碳化硅器件挑战现有封装技术

2022-03-03曹建武罗宁胜PierreDelatteEtienneVanzieleghemRupertBurbidge

曹建武,罗宁胜,Pierre Delatte,Etienne Vanzieleghem,Rupert Burbidge

(1.CISSOID中国代表处,广东深圳518118;2.CISSOID S.A.,Mont Saint Guibert,1435,Belgium;3.CISSOID S.A.,Tarbes,65000,France)

1 引言

碳化硅(SiC)器件的本质特性决定了其低内阻、高耐压、高频率和高结温等优异指标,在移动应用功率密度不断提升的压力之下,SiC器件对封装技术提出了全新的要求,也带来了全新的挑战。

在宽禁带(Wide Band Gap,WBG)半导体发展的早期阶段,SiC等器件的封装继承和沿用了现有的封装技术,这些技术主要是在硅基的绝缘栅双极晶体管(Insulated Gate Bipolar Transistor,IGBT)和金属氧化物半导体场效应晶体管(Metal Oxide Semiconductor Field Effect Transistor,MOSFET)等功率半导体的基础上发展而来的。过去功率半导体的表面金属化主要基于铝质材料,且一直都在渐进改良中,例如从铝基连接逐渐转向铜基或银基连接,包括邦定、焊接等。最新的发展尝试了各种铜烧结和银烧结,有时也称纳米银烧结或纳米银等技术,取得了优异的测试指标,特别是银烧结被认为是未来封装技术的主要发展方向之一。

为了充分发挥SiC等新型器件的优势,部分铜基同质连接和高压银烧结技术的研究已经获得了令人满意的性能。未来发展聚焦于低压或无压银烧结;铜烧结和银烧结都能提供极佳的导热性能和循环寿命,但铜烧结的工艺更为复杂,费时较多产出低效,且设备昂贵,制造成本偏高,因而低压或无压银烧结日益受到重视。部分工程师在连接的叠层微观构型等方面进行了探索,近年来出现多种嵌入式基板和无基板嵌入式封装等概念。也有一些工程师转向了某种非传统的异形封装架构,暂称之为离散型封装。此外,封装技术的高温化也是一个明显的发展趋势。

本文首先讨论了SiC器件的新特性和移动应用对功率密度的指标要求,以及这些特性和要求给封装技术带来的新压力和新挑战;在综述现有封装技术及其渐进改良的基础上,对铜基同质连接等特别是银烧结技术的发展状况进行了介绍;进而讨论了封装技术的叠层结构创新和离散化、高温化趋势;最后对封装技术的发展方向进行了综合评估。

2 现有技术及其面临的主要挑战

2.1 SiC功率器件的本质特性

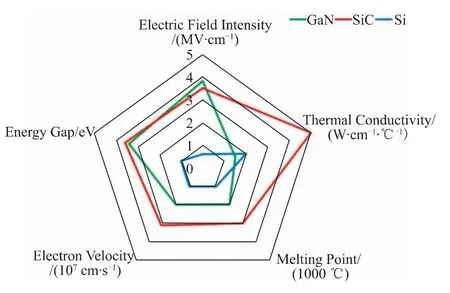

宽禁带半导体的本质特性主要表现在电场强度(Electric Field Intensity)、导 热 系 数(Thermal Conductivity)、熔点(Melting Point)、电子迁移速度(Electron Velocity)和禁带宽度(Energy Gap)5个方面,不同半导体材料的本质特性见图1。

图1 GaN、SiC和Si半导体材料的本质特性对比[1-3]

SiC的本质特性在多个方面都很优秀,其低导通内阻、高耐压、高开关频率和高耐受结温能力是这些本质特性的外在表现。SiC器件特别适合功率电子的移动应用,例如多电和全电飞机、电动船舶及新能源汽车等领域。在电动汽车的电力牵引驱动系统(Electric Traction Drive System,ETDS)应用上特别受重视,被视为IGBT等原有功率器件的换代技术。

2021年末标志性的SiC器件单芯片内阻已经低至13 mΩ(欧美)/17 mΩ(中国),正在挑战8~10 mΩ(欧美)/10~12 mΩ(中国)的量产目标。SiC半导体制造水平越来越高,芯片的内阻持续降低,从而为更高功率密度SiC模块的实现奠定了基础。为了配合高功率SiC模块的应用,CISSOID开发了相匹配的耐高温门级驱动方案,并推出了系列三相全桥SiC MOSFET智能功率模块(Intelligent Power Module,IPM),其中一款单臂6颗芯片并联时,额定内阻仅为2.53 mΩ,额定指标1200 V 550 ARMS/400 kW[4]。随着SiC芯片技术的进步,未来CISSOID有机会推出额定内阻2.00 mΩ的IPM,即保持现有模块的造型和尺寸不变,在理想的散热条件下,单个IPM的驱动功率将会高达1200 V 800 ARMS/600 kW,功率密度可再提高50%。

SiC器件的开关速度更高,开关损耗更低(大约为IGBT的1/3),因而可以适应更高的脉宽调制(Pulse Width Modulation,PWM)开关频率。过去基于IGBT、MOSFET器件构建的功率驱动电路开关频率多为6~10 kHz,一般不超过15 kHz。而基于SiC器件的同等功率实现,开关频率常常都在12~30 kHz(电机驱动)或50~100 kHz(电源逆变)。欧洲电力电子中心(European Center for Power Electronics,ECPE)探索项目在2015年已经实现了250 kHz的SiC开关频率[5];2021年有些面向电源类应用的SiC功率模块,PWM开关频率已经高达400 kHz[6],有些SiC门级驱动芯片的开关频率已经高达430 kHz[7]。针对高压大功率AC/DC或DC/DC应用,已有研究机构尝试在CISSOID的IPM上进行200 kHz开关频率的测试;针对电机拖动类应用,也有客户开始在CISSOID的IPM上尝试30~40 kHz的开关频率。

SiC器件耐压高、内阻小,芯片尺寸相对于IGBT可以做得很小。目前一颗额定指标为1200 V、150 A(约12 mΩ)的第四代IGBT芯片,面积约为140 mm2(11.31 mm×12.56 mm)[8];而一颗额定指标同为1200 V、150 A(13 mΩ)的SiC器件,面积仅为30 mm2(4.36 mm×7.26 mm)左右[9],后者面积较前者几乎减小至五分之一。

在高压大电流和高开关频率的应用中,大电流意味着导通损耗的增加;开关频率的提高也会带来开关损耗的增加;SiC芯片面积的显著缩小使得单位面积散热需求急剧增加[10-12]。在同等负载功率的情况下,兼顾结温、瞬态热阻、短路耐量等因素,SiC器件封装的单位体积导热能力需要提高3~7倍才能满足总体的散热要求,这对封装技术提出了前所未有的挑战。

2.2 来自移动应用的指标压力

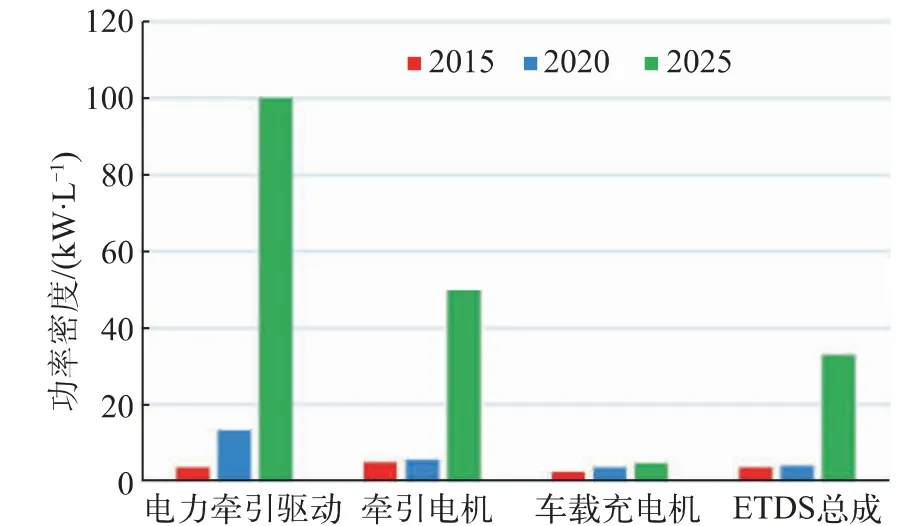

从2014年开始,美国能源部(Department of Energy,DoE)在DoE 2025序列资助了多个WBG基础研究项目,橡树岭国家实验室(Oak Ridge National Laboratory,ORNL)、麻 省 理 工 学 院(Massachusetts Institute of Technology,MIT)等学术机构及企业参与研发[13-15]。DoE还与其他单位一起资助了USDRIVE等新能源汽车探索,指向WBG器件的具体系统应用实现,其中对电动汽车类ETDS提出了苛刻的功率密度要求(见图2)。

图2 DoE 2025/USDRIVE的ETDS功率密度目标[13-15]

美国国家可再生能源实验室、伊利诺斯理工大学等研究机构及福特、通用等汽车企业参加了USDRIVE的挑战性研究项目[13-15]。主要难题在于ETDS的功率密度,相对于2020年的水平,USDRIVE要求2025年牵引电机及其驱动的功率密度分别提高到50 kW/L和100 kW/L,相对于2020年的探索实现(非工业实现),要求2025年分别提高8.8倍(机械)和7.5倍(电气);同时要求ETDS的成本下降到2025年的6$/kW[14],实现与内燃机驱动系统的可比性。

在环保要求更高的欧洲,业界也面临着类似压力。ECPE作为欧洲功率电子领域的代表性平台,依托本地多个大学、研究机构和企业,在基础材料、封装技术等多个层面做了大量的研究,均指向了各类创新性的高密度封装[19]。

2.3 现有封装技术面临的关键挑战

SiC器件对封装技术特别是高功率密度模块的封装提出了新的要求。这些要求包括但不限于:(1)为了耐受更高的结温,所有结合面的熔点要从200℃提高到400℃以上;(2)封装的总体散热能力提高3~7倍,以便在更小的体积下耐受相当的耗散功率;(3)连接的剪切力(die Shear)值要从30 MPa提高到60 MPa以上,从而可以耐受宽幅热冲击和热电联合功率循环,保证可靠性和寿命;(4)连接面的电阻值要小,以便耐受较高的电流;(5)要求更小的封装体积,有助于进一步提高功率密度并降低杂散电感,适应更高的开关频率[20-27]。

以ETDS为例,要实现8倍左右的功率目标值且散热能力还要提高3~7倍,业界必须从新兴材料、新型连接工艺和叠层构造形式等方向去寻找答案。

3 现有封装技术及其渐进改良

3.1 现有的封装技术

现有封装技术的核心可以归纳为焊接和邦定技术,笔者泛称为连接或结合。对于功率模块,与芯片(die/dice)直接相关的连接称为芯片近端连接,其他泛称为芯片远端连接。关于连接,多数文献混用为Attach、Contact、Connection或Join、Joining等,也有人用Bonding来泛指所有的连接(结合)。焊接是用于芯片底部与基板(Substrate)的连接(die Attach),或基板与散热底板的连接(系统连接)。焊接的主要方法有传统的SAC焊接(SnAgCu Soldering),近年发展出了各种钎焊(Brazing)和扩散焊等。邦定(Bonding)是用于芯片顶部到基板或基板到模块外框引线的连接,材质常用金银铜铝,型制有线形或带状,方法有超声或热压等。过去功率芯片的表面金属化材料通常是Al或Al掺杂少量Si、Cu,经过焊接与基板表面(通常是Cu)形成的金属间化合物构成die Attach的结合层。基板两面的金属常为Cu,通过焊接与散热底板连接,散热底板的材质通常为铝碳化硅(AlSiC)或表面镀Ni的Cu。

这些连接器件的性能在早期IGBT中可以满足多数应用的要求,近年来则日益落后于半导体技术的发展,主要表现在两个方面:(1)由于半导体芯片单位面积电流密度的提高,原有连接的导热能力严重不足;(2)由于半导体芯片最高耐受结温的提高,芯片近端和远端连接在宽幅度热冲击或热电联合功率循环测试中劣化太快,寿命不足。各类连接的熔点、导热能力取决于表面材料及形成结合的工艺过程,连接的剪切力取决于表面材料及结合层的热膨胀系数(Coefficient of Thermal Expansion,CTE)。SiC基础材料的CTE为(4.3~5.4)×10-6/℃,金银铜铝的CTE依次为14×10-6/℃、20×10-6/℃、18×10-6/℃、23×10-6/℃[2,27-28],金银铜的CTE更接近半导体,且刚度较低,拉伸延展性更好,商业中应用的封装技术主要使用银和铜。

3.2 基础材料和工艺的发展

至今为止,绝大多数基板的表面金属都是铜,外框引线端子也多为铜(有时镀镍等)。功率模块常用的是直接覆铜陶瓷基板(Direct Copper Bonding,DCB,或Direct Bond Copper,DBC)、氮化铝有源金属钎焊覆铜陶瓷基板(AlN Active Metal Brazing,AMB),还有掺杂了二氧化锆(ZrO2)增韧的Al2O3陶瓷基板等,基板与散热底板的连接(系统连接)泛称为DCB Attach,它们的表面金属化材料都是铜。近年来在USDRIVE项目的支持下,ORNL等开发了嵌入石墨(Graphite Embedded)的陶瓷基板,额定热阻下降17%,瞬态热阻降低40%,电流能力提高10%[14],其表面金属还是铜。

在DCB Attach工艺中,AlSiC散热底板的CTE为(7~9)×10-6/℃,热电联合功率循环周次是铜质散热底板的10倍,但其导热能力只有铜质散热底板的30%,寿命虽长但散热效果较差,因而近期的很多研究回归到铜散热底板。过去功率器件的表面金属多为铝,芯片顶部的粗线邦定多用铝线(也有些网状编织铜带的尝试)。近年来芯片近端连接的发展方向主要是用铜替代铝,与铝相比,铜的导热性能约高80%,电流能力约高37%[24];铜的CTE较低且更为柔软,延展性强,因而在解决了DCB Attach的寿命问题之后,铜基同质连接的热冲击和热电联合循环测试周次可以比传统的铜铝连接高6~15倍[27-28]。铜基同质连接工艺普适性强,除了用于传统的邦定和焊接外,还用于铜夹封装(Copper Clip Package,CCPAK)和印刷电路板(Printed Circuit Board,PCB)的各种厚铜工艺及焊接、烧结等。铜与半导体材料表面的结合有铝质金属化镀铜、铜质烧结缓冲层邦定、二次烧结等[10,19,24,26]。

然而裸露的铜很容易被氧化;铜与硅、SiC等半导体材料结合的附着力也偏弱;铜基连接工艺过程繁琐费时,量产产量低,制造设备昂贵。另外,功率器件的连接需要具备较大的电流能力,因而常用粗壮的线型或带状邦定材料,这样又会导致在热胀冷缩时产生较大的机械应力,容易损坏芯片、降低寿命。近期关于铜基同质连接的研究都是围绕着相关材料的改良(例如在铜料掺杂其他形成合金及焊料成分改善)和制造工艺(焊接方法等)展开的[10,23-24,26,29]。

连接的工艺实现和基础材料的开发是同步改良的。例如,传统锡银铜焊接的CTE约为30×10-6/℃,剪切力为20~30 MPa,导热系数为30~58 W/(cm·℃)[2,29],因而在连接工艺方面出现了固液相互扩散和瞬时液相烧结/焊接等工艺,与之配合研发了特制的焊料,新型焊接工艺的主要连接指标均有一定的改善[30-32]。此外,大量研究表明,在一定压力下进行的铜烧结和银烧结的剪切力是焊接的3~5倍,热导率为3~9倍,电阻率仅为焊接的1/6左右,各方面都有相当大的进步。

作为连接和结合辅料的粘性导电环氧树脂或掺杂微米银聚合物近年来也获得了极大的进步,过去老式的环氧树脂导热能力只有1~7 W/mK,现在已经提高到20~100 W/mK[2,29,33];除导热外,这些辅料还可以帮助减小连接电阻,减缓热胀冷缩带来的机械应力等[33];与之类似,作为模块封装填料的绝缘导热有机硅胶、热固性树脂等材料的导热能力也提高了。最后,外壳模料的发展对于封装的整体散热也有贡献。这些辅料的选择和工艺过程对封装整体性能也有重要影响[10,33-38]。

3.3 铜基同质连接的研究

很多学术机构和企业参加了铜基同质连接的研究,例如欧洲弗里德里希亚历山大大学等研究了重型铜线邦定,卡尔斯鲁厄理工学院研究了粗铜线与厚膜铜基板的邦定;有些企业开发了激光邦定技术来提高铜铜结合的连接强度,还有些企业开发了铝硅包裹铜带用于功率邦定;有些企业开发了铝基金属化芯片表面双面镀铜的工艺来支持铜基同质连接;多个企业开发了用于重铜邦定的PCB基板和焊膏以及操作工艺,可用于die Attach、邦定、扩散焊和铜烧结。部分工艺设备制造企业在这些研究的基础上进行局部创新,推出了兼容银烧结和重铜邦定的制造设备[19]。

NAKAKO等人在PCIM 2018(Conference of Power Convention and Intelligent Motion,PCIM)报告了铜烧结循环寿命的研究[39]。他们使用了3种不同的铜浆料,环境气体配置有氢气、氮气和甲酸,设置225~300℃的不同温度等级,在铜、DCB或AMB基材上进行了烧结试验,试验表明铜烧结可以用于49~169 mm2的芯片。该研究还使用了25 mm2的硅基芯片分别进行铜烧结(无压,300℃)、银烧结(20 MPa,300℃)、高铅焊接,然后进行了-40~+200℃的宽幅热冲击测试对比。在5000次循环之后,三种连接都出现了某种程度的劣化,铜烧结的边缘出现了细微的裂缝,银烧结的边缘则出现了较大的裂缝,但二者的中间位置几乎没有劣化;高铅焊接的边缘和中间均出现了明显的裂缝。该试验还进行了5 MPa、10 MPa等不同压力条件组合的测试,获得了60~80 MPa的剪切力。

NAGAO等人在PCIM 2018报告了高结温半导体铜烧结研究的情况[40]。他们使用一种新型的铜浆料(来源未披露),在300℃和氮气中,用1 MPa的低压对Si(3 mm×3 mm)和SiC(3 mm×4.4 mm)芯片进行铜烧结,获得的剪切力均值分别为32.7 MPa(Si)和17.2 MPa(SiC),报告认为这个结果好于传统的高温Pb20Sn焊接(一种高铅的铅锡焊料)。

WANG 和 LU 在 CIPS 2020(International Conference on Integrated Power Electronics Systems)联合 做 了 题 为 《Sintered Copper die Attach:Process,Properties,and Reliability》[41]的研究报告。研究者使用微米级的低成本市售铜膏,用铜烧结进行了die Attach测试。该测试使用了3 mm×3 mm、5 mm×5 mm的IGBT芯 片、DCB、AlN AMB基 板,在0~5 MPa、230~300℃等条件组合下进行烧结操作。测试表明,在5 MPa、270~300℃,不同基板上进行30 min的铜烧结,芯片的剪切力最高可达65 MPa。在经过2000次的-55~125℃热冲击循环(参照JESD22-A106B.01测试标准)之后,剩余剪切力也还有58 MPa。考虑到目前各类焊接工艺的die Attach剪切力都在20~30 MPa左右,该报告的结果是相当积极的。

3.4 封装技术的现状

某些基于第五代IGBT芯片的功率模块封装技术是渐进改良的典型案例,反映了封装技术的现状[30-31]。该技术集合了封装技术的经典方法和渐进改良成果,其中部分也尝试了铜烧结和银烧结等工艺,主要包括:

1)芯片顶部连接,核心是铜铜(Cu-Cu)邦定,通过对芯片顶部进行铜质金属化(基板表面也为铜),邦定线由铝线改为铜线,获得了最佳的表面同质结合及CTE匹配,改善了连接寿命和芯片表面的散热状况;

2)芯片底部连接,依据底部金属化的不同,分别采用铜锡(Cu-Sn)或镍锡(Ni-Sn)混合焊料进行扩散焊(不同配比试验,有时也掺入了纳米银粉),在结合面产生了5μm以上的金属化合物层,测试表明对面积高达185 mm2的IGBT芯片都可以有效操作,该封装技术也尝试了高压银烧结来进行die Attach(压力5~30MPa);

3)系统连接,DCB Attach等,通过调节焊料中的锡银铜比例,并调节工艺过程(温度曲线),实现了高效改进型焊接,获得最佳的结合面弹性模量。

由此,该组合式渐进改良的封装技术获得了性能的综合性改善:首先,该技术将各个连接的熔点都提高到了400℃以上,可以支持200℃以上的最高工作结温,可用于SiC模块的封装;其次,使用该技术的功率模块在各种寿命测试中表现优异,在热冲击和热电联合功率循环(类似于AQG 324的PCSEC[42])测试中表现优异,经过200万次循环后芯片顶部邦定几乎没有劣化,底部焊接则仅因DCB铜皮劣化而受到影响[30];模块总体热阻显著降低,导热性能提高15%左右。该封装技术是一个显著进步,但对于SiC器件要求的3~7倍的散热能力还是不足的。

其他厂家也开发了主要基于铜基同质连接的不同工艺,具体实现各有特色。例如直接端子键合把铜质引线端子直接键合到芯片顶部[19],芯片顶部系统混用了铜烧结和铜铜邦定[19],与DTS概念接近的邦定缓冲层(Bonding Buffering)技术揭示了铜基同质连接的核心要点:通过在芯片表面生成大约50μm的缓冲层,解决了铜与半导体表面结合强度不足的问题,且导电和导热能力优异,有报道说该技术实现的芯片顶部连接,电流耐受能力提高至原有工业标准的15倍[22-25]。还有一些企业转向了银铜三维多层烧结的无邦定连接,目前细节没有得到足够的披露,但是厂家宣称其电流能力、导热能力和热循环周次均得以提高10倍[19]。国内的领先企业也开发了类似的先进混合封装技术,取得了优异的测试结果,部分已在产品上批量应用[27]。

由此可见,目前功率器件封装技术的核心工艺已从铝基转向铜基,在前期研究和实际产品应用上都取得了显著进展,除了基于原有技术的邦定和焊接等连接型式,铜烧结也有不小的进步。但从导电导热性能、剪切力、熔点等指标来看,这些渐进改良的效果还不够,因而近年来业界的前沿研究大都转向了银烧结。

4 银烧结技术

4.1 银烧结技术的背景

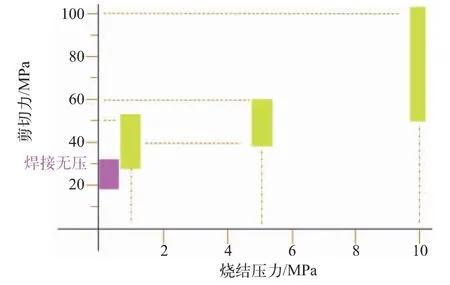

银是目前唯一一种在200℃下有自动还原的去氧化自洁功能的金属材料,对于银银(Ag-Ag)、金银(Au-Ag)或银铜(Ag-Cu)界面,银烧结后形成的结合面非常稳定,工艺实现相对简单,生产速度更快。从现有的研究成果来看,银烧结形成的结合面同时具备高电导、高热导、高可靠性、高剪切力等特点,因而已被视为封装技术未来的核心发展方向之一。卡尔斯鲁厄理工学院的研究报告[50]指出,die Attach银烧结之后的结合面熔点分别为961℃(银)和1085℃(铜),足以耐受高达225℃的工作温度,银烧结的导热能力是传统焊接的5~7倍,融合界面更为柔软,具有更大的剪切力值,银烧结压力与die Attach剪切力的大致关系参见图3,因而其热电联合功率循环寿命是传统焊接的10倍。总而言之,仅就热力学性能而言,银烧结正好可以满足SiC器件对封装技术所要求的3~7倍的散热能力[27,35,43-47]。

图3 银烧结压力与die Attach剪切力的大致关系[20,28,32,43-47]

目前国内模块封装常用的钎焊焊料为锡银铜焊料组合(SnAgCu,SAC),其熔点仅有220℃左右,而现在多数SiC器件的最高额定结温都是175℃,很快就会普及到200℃,因而要求芯片底部连接结合面的熔点要达到300℃,最好超过400℃。由于银烧结形成的结合面更为柔软,在芯片底部连接时,高温高压银烧结的热冲击测试或热电联合功率循环周次,可以达到传统钎焊的10倍或以上[24,27]。不仅如此,银烧结连接在电气和热力学性能上也非常理想,大致而言,其烧结面的电阻率可以降低至8×10-6Ω·cm2[8],热导率提高到150~300 W/(m·K),导热性能是传统焊接的3~10倍[2,27,35]。图3中给出的数值是一个大致的数量级描述。银烧结相关的研究和实践还处于早期阶段,尚未有一个公认的、规范化的测试规程,所以不同研究的测定条件是有差异的,报道的测试数值也各不相同。

银烧结的优异性能吸引了大量的研究者涉足其间,但其并非新生事物。早在1970—1983年,银烧结就被用于金属和陶瓷之间的键合,同期也有一些铜烧结、金烧结的研究,还有使用铁和陶瓷(Al2O3)在100 MPa~1 GMPa压力下进行烧结的报道。1990年前后,德国开始使用微米级的银粉膏料来进行高压烧结,2000年前后,纳米级的金粉和银粉(纳米银)也开始被用于各种试验。这些实验表明在适当的压力条件下,各种烧结都能实现极佳的连接强度和导电导热性能,近期中高压银烧结也开始进入量产应用;近年来更多的试验表明,较为便宜的亚微米到微米级的混合银粉浆料可以在较低温度(220℃左右)进行有效的烧结(配合以各种辅料、制造工艺),但还是需要足够的压力才能保证剪切力、导通电阻及导热能力等指标满足应用的需要[20]。目前已有一些报道展示了低压甚至无压银烧结试验的测试情况,效果暂时还不够理想,有待进一步探索。

欧洲很多研究机构介入了银烧结相关的探索。在德国佛劳恩霍夫研究促进协会(Fraunhofer)体系中,材料和系统所(Fraunhofer Institute for Microstructure of Materials and Systems,IMWS)长期致力于广域的半导体封装基础研究并开发了对应的CAM(Computer Aided Manufacturing)系统;可靠性和微集成所(Fraunhofer Institute for Reliability and Microintegration,IZM)同时在进行大面积银烧结和扩散焊的研究和验证;硅技术所(Fraunhofer Institute for Silicon Technology,ISIT)也从事封装技术和可靠性研究,并与美国元件企业VISHAY一起建立了研究型试生产线;法国IMS(Laboratoire de l'Intégration du Matériau au Système)开放平台进行了3D组装相关的低压银烧结研究,法国PRIMES(Plateforme d'Innovation Mécatronique de Puissance et Management de l'énergie)开放平台则进行了模块结构创新方面的开 发。University of Breme、Chemnitz University of Technology、Delft University of Technology等高校也都参与了各种铜烧结、银烧结研究。欧洲其他国家的研究机构相对分散,大都依托于ECPE与德法的对口单位合作[19]。

2014年SIOW在期刊ElectronicMaterials[44]、2018年LIU等人在Micromachines[45]汇总了银烧结的总体情况,两个报道均可作为近年来银烧结技术发展的索引。在PCIM 2018,TAKESUE等报道了无压银烧结在机械和可靠性方面的测试情况[48],OTTO等人报道了在引线框架上进行银烧结和扩散焊的对比研究[32],DRESEL等人报道了在高温PCB上进行银烧结的研究情况[49];在CIPS 2020,SUGANUMA报告了有压银烧结及铜烧结的测试情况[20],SUBBIAH等人(佛莱堡大学)报道了在若干非DCB基板进行银烧结的试验[46],而BLANK等人(卡尔斯鲁厄理工学院)则对无压银烧结进行了总结[50];2021年CALABRETTA等人在AppliedScience报道了银烧结工艺优化和建模的研究成果[47]。这些研究报道反映了近年来银烧结技术的前沿发展,以下笔者对相关研究作一些详细介绍。

4.2 银烧结技术的相关研究

4.2.1 大阪大学的研究

大阪大学SUGANUMA在CIPS 2020报告了《WBG Power Semiconductor Packaging with Advanced Interconnection Technologies》[20],作为CIPS 2020的特邀报告,论文详细说明了银烧结结合面的形成机制:柔软的合金融合介面(见图4)。报告总结了银烧结技术的历史和现状,给出细节数据,团队用相对便宜的微米和亚微米混合颗粒银膏在200℃低温下进行die Attach,获得优异的电气和热传导性能。报告指出,在180℃进行10 min的无压银烧结可在DCB上形成剪切力值约为30~40 MPa的结合,结合面的电阻值、热导率等关键指标也很理想;用GaN芯片在镀镍的陶瓷覆铝(Direct Bonding Aluminum,DBA)基板上进行银烧结,在-40~250℃区间进行500次热冲击试验后,残余剪切力几乎没有变化(保持在约33 MPa的水平)。

对于用银料溅射形成的GaN芯片金属表面,在250℃与微米银膏烧结后的银珠分布非常均匀,可以有效结合两个表面;对于Au-Ag烧结,过去低压烧结的效果不良困扰了业界多年,近年已被研究清楚,空气环境、无压、180℃、10 min烧结的结合面细节见图4。另外,作者也曾经做过数年的铜烧结研究,在250~300℃的氮气环境中,用0.4 MPa的压力进行的铜烧结也可获得30~40 MPa的die Attach剪切力数据。

图4 银烧结界面的融合情况:金银界面(Au-Ag)的融合[20]

大阪大学的报告指出,传统焊接技术已不能满足WBG器件对导热能力及热电联合循环寿命的苛刻要求,高压银烧结目前虽然还比较昂贵,但是已经开始了商业化应用进程。由于烧结的结合面是融合性的,与焊接结合面的刚性相比要柔软很多,因为能够更好地消化热胀冷缩的机械应力,所以获得了极为理想的可靠性和寿命。

4.2.2 佛莱堡大学的研究

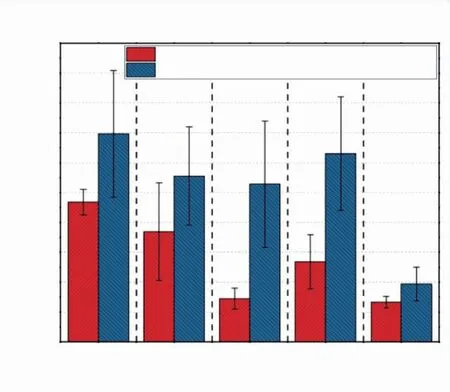

佛莱堡大学SUBBIAH等人在CIPS 2020报告了《Comparison of Silver Sintered Assemblies on Non-DCB Substrates》[46],对3种非DCB基板(IS550H高温PCB、隔离金属基板和铜质引线框架)进行了银烧结测试,测试使用了2 mm×2 mm的小型芯片及市售银膏(LTS 338-28[37]),在230℃、10~20 MPa压力下进行,初始和剩余剪切力见图5。

图5 在PCB上进行银烧结的初始和剩余剪切力[46]

该研究指出,用银烧结技术把功率芯片等直接连接到高温PCB上是可行的。仅从剪切力的数据来看,这个试验并不完美,因为在高压银烧结(最高20 MPa)时获得的最佳剪切力初值只有35 MPa,低于3.3节天津大学的中压5 MPa铜烧结数据[41],所以笔者认为这个试验还需要进一步的尝试,例如参考4.2.3节卡尔斯鲁厄理工学院(Karlsruhe Institute of Technology,KIT)的测试,使用不同的芯片底部金属化层及PCB的表面处理来进行比对。不过该试验偏向离散式封装(参见5.2节),报告提及了在PCB上可以集成更多的离散元件并通过铜质过孔互联等,并称该PCB基材可以在200℃高温环境下长期可靠地工作,因而该研究也有其独特的意义。

4.2.3卡尔斯鲁厄理工学院和日立化学的研究

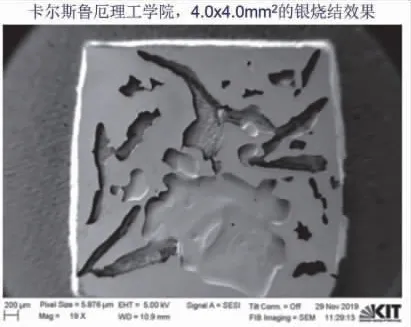

卡尔斯鲁厄理工学院BLANK等人和日立化学ISHIKAWA在CIPS 2020联合发表了《Is Pressureless Sintering Ready for Power Electronic Modules?》报告[50],报道了无压纳米银及纳米铜die Attach烧结的测试情况。测试使用3种不同尺寸的die,分别为2.3 mm×2.3 mm、3.2 mm×1.6 mm、4.0 mm×4.0 mm,较小的2款芯片获得成功,第3个较大的芯片遇到问题,烧结后呈现大量的空洞区(见图6)。

图6 4.0 mm×4.0 mm的die Attach,显示了大量的空洞区[50]

研究者使用了100 nm的纳米铜膏、20 nm的纳米银膏等材料,在275℃进行了无压烧结对比试验,银烧结测试的衬底使用了常规的DCB基板及化学镀镍沉金(Electroless Nickel Immersion Gold,ENIG)和化学镀镍镀钯及沉金(Electroless Nickel Electroless Palladium Immersion Gold,ENEPIG)这2种PCB基材,铜烧结测试则使用了DCB基板及铜质引线框架。

2.3 mm×2.3 mm的die使用了纯银进行底部金属化,3.2 mm×1.6 mm使用了厚膜银钯合金(Thick Film Silver Palladium,AgPd),而4.0 mm×4.0 mm的die底部表面为镍钯铜合金,并在烧结前进行了表面预处理。此外,测试还使用了80μm和120μm两种银膏(铜膏)印刷厚度进行了烧结试验,具体烧结时间曲线的配置也有调整和变化。试验表明,对2.3 mm×2.3 mm的芯片,纳米银烧结在ENIG和ENEPIG产生的剪切力均值分别为82 MPa和100 MPa,较为理想;3.2 mm×1.6 mm(AgPd底部)的芯片,在ENIG上的剪切力均值为70 MPa,但在DCB上表现不佳,不超过30 MPa;至于铜烧结,这两个小型芯片在一定的工艺条件下获得的最好结果是在铜质引线框架上,剪切力均值为65 MPa,与天津大学的测试结果一致[41]。4.0 mm×4.0 mm芯片的银烧结试验没有获得成功,空洞面积太大(图6),报告者认为该芯片面积较大,在进行无压银烧结时焊膏挥发存在一定困难,还需要继续研究。

4.2.4 卡塔尼亚大学的研究

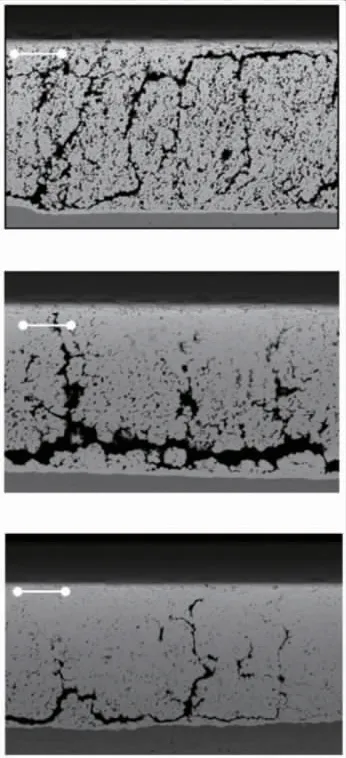

CALABRETTA等人在卡塔尼亚大学及合作企业研究了SiC芯片银烧结工艺优化并建模,在Applied Sciences发表《Silver Sintering for Silicon Carbide Die Attach:Process Optimization and Structural Modeling》[47],报告了使用BOSCHMAN的市售设备在AMB基板上进行SiC芯片银烧结的详细过程。该文还报告了10~30 MPa的有压银烧结最佳压力值的测定方法,并结合3000次宽幅热冲击试验(-65~+150℃)的中间和最终测试数据,劣化情况见图7。

图7 不同压力下的银烧结融合界面在3000次宽幅热冲击后的劣化情况(10 MPa≤P1<P2<P3≤30 MPa)[47]

他们还基于中间测试结果等数据,对银烧结的材料(颗粒)、压力、温度等之间的关系进行了研究,尝试了用有限元方法对结合面进行分析,并通过烧结粘附特性和相关断裂形式进行了内聚区建模。

4.3 银烧结技术的材料、工艺和设备

银烧结的两个表面,芯片底部金属化层和基板、散热底板表面的金属化层的材质也得到了广泛的研究。例如,因戈尔施塔特技术应用大学等研究了银浆料与改性铜合金之间的连接;弗劳恩霍夫集成系统和设备技术研究所(Fraunhofer Institute for Integrated Systems and Device Technology,IISB)则研究了银银直接键合的效果;阿莎芬堡应用技术大学研发了Micro Copper Sinter材料;F&K、DODUCO等企业也致力于界面友好的镀层材料研究并应用于产品设计[19]。

在企业界,领先的基础材料公司HERAEUS、日立化学等开发了适用于银烧结的各种浆料[28-29,50],目前市场上已有十余家银烧结浆料的商业供应。以颗粒度论,有纳米、亚微米和微米级别;以烧结压力论,有高压银膏、低压银膏、无压银膏;市面也有金浆料、铜膏料的供应。已有一些中国厂家涉足了银烧结材料,并与国内大学一起进行了对比验证。

在不同压力、温度(曲线)和环境(气体)条件下,对不同芯片、基板的表面材质进行银烧结时,其功效有所不同,这方面的研究也很广泛。银烧结工艺研究的参与者有前述的Fraunhofer研究协会体系IZM、IMWS、ISIT等多个研究所,大学则有University of Applied Science Kempten、University of Breme、Ferdinand Braun Institut Berlin、卡尔斯鲁厄理工学院等。基尔联合应用大学(University of Applied Sciences Kiel,UASK)进行了低温银烧结工艺生产线的开发;IMWS和UASK还进行了基于银烧结的高密度高温微组装研究,具体有厚铜PCB制造工艺、带有嵌入式元件的混合PCBA(Printed Circuit Board Assembly)等。参与工艺研究的企业则有HERAEUS、F&K、HESSE和DODUCO等,在测试验证和建模方面,前述多个大学、研究机构及企业,与MENTOR等热力学和电气模拟软件厂家合作,同步开展了各种新型工艺的建模及验证[19]。

焊接设备厂商PINK、BOSCHMAN和ASM等开发了从实验室应用到量产车间使用的自动化银烧结设备,ZESTRON开发了用于银烧结前后进行清洗处理的生产设备。银烧结技术目前还在发展中,现有的工艺和设备既是对前期研究成果的阶段性总结,又是后段持续演进的起点[19]。

4.4 银烧结技术总结

如前所述,纳米或微米级的银粉颗粒材料是一种优异的封装材料,银烧结形成的结合面同时具备理想的导电和导热性能。就工艺过程而言,主要特征表现在两点:(1)银是目前唯一可见的当温度在200℃以上时表面氧化层可以自洁并恢复到纯银状态的金属材料,而近年绝大多数银烧结工艺是在250℃左右进行的,因而可以省略很多烧结前的预处理过程;(2)银烧结的结合面是融合的,在烧结面形成了柔软的合金层,可以耐受更大周次的热电联合功率循环,因而可靠性更高,寿命更长。当然,纯粹的银粉无法直接进行烧结操作,通常以银膏或银浆形式出现,混合有某种化合物或聚合物。除了银粉本身的纯度,银粉在介质中的分布均匀度、介质在烧结后的残留状况也都存在工艺问题;有些研究使用了金粉或铜粉(金膏或铜膏)来代替银膏进行烧结试验[20,41]。

银烧结目前的研究涉及到die Attach、DCB Attach等,效果取决于被烧结的两个界面的材料及具体银浆料的特征,还有环境气体、温度曲线(升温、停留时间、降温等)、压力等要素。银烧结的具体方法有热压、原位成型、火花等离子、激光烧结、电流烧结等[45]。从现有的研究报道来看,在一定压力下进行的各种银烧结都可以获得理想的剪切力值,银烧结的压力越大、温度越高,高温持续时间越长,烧结的效果越好。但是高温高压烧结的制造成本偏高,长时间烧结的产能偏低,而且烧结压力太高可能对芯片本身带来潜在的机械损害,进而影响到热冲击或热电联合循环的寿命周次[33,45,48]。

当然目前可见的研究报道,使用的芯片面积都还较小,面积更大芯片(或DCB)的烧结报道较少,具体工艺条件和过程还需要进一步研究和验证。die Attach或DCB Attach的低压或无压银烧结试验都还在发展中,多数研究是在200~300℃的温度范围内进行的,而这正是大多数普通的表面安装技术(Surface Mount Technology,SMT)回流焊炉(Reflow Oven)的工作区间。因此,如果未来无压银烧结或低压银烧结技术可以取得理想的进展,就意味着其制造效率可以显著提升,制造成本将会大大降低,进入商业化量产应用的门槛就非常低了。笔者认为,未来银烧结的技术突破将主要集中在以下几个方向:(1)低温低压银烧结材料的研究;(2)较大面积芯片的银烧结工艺研究、中间介质的清除等;(3)在前二者基础上发展出来的全自动化银烧结制造设备。

5 封装技术的其他发展

5.1 演进中的模块叠层构型

基板是功率模块的芯片载体之一。常见的基板与芯片、散热底板的连接模式在IGBT时代就已经成为了一种定式。近年来在基板的叠层构型方面也出现了新的趋势,为了提高组装密度,研究人员开始使用双面散热结构,过去单一的芯片底部散热带走了大约60%的内耗,但是在芯片顶部的浅近层面,还有40%的热量未能及时排出,导致芯片结温偏高。在SiC器件中,导通电阻伴随结温升高而增加,其短路耐量只有IGBT的一半左右,约为2.5μs左右[3-4],因而节温更容易快速越限。所以改善现有各个结合面的热阻,或同时减少结合面的数目,也是业界努力的主要方向之一。近年来出现的嵌入式基板概念把芯片及基板都埋入某种载体中,芯片和嵌入基板都使用了双面银烧结进行连接,由此来实现双面散热,嵌入式基板、双面空冷散热的剖面构造见图8。更为激进的无基板封装概念则取消了嵌入基板,芯片通过载体的金属化层直接连接到散热体上[42]。图中的顶部和底部嵌入基板与散热器的结合面都使用了热界面材料,可改善导热并减缓机械应力。

图8 嵌入式基板、双面空冷散热的剖面构造[42]

图8中还出现了Spacer/Spacer Attach的概念。Spacer为芯片顶部烧结连接的一个铜质中间件[2,26,42],通过邦定或二次烧结与其他层面进行连接(Spacer Attach)。与低压和无压银烧结的情况类似,这些嵌入叠层结构还处于发展早期,各个报道的细节披露尚不充分。

5.2 模块封装的离散化趋势

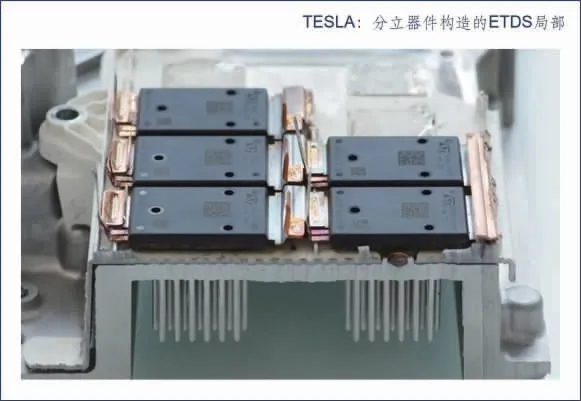

为了减小ETDS的体积和重量,部分工程师转向了接近于组装概念的各种3D综合集成。各种形式的发展分别肇始于混合厚膜电路、微组装或多芯片封装等传统高密度工艺,或这些工艺的混合运用,现在也有一些其他创新的微观构造型式。过去的ETDS常用IGBT模块来构建,而电动车企TESLA几年前就用SiC分立器件实现了全SiC版的ETDS,通过将电气驱动与电机机体进行某种程度的融合,显著提高了ETDS的性价比。图9展示了TESLA的实际产品设计:非典型模块和散热器的剖面构造[12]。

图9 非典型模块:分立器件构造的ETDS局部[12]

近年来更多研究机构和企业介入了这种离散化的研究。卡尔斯鲁厄理工学院在进行激光加工及银烧结等混合制造工艺研究的同时,还尝试用铜烧结把门级驱动直接结合到功率模块中去;瑞典的零部件供应商与车企VOLVO一起进行了高密度混合封装的设计研究;University of Applied Sciences Kiel进行了封装与模组设计一体化的尝试。多个商业公司开发了p2Pack(die Embedded PCB Package)、ECP(Embedded Component Package)、OCM (Open Constructure Module)等多种离散型的封装架构,有些架构允许在PCB表面安装控制系统零件,而在PCB内层嵌入了引线框架,其间的空腔用以容纳功率器件、门级驱动及其他分立元器件等[19]。

5.3 封装的高温化趋势

为了获得系统设计所要求的更高功率密度,今天很多工程师不得不把更多的元器件塞入到极为狭小的空间中,造成了单位体积中需要排出热量的急剧增加,进而要求封装技术显著提高导热散热能力。另外,为了适应较高环境温度的应用场景,例如没有液冷条件的移动功率应用,半导体器件本身就要面对更高结温的工作条件。因此,除了设法提高导热散热能力,功率器件及其驱动器件的封装不可避免地走向了高温化。知名技术市场趋势研究公司YOLE早在2012年就明确指出,多年来功率电子器件的结温一直在持续提高[33],YOLE对功率器件结温的预测见图10。

从图10可以看出,从1980年到2015年,硅基功率半导体的最高结温从100℃提高到了150℃;然后由于WBG半导体的出现,自2015年起,结温的上升趋势进一步加速并分化为2个分支走向。现在SiC器件的结温普遍到了175℃,到2025年将会普及到200℃,而到2030年则会提高到225℃左右[33]。SiC器件本身的最高耐受节温可以轻易超越500℃,目前常见的SiC器件标称结温175℃(少数标称200℃)是由于现有封装技术的限制所致。

图10 2012年YOLE对功率器件结温的预测[33]

有许多面向未来的应用已推动功率半导体最高结温的上升。如2019年ORNL在项目报告中把门级驱动的工作环境温度提升到150℃作为一项挑战,原因是为了进一步提高功率密度,ORNL正在尝试把逆变器集成到电机端盖或者电机筒体上[13,16-18]。欧洲中小功率的电动助力转向已经实现了完全的机电融合,为了减小尺寸和重量,柏林技术大学、卡尔斯鲁厄理工学院、ZF公司、YASA公司等都在努力把ETDS融合到牵引电机上去[19],所有类似的努力都导致电力牵引驱动越来越靠近作为热源的电机,而且电机的轴温也伴随着转速在持续提高,因此不仅需要功率器件提高最高耐受结温,也需要与之匹配的高温门级驱动方案。

针对结温持续上升的应用需求并配合SiC器件的普及,CISSOID公司推出了耐高温的SiC门级驱动芯片和方案(CMT系列175℃结温,CHT系列225℃结温)。CISSOID长期从事高温半导体器件的设计制造,其核心技术包括两个主要方面:第一,高温芯片技术,基于耐高温的芯片结构设计及先进的绝缘体上硅(Silicon on Insulator,SoI)制造工艺;其二,高温封装技术,其金属陶瓷封装的高温器件系列最高耐受结温可达225℃以上[33]。且与绝大多数硅基器件约1000 h的高温寿命不同,CISSOID的高温器件可在175℃结温条件下长期稳定连续运行达15年之久。SiC等半导体的高功率密度和高温应用越来越受到重视,这些应用的领域包括但不限于航空应用、电动汽车动力总成深度集成、移动储能等,将会给整个功率电子产业带来深刻影响,并推动封装技术的持续进步。

6 结论

为了应对SiC等新型功率半导体带来的挑战,封装技术的发展路线是多径的。封装技术的发展是一个综合的系统工程,牵涉到基础材料、构型设计、制造工艺及制造装备,还有测试、验证及建模等细分领域,有些是基于现有技术和工艺的渐进改良,有些则是另辟蹊径的超越创新,很多研究工作在细分专业的边缘展开。封装技术的发展为充分发挥SiC等新型半导体的性能优势奠定了基础。

业界正从基础材料、连接工艺、构造形式等方面展开探索。渐进改良的、混合型的铜基同质连接等基本满足了目前的需求;要充分发挥SiC等WBG器件的性能优势,封装技术的前沿研究正在寻求革命性的发展。鉴于银烧结界面极为优异的导电导热能力、剪切力及宽幅度热冲击和功率循环周次能力,今天多数的研究指向了银烧结技术,特别是低压和无压银烧结的材料和工艺。

模块封装的叠层结构创新以及封装的离散化、高温化也是新型封装技术的发展方向,决定了SiC等器件高功率密度和高温应用的实现。单一层面的技术改良难以满足日趋苛刻的应用要求,对于SiC器件而言,封装技术的未来发展方向在于银烧结工艺、新型叠层结构,以及离散化、高温化等方面的深度融合。未来5~10年,作为核心连接技术的银烧结将会得到充分的发展,其性价比也会逐渐为各种主流应用所接受。