一种LED显示驱动芯片倍频OS-PWM算法

2022-02-17王震宇王雪原唐茂洁范学仕

王震宇,王雪原,唐茂洁,范学仕

(中科芯集成电路有限公司,江苏无锡 214072)

1 引言

随着LED显示驱动技术的更新换代,小间距LED显示驱动正逐步成为主流技术,在显示屏、穿戴设备、照明设备及其他电子设备中得到广泛应用[1]。2019 年全球LED 市场突破500 亿,近5 年复合增长率达到15%以上,小点间距LED显示屏具有无缝拼接、模块化维护、显示均匀性好、色彩自然真实、画面清晰等优点,逐渐成为研究热点[2]。多路恒流LED 驱动芯片具有高密度、高清晰度、宽角度、高亮度、高刷新率、高对比度、智能控制、节能环保等多种技术优势,在小点间距LED 驱动芯片中得到广泛应用[3-4]。

在小间距LED显示屏中,多路恒流LED 驱动芯片采用传统脉冲调制(Pulse with Modulation,PWM)控制方式控制LED 灯亮/暗时间,达到不同灰阶亮度的显示效果。当所显示的灰阶亮度较低、连续不发光的时间较长时,会出现因刷新率低、灰度等级不高而造成的闪烁现象[5]。郑扬旗等提出一种脉冲宽度可调变的发光二极管驱动集成电路装置,该装置可以提高更新率,降低发光二极管闪烁现象[6]。张晋芳等提出一种新的PWM 控制信号的方法及装置,该装置只需要极小的硬件开销且不需要对应用环境提出更高的需求,即可以实现更好的驱动效果[7]。王顶基于打散脉冲调制(Scrambled Pulse with Modulation,SPWM)打散算法,通过内建双SRAM 的存储模式对输入数据进行处理和优化,提高刷新率和低灰效果[8]。赵肃等提出一种乱序PWM算法提高芯片刷新率,采用PWM 合成技术提高LED 的色彩灰度等级[9]。陈培腾等在传统PWM 基础之上,结合双边触发器技术,该技术在一定程度上可以提高刷新率,避免闪烁[10]。

本文在PWM算法基础之上,采用时钟倍频技术,提出一种倍频优化打散脉冲调制(Optimize-Scrambled Pulse with Modulation,OS-PWM)算法,将一组数据的显示时间打散成几个较短的时间段,每个较短的时间段均保持原先的占空比,以增加LED显示屏的整体刷新率,在不改变总灰度的前提下提高刷新率。

2 倍频OS-PWM算法实现

2.1 OS-PWM算法

OS-PWM算法[11]是在打散SPWM算法的基础之上,增加等级优化功能,在不改变总体灰度的前提下通过增加打散组数提高刷新率和低灰显示均匀性,从而使显示画面更加细腻,均匀性更好。该算法流程的具体步骤为:

1)16 位二进制灰度数据D15D14...D1D0由外部接口串行输入至驱动芯片中,范围为0~65535,刷新倍数为2K=1/2/4/8,在打散成64 个子周期的基础上,进一步打散提高的刷新倍数;优化等级G=0/1/2/3,要求每个子周期中每组PWM 脉冲不小于设定的参考时钟周期数1/2/4/8 个GLCK;

2)将灰度数据划分为10 位高阶数据和6 位低阶数据,每个打散子周期的时钟周期数为1024 个显示时钟GCLK,整个显示周期最小打散的子周期个数为64。在设计中定义一个10 位的计数器CNT1 用于计数每个子周期时钟周期数,6 位的计数器CNT2 用于计数打散的子周期个数,优先计数CNT1,在每个时钟上升沿加1,当CNT1 溢出时CNT2 自动累加;

3)根据刷新倍数,将整个显示周期打散成64/128/256/512 个子周期,此时每个子周期的时钟周期数为1024/512/256/128 个,整个显示周期依旧为65536 个显示时钟GCLK;

4)根据刷新倍数和优化等级,将10 位高阶数据平均分配到64/128/256/512 个子周期,每个子周期中PWM 脉冲个数为TM=D1529-K-G+D1428-K-G+...+D6+K+G20,在每个子周期中,CNT1 从0~TM-1 依次输出PWM 脉冲;

5)将剩余 6 位低阶数据均匀分配到64/128/256/512 个子周期中,此时每个子周期中PWM脉冲个数TL不超过1/2/4/8 个,并按照均匀分配原则分布到各子周期中,其均匀分布原则为按照CNT2[0:5]/ {CNT2 [9],CNT2 [0:5]}/ {CNT [8:9],CNT2 [0:5]}/{CNT[7:9],CNT2[0:5]}顺序,在CNT1 为TM时,依次将TL个PWM 脉冲输出;

6)根据行数32 和通道数16,分别应用32×16 次步骤1~5,生成PWM 控制LED显示[12]。

表1 为采用OS-PWM算法的优化等级和刷新倍率表,列出了详细的刷新倍率、优化等级、打散子周期和最小PWM 脉冲数之间的关系。

表1 优化等级和刷新倍率表

2.2 倍频OS-PWM算法

在OS-PWM算法基础之上,采用倍频技术,其原理是将原本从亮到灭的计数周期均匀打散成多个时间较短的子周期,所有子周期的占比总和与原先整个计数周期相同。这样在不影响整体灰度的情况下,极大地提升了LED显示屏的整体刷新率。结合时钟双沿计数技术,可以在相同时间内刷新更多的数据,以此提升灰度等级和显示的细腻度。倍频OS-PWM算法将16 位数据分为9 位的高位数据MSB 和7 位的低位数据LSB。采用在图像显示中占有主要作用的高9 位的MSB 数据进行打散的方式来提高LED显示屏的刷新率。MSB 的计数周期打散后在每一个显示子周期中都会进行计数,再加上一次LSB 的计数周期(根据具体数值平均分配到不同的显示子周期中),就可以达到和未分解的PWM 一样的分辨率[13]。

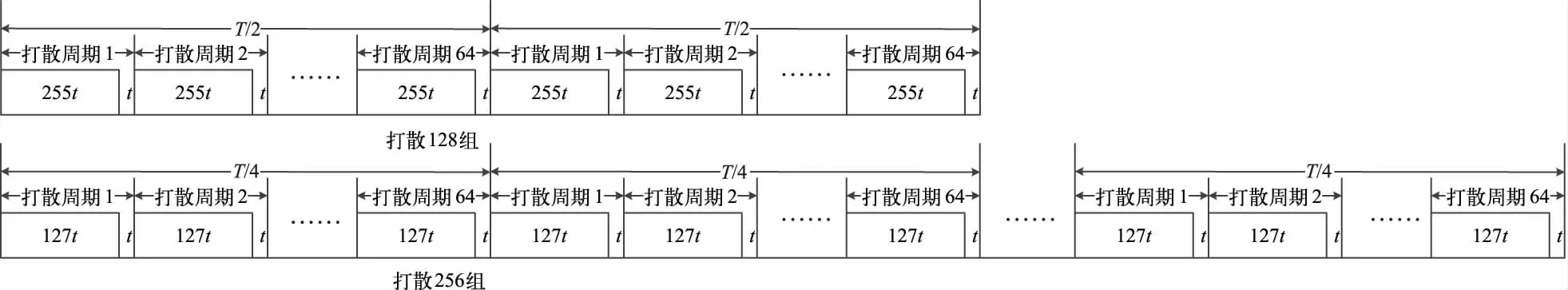

将一个显示周期T 分为128/256 等份,每份以9位256t 或128t(采用时钟倍频技术,双沿计数)为基础,和一个低位数据的计时时钟周期t 组成512 或256个计数周期。这样总计仍为256t×2×128=65536t=T(128t×2×256=65536t=T),总灰度不变,但刷新率提高了128 倍或256 倍,即在64 倍的基础上提升2 倍或4倍(下同),倍频OS-PWM算法打散控制图如图1 所示。

图1 倍频OS-PWM算法打散控制图

同时定义2 个PWM显示计数器CNT1(9 位)、组数计数器CNT2(7 位)、行计数器以及下鬼影控制信号和首行偏暗调节指示信号。CNT1 用于计数每组PWM周期显示所需的时钟数(即灰度数值),CNT2 用于计数打散组数实现均匀打散,CNT1 和CNT2 组合实现PWM 计数控制。5 位行计数器记录行数变化,消影调节指示信号EN_GHOST 需要4.5 个显示时钟GCLK,在当前行通道开启前拉低,通道关闭后拉高下一行消影,预留足够充电时间,解决下鬼影问题;首行在通道开启前拉高,通道关闭时拉低,由模拟部分完成首行偏暗调节,解决首行偏暗问题。

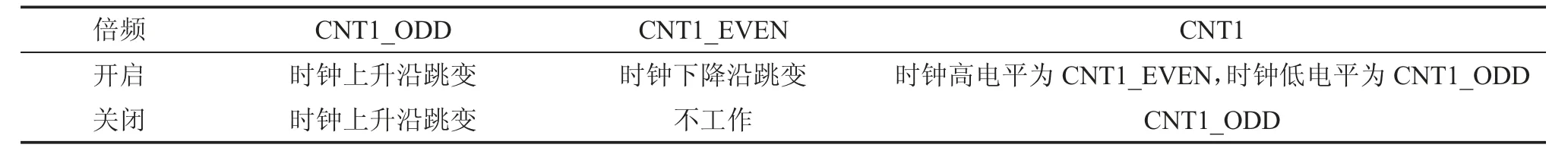

为提升灰度等级,采用时钟双沿计数的方式,定义两个计数器CNT1_ODD 和CNT1_EVEN,分别在显示时钟GCLK 的上升沿和下降沿进行计数,通过控制信号和两个计数器异或运算得到一个双沿计数器。在关闭倍频功能时,只有CNT1_ODD 工作,在显示时钟GCLK 上升沿计数,显示计数器CNT1 直接由CNT1_ODD 得到。在开启倍频功能时,双沿计数工作,CNT1_ODD 在时钟上升沿翻转,CNT1_EVEN 在时钟下降沿翻转,最终的显示计数器CNT1 在显示时钟GCLK 高电平时选择CNT1_EVEN,显示时钟GCLK低电平选择CNT1_ODD,CNT1 选择如表2 所示。

表2 CNT1 选择表

一帧16 bit 的数据大小为65536,即共需要65536个时钟,在关闭倍频的情况下,打散128 或256 组分别需要512 或256 个时钟,相对于打散64 组,打散128或256 组的刷新倍率依次提升2 倍或4 倍。在开启倍频的情况下,双沿同时计数,显示相同数据所需要的时间减少一半,即时钟个数为原来的1/2。此时,同样一帧16 bit 的数据打散128 或256 组则分别需要256或128 个时钟,在相同时间内,相对于打散64 组,刷新率提升4 倍或8 倍,倍频OS-PWM算法刷新倍率如表3 所示。

表3 倍频OS-PWM算法刷新倍率表

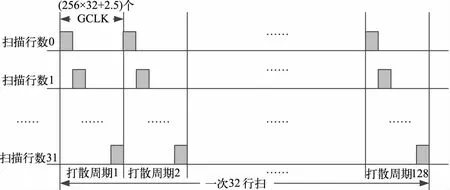

32 行扫16 通道恒流LED显示驱动芯片的实际具体应用如图2 所示。在每一个打散周期内,从0~31行依次进行切换输出。在总的时钟周期不变的情况下,打散组数可配置为128 组和256 组,以应对不同场合的应用需求,由此实现不同的刷新率需求。分组数目越多,打散情况越好,刷新率越高,但同时输出开关的开关频率也越高。在每一个打散的组中,PWM 波形的脉宽将会最大可能平均。在倍频OS-PWM 模式被配置为打散128 组,分别命名为PERIOD0、PERIOD1、PERIOD2、......、PERIOD127,如果灰度为256,每组脉宽的最大可能平均将会为2 个显示时钟GCLK周期,如果灰度为132,除了PERIOD0、PERIOD64、PERIOD32、PERIOD96 中的脉宽为2 个显示时钟GCLK 周期,其他仍为1 个显示时钟GCLK 周期,即平均后多余的4 个灰度将会平均分配到4 组里,每组之间隔32 组以达到尽可能的平均分布。

图2 应用倍频OS-PWM算法的32 行扫时序

通过对比OS-PWM算法和倍频OS-PWM算法,可以发现最高刷新率同样达到8 倍刷新率,但倍频OS-PWM算法复杂度降低一半,整体电路面积减少40%。

3 结果及分析

基于倍频OS-PWM算法,设计的32 行扫恒流PWM 输出LED 驱动芯片是一款小间距大屏LED显示屏驱动芯片,内建倍频OS-PWM 高刷新算法,专门针对小点间距显示屏存在的低灰问题做出优化处理,可以有效解决传统的PWM 刷新率较低、低灰显示均匀性差等问题。

基于LINUX 系统,采用专业EDA 工具,对搭载此算法的显示驱动芯片进行全局仿真。

仿真结果见图3,gclk_double 为开启倍频算法使能信号,高有效;pwm[15:0]为16 路的PWM 输出,高电平表示输出有效,显示时钟GCLK 为35 MHz,每个时钟周期为28 ns。从pwm[15]到pwm[0],打开时间依次减半。

关闭倍频gclk_double=0,打散子周期数为128 的仿真结果见图3,打散128 组,每组65536/128=512 个显示时钟周期,每个打散子周期为512×28=14336 ns,与仿真结果一致。

图3 关闭倍频,打散子周期数128 的仿真结果

关闭倍频gclk_double=0,打散子周期数为256组,每组65536/256=256 个显示时钟周期,每个打散子周期为256×28=7168 ns,与仿真结果一致。

开启倍频gclk_double=1,打散子周期数为256组,每组65536/256=256 个显示时钟周期,采用时钟倍频技术,每个打散子周期为256/2×28=3584 ns,与仿真结果一致。

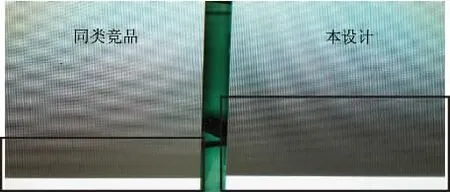

搭载该算法的芯片已经通过测试,对比搭载OS-PWM算法的芯片[8],面积由980×1500=1.47 μm2缩减到910×980=0.891 μm2,面积减少40.13%。图4 为使用该算法芯片的显示屏与同类竞品在相同配置下的实测结果对比,从图中可以看出,该芯片低灰段的长度是同类竞品的两倍,具有更好的显示均匀性。

图4 搭载该算法的芯片与同类竞品[8]实测结果对比

4 总结

本文针对小点间距LED显示屏中存在的刷新率较低和低灰显示均匀性差等问题,基于OS-PWM算法,采用时钟倍频技术,提出一种倍频OS-PWM算法。将一组数据的显示时间打散成几个较短的时间段,每个较短的时间段均保持原先的占空比,以增加LED显示屏的整体刷新率,在不改变总灰度的前提下提高了刷新率,算法复杂度减少一半,并对算法进行等级优化,提升了显示均匀性。基于该算法设计的LED 驱动芯片,面积可减少40%。