基于SiP 技术的多片DDR3 高速动态存储器设计

2022-02-17张小蝶邱颖霞邢正伟

张小蝶,邱颖霞,2,许 聪,2,邢正伟

(1.安徽芯纪元科技有限公司,合肥 230000;2.中国电子科技集团公司第三十八研究所,合肥 230088)

1 引言

系统级封装(System in Package,SiP)以其小型化、更轻薄、多功能的优势,在通用或专用的高速电路及系统高度集成的硬件电路设计中占据着重要位置[1]。为顺应需求的日益扩大,电子设备在功能日益复杂强大的同时需要其内存充足且运行足够可靠稳定。以往可以利用PCB 板载实现大内存容量的主控制器和内存芯片间频繁读写功能,然而板载设计无法满足小型化、轻量化需求。另外,从系统的角度考虑,主控芯片与内存芯片之间的读写性能极大地影响着系统运行的速度和稳定性[2],信号完整性问题面临更大的挑战,同时内存容量的扩大对系统集成度和封装可靠性的要求更加严苛。

DDR3 是目前系统级计算设备的主流存储器,采用的8 位预取技术提高了存储带宽,运用的源同步时序可支持800 Mbps/1066 Mbps/1333 Mbps 的数据读写速率,各组信号遵循STLL15 电平规范,同时在DDR3内存设计标准中引入的写平衡(Write Leveling)机制可以通过DDR 控制器动态调节每组位线时序补偿延时,从而达到同步[3]。其接口电压降低为1.5 V,这在一定程度上降低了器件功耗,但同时也使得主控芯片和内存芯片之间信号的噪声容限减小,由此带来的信号完整性问题更加突出。目前已有规范指出Fly-By 拓扑对于控制偏移时序有一定效果[4],但还不能确保高频率高带宽的存储系统能够实现预期的信号完整性,因此还需借助进一步的仿真验证。

相比低速电路,信号完整性问题在高速电路中尤为凸显,因此低速电路设计流程、开发方式等已然不适用于高速电路。高速信号完整性仿真软件应运而生,在提高设计质量的同时也极大地提高了设备开发效率。目前市面上高速信号质量分析的工具有很多,其中Cadence Sigrity 是常用的DDR 信号完整性仿真软件之一。

本文利用SiP 技术设计了一款主控芯片和多片内存芯片结合的一体化高速动态存储设备,主要介绍了该设备的电路拓扑形式和SiP 版图PCB 设计,对DDR3 关键信号完整性完成了仿真验证和分析,并对由分立封装形式控制器芯片、DDR3 颗粒所构成的板级高速动态存储系统进行仿真分析对比。结果表明,相对于采用分立板载器件设计的具有相同功能的板级存储设备,利用SiP 技术设计的多片DDR3 颗粒一体化高速动态存储器性能更优。

2 SiP 电路拓扑设计

拓扑原指计算机中各个网络节点之间的连接形式,如今随着数字电路时钟频率的不断提升,对于多负载高速电路而言,拓扑是指电路板中各芯片之间的布线顺序和布线结构。DDR 有众多信号线,不同功能的信号线可驱动负载的数量也不等[5],例如数据线一般只接一个负载芯片,而地址线和时钟线可以连接多个负载芯片。通常多负载电路采用的布线方式有星型拓扑结构、菊花链拓扑结构、Fly-By 拓扑结构,其中Fly-By 拓扑结构是DDR3 规范中推荐使用的一种形式,它是一种特殊的菊花链拓扑结构,特点在于每一个分支走线较短,图1 给出了一种采用Fly-By 拓扑形式的4 片负载芯片与CPU 布线结构示意图。

图1 Fly-By 拓扑布线示意图

2.1 CPU 与DDR3 电路原理设计

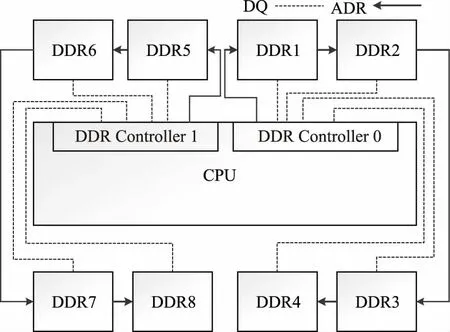

由上文可知,对于DDR3 颗粒而言,其数据线是采用点对点的连接方式,而地址、命令、控制、时钟等信号线采用的是多点互联的形式[6]。基于以上分析,对于一拖多DDR3 颗粒的高速电路可以采用Fly-By 拓扑进行地址线、控制线、时钟线布线。由于本文所使用的“魂芯”系列DSP 处理器内部含有2 个64 bit 的DDR 控制器通道,在设计时要考虑双通道连接形式,为了达到存储设备容量需求,SiP 设备选择的是4 Gb 16 bit DDR3 裸芯,每个通道的DDR 控制器需要挂接4 颗DDR3 裸芯,2 个通道共需要8 颗DDR3 裸芯。

考虑到DSP 处理器、DDR3 颗粒一体化SiP 电路所需芯片数目较多、布线复杂,原理图设计结合拓扑结构,图2 给出了8 片负载DDR3 芯片与CPU 的原理示意框图,其中DDR(1~4)地址线、控制线、时钟线采用Fly-By 拓扑走线形式连接到DDR Controller 0 片选,数据线点对点连接到对应的DDR Controller 0,DDR(5~8)地址线、控制线、时钟线采用Fly-By 拓扑走线形式连接到DDR Controller 1 片选,数据线点对点连接到对应的DDR Controller 1。

图2 SiP 原理框图

2.2 CPU 与DDR3 电源设计

根据图2 所示的SiP 原理框图可知,在此一体化SiP 电路中,DDR3 颗粒有众多的电源引脚,且负载动态响应较高,因此在进行电源设计时首先需要考虑直流供电的带负载能力,其次要考虑直流供电的稳定性能否满足8 片DDR3 负载芯片的供电要求,而从电源完整性角度考虑,所设计电路需满足阻抗连续性要求,确保信号具有尽可能短的返回路径,从而在降低电磁辐射的同时减少对其他信号的干扰。

考虑到本文采用的设计方法是SiP 形式,其由外部直流稳压电源供电,因此直流电源带负载能力在本文不做详述。而为了提高电源完整性,除了外部供电电源需要稳定外,还需要在整个SiP 内部电源系统上并联一定数量的去耦电容,使电源回路阻抗尽可能最小。

图3 为本文所设计的SiP 电路原理示意图,其中图3(a)为CPU 电源上的去耦电容,图3(b)为DDR3 电源上的去耦电容。

图3 CPU 与DDR3 供电电路原理图

3 SiP 版图设计

3.1 板层设计

SiP 原理设计完成后,版图设计是尤为重要的一环,关系着功能实现以及性能满足。图4 为此款SiP 的层叠结构示意图,采用的是10 层ABF 材料基板,L1、L10 为器件布局层,L3、L5、L8 敷设完整的地层,为相邻布线层L2、L4、L7 的高速信号走线提供电流返回路径,从而减少高速信号的反射和辐射。L6、L9 是电源层,由于SiP 电源种类较多,考虑到在负载电流较大、负载动态响应较高时的电源完整性问题突出,分别利用相邻的L5、L8 地层做电源回流路径,这样既能增加电源稳定性,又能提高封装基板的散热能力。

图4 SiP 层叠结构

3.2 器件布局和布线设计

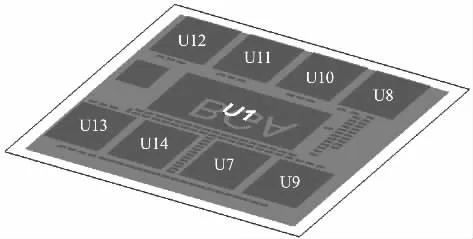

此款SiP 所用到的器件主要有1 颗主控芯片和8颗DDR3 内存芯片,器件布局主要考虑的是在满足SiP 封装尺寸要求下主控芯片、DDR 颗粒、去耦电容和终端匹配电阻的布局。根据第2 节所述内容,考虑到主控芯片挂接多片DDR3 负载芯片的拓扑形式为Fly-By,而DSP 处理器拥有双通道的DDR 控制器,故对8 颗DDR3 颗粒和CPU 采用以主控芯片为中心的对称布局布线,如图5、6 所示。

图5 SiP 器件布局

图6 SiP 所有信号层布线设计

4 PCB 后仿验证

将布线后的PCB 文件导入Cadence Sigrity 相关软件,利用powerSI 提取网络与信号的阻抗参数(Z)和散射参数(S),为后续利用systemSI 做时域分析提供基础。本文主要从拓扑结构验证、DDR3 时序及眼图测量、SiP 与板级设计方案对比三方面做一体化高速动态存储SiP 的PCB 板后验证分析。

4.1 拓扑结构仿真验证

根据前文所述,DDR3 数据信号包括DQ、DQS、DM 等,将数据总线全部抽取仿真其波形所形成眼图如图7 所示。由图7 可知,DDR3 数据线、地址线信号清晰,眼图开合规整,差分时钟线信号上升沿、下降沿以及过冲均满足要求。

图7 SiP DDR3 典型信号走线波形

4.2 DDR3 时序验证

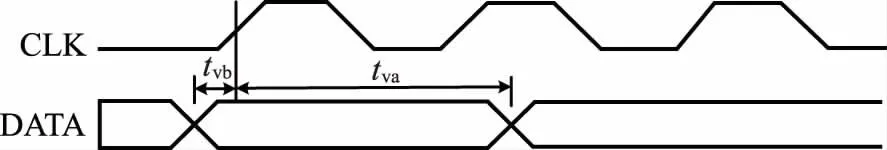

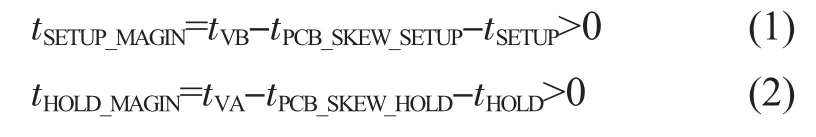

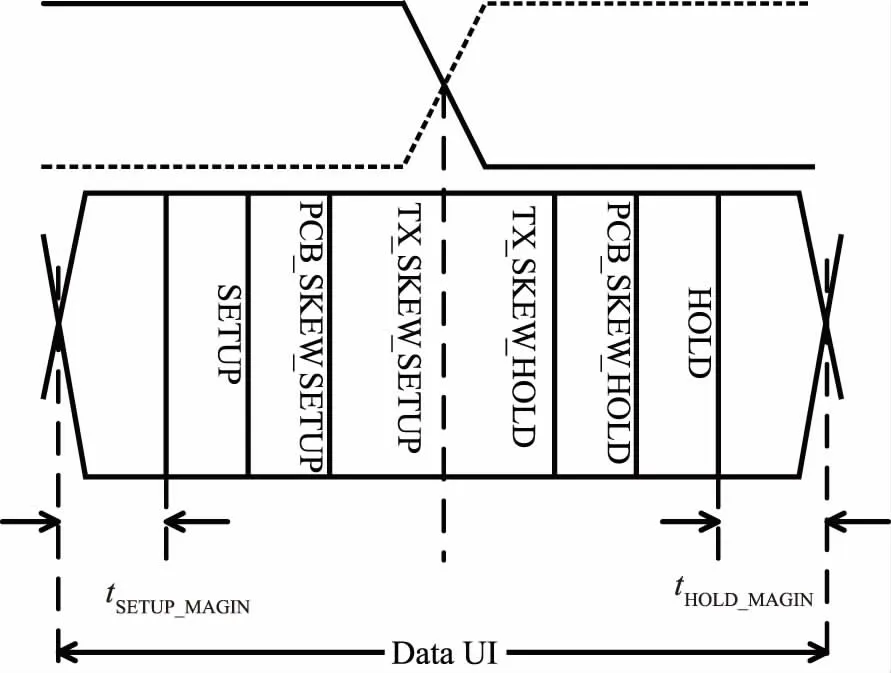

时序裕量是否满足规范要求是DDR3 总线设计是否成功的重要衡量指标,DDR3 采用的是源同步时序,在进行时序验证时主要考虑的是时钟和数据信号经过完整路径后的延时、器件内部延时、器件建立保持时间以及信号的过冲等。源同步时序验证的方法主要有公式法和眼图分析法[7],二者的时序计算原理是一样的。如式(1)、(2)所示,式中tVA为驱动端数据在驱动端时钟发出前有效的时间,tVB为驱动端数据在驱动端时钟发生后有效时钟,图8 给出了DDR3 引入写平衡机制后的输出时钟与输出数据的关系图。图9 为源同步时序眼图分析原理图。

图8 时钟与数据的关系

图9 源同步时序眼图分析原理

在DDR3 高速动态存储电路中,数据信号在进行数据读取时采用的是双边沿采样,因此数据线的数据传输速率是时钟线的2 倍。本文所使用的“魂芯”II-A型DSP 最大总带宽为128 Gbps。根据DDR3 规范,数据速率为1066 MHz 的条件下,数据的建立时间和保持时间之和不能小于175 ps,数据信号的过冲峰值不能超过0.4 V。

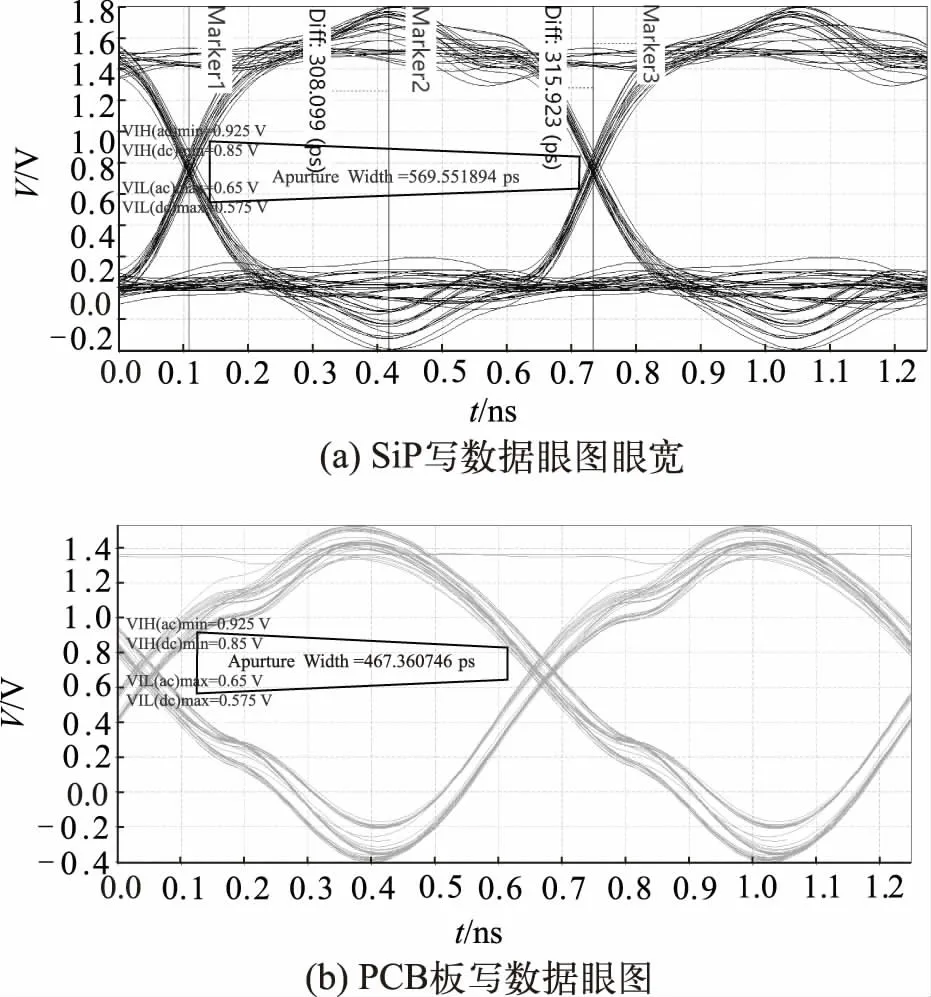

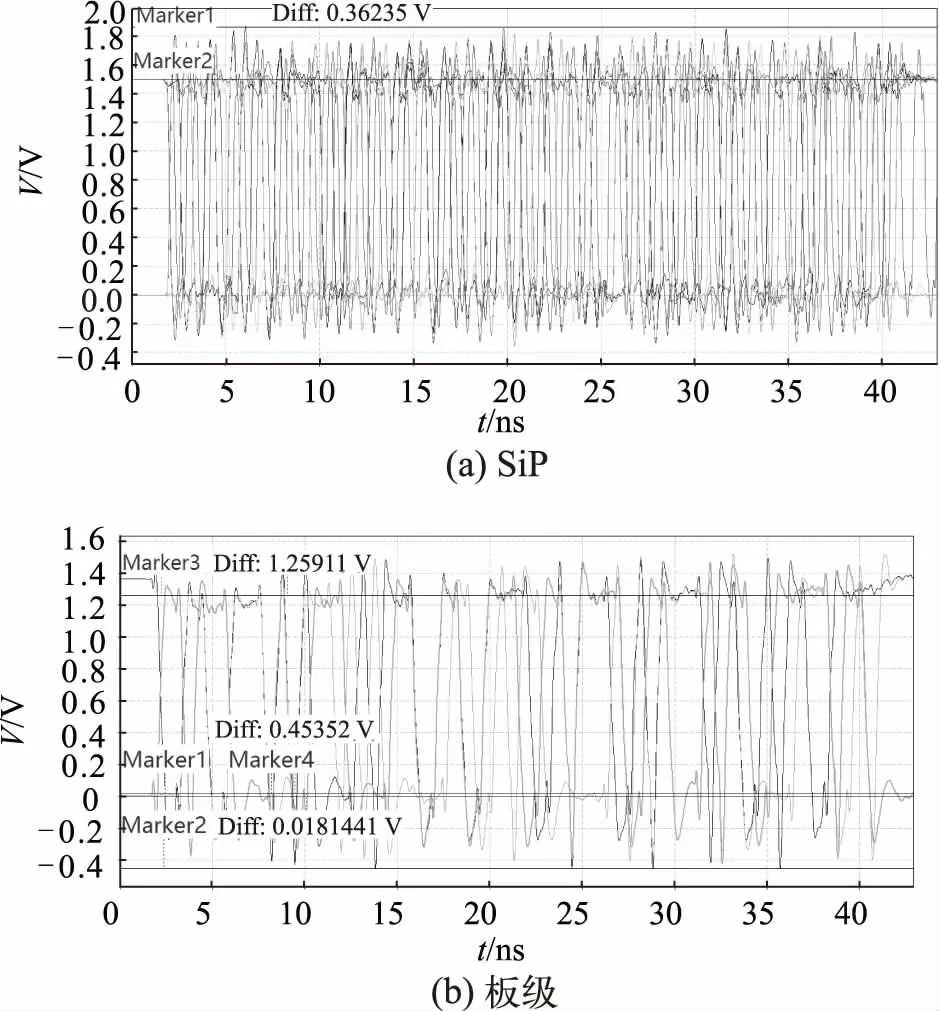

为了验证DDR3 的时序是否满足规范,本文采用Cadence Sigrity 软件进行信号仿真[8-9],并对仿真及其结果进行分析。图10、11 分别给出了数据总线写时序眼图和时钟建立和保持时序测量图。由仿真结果可知,数据线的建立为312.776 ps,保持时间为313.882 ps,建立时间和保持时间之和为626.658 ps,远大于规范所要求的175 ps,故建立和保持时间满足要求;地址线的建立时间约292.553 ps,保持时间约286.594 ps,建立、保持时间之和为579.147 ps,远大于规范所要求的175 ps,故建立和保持时间满足要求。最大过冲值约为0.38 V,小于规范所要求的0.4 V,综合以上分析,DDR3 时序验证满足要求。

图10 时钟写数据眼图时序测量波形

图11 时钟建立和保持时间测量波形

4.3 与板级设计方案对比

针对本文所设计的多片DDR 颗粒高速动态存储器SiP,为考量其性能优劣,对具有同样功能的板级多片DDR 颗粒动态存储控制板进行了设计和验证。该存储控制板原理框图与SiP 一致,且主控制器与DDR颗粒之间同样采用Fly-By 拓扑进行连接,如图1、2 所示。该控制板采用的主控制器和DDR3 颗粒均为SiP所用的“魂芯”II-A 型DSP 裸片、DDR3 颗粒裸片的封装形式。存储控制板波形仿真结果如下,其中图12 为PCB 板DDR3 地址总线眼图波形,对比图7(c)可知,SiP 的地址线信号眼图更加清晰。图13 为SiP 和板级数据线眼图眼宽测量图,由此可知,SiP 眼宽为569.552 ps,板级眼宽为467.361 ps,相较于板级仿真结果,SiP 眼图更加规整。图14 为SiP 和板级DDR3 数据信号线电平仿真波形和测量结果,由图可知,SiP 电压过冲约为0.37 V,满足标准,而板级电压过冲值约为0.454 V,超过了标准规定的0.4 V,故SiP 电平阈值符合规范要求。

图12 PCB 板地址线眼图

图13 SiP 和板级数据线眼图眼宽测量结果

图14 DDR3 电平及过冲测量结果

针对以上仿真试验,同时结合JEDEC 各项标准将仿真结果总结到表1,可以看出,本文所采用的SiP 方案设计多片内存负载的高速动态存储设备满足JEDEC 标准,且DDR3 时序及电平性能优于PCB 板级设计方案。

表1 高速动态存储控制SiP 与板级设计仿真对比

5 结论

本文以自研“魂芯”II-A 型DSP 处理器为核心搭载多片DDR3 内存负载,利用SiP 技术,设计了一款多片DDR3 高速动态存储SiP 设备,分别从电路拓扑设计、版图设计详细介绍了该SiP 的设计原理及方案实现,并根据PCB 后仿验证分析,论述了该SiP 利用Fly-By 拓扑设计的可行性,另外利用Cadence Sigrity仿真验证,分别从DDR3 时序测量、电平测量、眼图分析三方面验证该存储设备的性能均较板级实现方案更优。由此可知,本文所述方法在一定程度上优化了板级设备的性能,同时提高了设备及片上系统的集成度,能够满足市场日益凸显的设备小型化、轻量化需求。