基于0.18 μm CMOS 加固工艺的抗辐射设计

2022-02-17周晓彬左玲玲周昕杰

姚 进,周晓彬,左玲玲,周昕杰

(中科芯集成电路有限公司,江苏无锡 214072)

1 引言

在空间辐射环境中,总剂量(Total Ionizing Dose,TID)效应、单粒子闩锁(Single Event Latch-up,SEL)效应、单粒子翻转(Single Event Upset,SEU)效应是影响CMOS 元器件可靠性的主要因素[1]。基于0.18 μm 特征尺寸附近的工艺节点,国内已有多个成功的辐射加固设计案例[2-3],但良好的辐射加固策略不仅要保证加固器件的可靠性,同时也应该尽量减小加固设计对元器件面积、速度等基本性能的影响。本文基于0.18 μm CMOS 加固工艺,采用工艺加固与设计加固结合的方式,对TID、SEL、SEU 的具体加固方法进行描述,产品验证表明加固策略在抗辐射性能及面积上具有明显优势。

2 总剂量加固

CMOS 工艺总剂量辐射效应主要作用于SiO2层[2]。电离后产生的电子-空穴对在外界电场的作用下,只有少量高迁移率电子与空穴复合,多数漂移出SiO2层;少数低迁移率空穴与电子复合,多数向SiO2/Si 界面运输,一部分直接形成SiO2一侧的陷阱电荷,另外一部分则随着时间堆积,最终形成界面陷阱电荷,进而影响器件的性能。

根据国内外相关研究成果[4-6],0.18 μm CMOS 工艺下,栅氧受TID 影响很小,阈值电压变化可以忽略,但STI 场区的正电荷不断积累会引起场区下的P-衬底反型,在相邻有源区的压差下形成漏电通路,导致电路静态电流激增。STI 隔离场区的主要漏电通路包括:N 管自身源漏端有源区的场边缘漏电通路;相邻N 管在有源区形成压差后产生的漏电通路;N 管与相邻N阱内的P 管在有源区形成压差后产生的漏电通路。

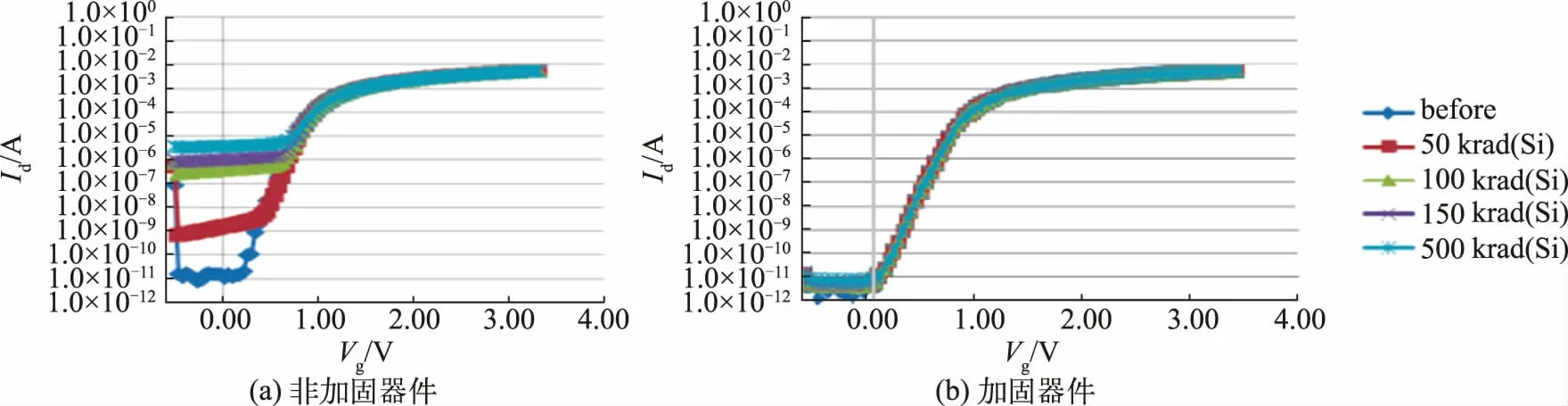

针对0.18 μm CMOS 工艺下总剂量引起的漏电特性,加固工艺针对性地对STI 场区进行总剂量加固[7],主要通过离子注入的方式提高STI 场区下P-衬底反型的阈值电压,从而抑制了各漏电通道的开启。对总剂量辐射更敏感的3.3 V NMOS 器件选取W/L=10 μm/0.35 μm,加固前后不同剂量下的关态漏电流Id与栅电压Vg特性曲线如图1 所示。图1(a)是商用非加固NMOS 器件,可以看出,在50 krad(Si)剂量时Id已变化2 个数量级;100 krad(Si)剂量时Id已变化4 个数量级。图1(b)是商用加固NMOS 器件,可以看出,在500 krad(Si)剂量时器件I-V 特性曲线与辐照前基本一致,Id基本没变化,因此采用工艺加固后,3.3 V NMOS 抗总剂量辐射能力从加固前的不到50 krad(Si)达到了500 krad(Si)水平。考虑到STI 场区注入的加固工艺可能会对器件电特性,特别是对沟道较短的1.8 V NMOS 电特性产生影响,对加固前后1.8 V NMOS 管常规电参数进行测试,结果如表1 所示。加固前后击穿电压未发生变化,阈值电压及饱和电流变化幅度均在10%以内,满足电路实际设计需求,针对加固后NMOS 管电参数的变化,重新抽取了器件Spice 模型,以保证仿真精度。与常规的环形栅等依靠版图设计的总剂量加固设计相比,加固工艺的版图面积及设计难度大大降低,且总剂量指标更高。

图1 不同辐射剂量的I-V 特性曲线

表1 加固前后电参数对比表

3 单粒子闩锁加固

CMOS 体硅工艺下反向器单元的寄生PNPN 可控硅结构(Silicon Controlled Rectifier,SCR)及其等效电路如图2 所示,主要包括寄生横向NPN 双极晶体管T1、寄生纵向PNP 双极晶体管T2 和寄生电阻R1~R4。高能粒子入射器件后电离出大量的电子-空穴对,在电场作用下,PMOS 的源端吸收过剩电子流,NMOS的源端吸收过剩空穴流,电子和空穴定向移动形成的电流通过寄生电阻R2,在T1 的发射结产生足够大的压降时,T1 正偏导通,此时T1 的集电极电流流过另外一个纵向PNP 双极晶体管T2 的基极,电流通过寄生电阻R1在T2 发射结产生足够大的压降时,T2 正偏导通,T2 的集电极电流又进一步触发T1,使得T1 的集电极电流继续增加,不停的正反馈使SCR 进入电流再生状态,最终导致芯片永久失效[8]。

图2 CMOS 器件剖面结构及等效寄生电路

对图2 所示的结构及等效电路图进行分析,R1、R2可简单等效为P 管源端到体接触的电阻、N 管源端到体接触的电阻,R3、R4可简单等效为N 管及P 管有源区间电阻。R1、R2的阻值与源端到体接触的距离成正比,R3、R4的阻值与N 管及P 管有源区距离成正比。降低R1、R2阻值,根据分压原理,可以减小寄生双极晶体管T1 及T2 的发射结压降;同理,增加R3、R4阻值,也能减小寄生双极晶体管T1 及T2 的发射结压降,从而抑制T1 及T2 的发射结正向导通,降低发生闩锁的可能性。因此通过减小P 管、N 管源端到体接触的距离L1,增加N 管有源区及P 管有源区的距离L2均能抑制单粒子闩锁。通过TCAD 仿真[9],模拟了非外延片在400 K 温度下L1、L2的SEL 特性,结果如表2 所示。在获取L1及L2的合理尺寸后,将该值放入设计规则检查(Design Rule Check,DRC),将该方法与常规的保护环加固设计方法对比,可明显减小版图面积。

表2 非外延片在400 K 单粒子闩锁线性能量传输阈值(Linear Energy Transfer Threshold,LETth)(MeV·cm2/mg)

4 单粒子翻转加固

高能粒子入射半导体器件的敏感区后,产生的瞬间电流引起器件逻辑状态的改变即为SEU。SEU 主要发生于存储单元,组合逻辑产生的单粒子瞬态(Single Event Transition,SET)毛刺信号如被存储单元采集,同样会产生SEU。

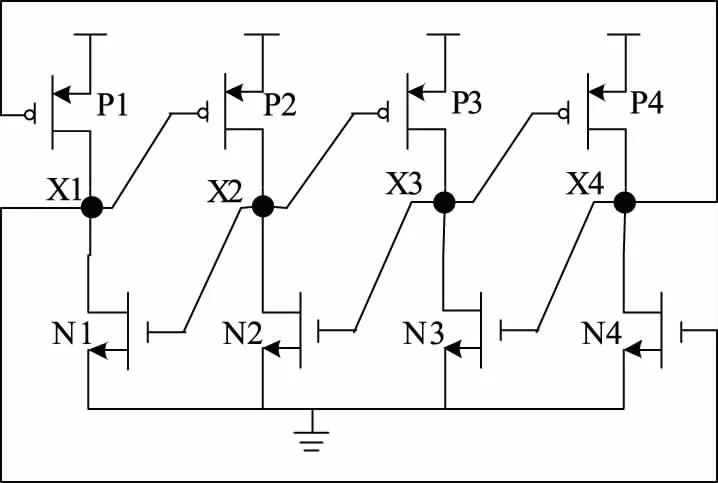

SEU 加固通常采用双互锁存储单元(Double Interlocked Storage Cell,DICE)结构,其结构如图3 所示,X1、X3 节点为数据输入口,X1~X4 4 个节点存储逻辑状态,任意一个节点的状态都由其左右相邻的节点所控制,因此它们起到了反馈互锁的作用。当其中一个节点受到单粒子轰击发生正向或负向翻转时,由于受到其他节点的钳制,受轰击的节点会很快恢复正常逻辑电平,其他节点始终保证正确电平。根据TCAD仿真确定LETth为37 MeV·cm2/mg 时的敏感节点间距,以保证DICE 结构的抗辐射性能。由于0.18 μm 工艺下SET 已比较明显,基于DICE 加固时序单元,同时考虑时钟、复位等全局信号加固,可保证电路满足1×10-10errors/(bit·day)的翻转率指标。

图3 时序电路的DICE 结构

在宇航产品的关键应用区域,如负责系统故障的诊断、控制、调配和重构等均需满足37 MeV·cm2/mg的翻转阈值要求,同时考虑到其他设计领域高可靠性电路的设计需求,开发了支持全局三模冗余(Triple Module Redundant,TMR)设计的单元库设计套件及设计流程,以满足高抗辐射指标、高可靠性指标的核心控制逻辑设计需求。

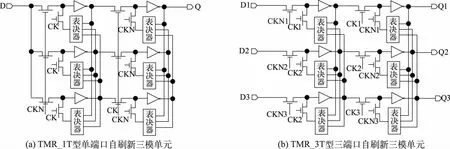

TMR 加固时序单元逻辑示意图如图4 所示,该结构主要将表决器移植到时序单元内部,通过内部表决器完成时序单元存储节点的实时刷新,当其中一个节点翻转时,通过表决器立刻恢复至正确的节点状态,避免了内部存储节点的错误累积,极大提升了单元的抗翻转能力及可靠性。图4(a)是用于常规综合的TMR_1T 单元,为单端口设计,即三路数据输入、时钟输入、输出各共用一个端口,图4(b)是用于单元库全局TMR 设计的TMR_3T 单元,该单元为三端口设计,与TMR_1T 相比,所有三路输入输出端口各自独立。单元库设计套件提供了全局TMR 网表生成的脚本,帮助用户快速实现全局TMR 设计,同时对全局三模中使用的TMR_3T 单元的时序功耗文件及功能仿真文件进行了深度开发,保证用户在全局三模网表下仍可完成形式验证、PT 分析等数字正向流程。尽管全局三模设计的电路规模更大,但在产品开发中发现,圆片中测时成品率却更高,原因是当电路中某个器件失效时,只影响三模中其中一路的局部逻辑,对电路实际功能无影响,为保证实际交付给用户电路的高可靠性,对自刷新三模单元逻辑进行了优化设计,保证中测过程中每一路均可以单独完成测试。

图4 TMR 单元设计示意图

5 实际应用情况

目前,基于以上加固方法开发的抗辐射单元库,已成功完成5 款以上抗辐射产品的开发。以其中一款数字信号处理电路为例,该电路非抗辐射版本基于商用0.18 μm CMOS 工艺制造,在加固工艺上分别采用DICE 加固设计及全局TMR 加固设计,流片后各项性能指标对比如表3 所示。DICE 加固版本的面积是商用线非加固版本面积的2 倍以内,非加固版本采用9Track 单元库,加固版本采用了12Track 单元库,如除去单元高度影响,加固版本的面积增加在30%左右,与非加固工艺下的抗辐射加固电路对比[2],面积优势明显。DICE 加固版本的最高工作频率较非加固版本降低近30%左右,其中包括商用线与加固工艺的器件特性偏差。全局TMR 加固版本较非加固版本面积增加近5 倍,较DICE 面积增加在3 倍以内,考虑到面积增加后对电路速度的影响,全局三模设计的工作频率并未明显降低,同时全局三模电路在Ta 离子下仍未翻转,具备超高的抗单粒子翻转能力。

表3 非加固版本与加固版本性能指标对比

6 结论

基于0.18 μm CMOS 加固工艺,通过工艺加固,在未增加版图面积的前提下,抗辐射电路总剂量水平达到300 krad(Si)以上;通过优化版图设计规则,以较小的面积损耗满足抗单粒子闩锁的设计需求;通过采取不同的加固设计方法,满足各种单粒子翻转指标的抗辐射电路需求。与基于商用工艺的抗辐射电路对比,能在更小的面积下实现更高的抗辐射性能,该加固工艺设计平台可为用户提供更具竞争力的高可靠性产品开发途径。

0.18μm CMOS 加固工艺可支持3.3 V 或5 V 器件,配合设计平台已开发的抗辐射低压差线性稳压器(Low Dropout Regulator,LDO)IP,内核标准单元的1.8 V 工作电压由LDO 提供,可实现全芯片3.3 V 或5 V 的单电源设计,对于目前广泛使用的3.3 V 及5 V抗辐射应用系统,基于该加固工艺设计平台,可快速实现更小型化、更低功耗、更高工作频率的抗辐射芯片替换,全面提升现有抗辐射应用系统的性能,具备良好的应用前景。