实时以太网视频传输系统的设计

2021-12-22冯云婷毛紫荆

冯云婷,张 军,毛紫荆

(天津职业技术师范大学电子工程学院,天津300222)

近年来,大部分电子设备都产生接入互联网的需求,视频的实时传输也需要向智能、网络方向发展。传统的视频传输通过电缆进行传输,缺点是只适合于区域传输[1]。由于以太网具有成本低、易与网络连接以及通信速率高等优点,因此可应用在网络远程监控等对视频实时性要求较高的场景。现场可编程门阵列(field programmable gate array,FPGA)具有灵活性强、吞吐量和集成度高等优点,且可编程逻辑资源丰富[2],能进行快速的并行运算,重复编程,性价比高,因此应用于数字信号处理、视频图像处理以及人工智能等领域。高俊岭等[3]使用OV7670摄像头采集图像,通过VGA(video graphics array)进行实时显示,实现了视频图像的采集显示,但并未使用乒乓操作和利用网线进行数据传输,因此不能进行远距离传输。韩众等[4]使用CMOS摄像头获取图像,采用乒乓式存储,实现数据的SDRAM(synchronous dynamic random access memory)存储和VGA显示,解决了图像拖影问题,但还是不能解决远距离传输视频图像的问题。吴长瑞等[5]将FPGA和PHY芯片结合,实现了UDP/IP(user datagram protocol/internet protocol)协议数据的正确发送和接收,但未实现视频图像的以太网传输。于波等[1]基于EP4CE10F17C8使用OV7725实现了以太网视频传输,实验工程未使用乒乓存储,且进行通信时采用的是MII接口,需要16根通信线,端口使用信号线过多。本文在SDRAM数字读写控制模块中使用乒乓操作,对OV7725摄像头采集的数据进行SDRAM输入输出,无缝缓冲,节约了缓存空间,采用RMII接口进行以太网模块的设计,只需7根通信线即可完成视频的实时传输。

1 以太网视频实时传输原理

视频实时传输过程分为视频数据获取、存储和传输。首先光线通过镜头传输到图像传感器,感光矩阵将光信号转变成电信号,再将信号存储为由像素点组成的数字图像,再经过A/D转换,传入DSP处理单元进行图像处理,包含图像格式转换等处理操作。转换成10 bit的数据流后,一般使用8根数据线将数据传输至FPGA芯片,再存储至SDRAM,最后通过网线传输视频信号。视频实时传输的技术指标有吞吐量、丢包率、接收帧率和传输速率。吞吐量为单位时间内传输的数据量,丢包率为丢失的数据包数量占发送数据的比率,接收帧率为每秒接收的图像帧数。其中,吞吐量、接收帧率和速率与图像清晰流畅成正比,丢包率与其成反比。对于帧率,当帧率高于10~12 fps时,人眼认为图像连贯。

实验工程主要实现对摄像头的配置、图像数据的处理及缓存、图像数据以及视频在上位机进行实时显示的功能。在系统实现中,采用Quartus II 13.0为开发环境,整体采用Verilog HDL语言实现各个模块的功能描述,并使用ModelSim软件进行联合仿真以及SignalTapⅡ工具对信号进行实时抓取,分析各个模块波形,验证其设计正确性。其中,采用的主控芯片为Altera Cyclone IV E系列的FPGA[6],型号为EP4CE10F 17C8,OV7725摄像头传感器作为采集前端,SDRAM作为数据缓存,最后通过PHY芯片与MAC层通信,进行数据输出。

系统的整体框架如图1所示,功能主要包括图像数据的接收、缓存及传输三方面[7],具体为时钟管理模块、摄像头驱动模块、SDRAM数据读写控制模块以及以太网数据通信模块。

图1 整体功能框图

摄像头驱动模块包括I2C驱动模块、寄存器配置模块以及图像采集模块;以太网数据通信模块包括UDP模块和数据封装模块。

①由IP核PLL生成I2C(inter-integrated circuit)驱动模块和SDRAM控制模块的驱动时钟,OV7725图像采集模块时钟由摄像头自带晶振产生并传入,UDP模块、图像格式配置模块和数据打包模块的驱动时钟都由外部PHY(physical)芯片传入。②由I2C驱动模块向OV7725摄像头写入寄存器配置信息,OV7725采集模块将传入的图像数据采用乒乓操作的方式暂存至SDRAM。③图像格式配置模块按照上位机显示的格式进行配置,图像数据打包模块再读取并打包SDRAM中的数据。④UDP模块通过网线将数据发送至上位机,实现视频图像的实时显示。

2 以太网视频实时传输实验方案

2.1 OV7725摄像头驱动模块

摄像头采集模块采用OV7725图像传感器采集视频数据[1],其在性能、质量及可靠性等方面满足了大部分的多媒体要求,在弱光条件下表现出色,且可在-20~70℃的温度范围内工作,支持输出最大为30万像素(640×480分辨率)的图像,能够在VGA模式下以60帧/s的速度运行[8],由用户控制输出图像的格式以及数据传输等。其中,摄像头控制寄存器的参数由I2C控制模块通过时钟信号SCL和数据信号SDA[9]引脚写入,摄像头根据寄存器的参数配置运行。SCL和SDA使用的通讯协议SCCB和I2C类似,故可使用I2C协议代替。

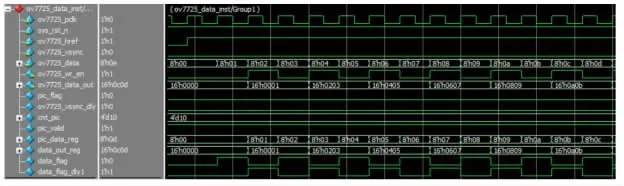

该摄像头通过2×10排针与FPGA开发板相连,I2C驱动模块的功能是实现OV7725摄像头的初始化和寄存器配置。首先,使用I2C协议代替SCCB接口协议向OV7725摄像头写入OV7725寄存器模块内部包含的寄存器配置信息,继而对摄像头进行相关配置。OV7725图像采集模块再接收摄像头传输的数据信息,并将8 bit的图像数据拼接成16 bit数据,暂存至SDRAM中。图2为由ModelSim仿真软件得到的图像采集模块仿真图,可见该模块能正确地采集数据。

图2 图像采集模块ModelSim仿真图

2.2 SDRAM数据读写控制模块

SDRAM即同步动态随机存储器,通过对电容不断地充放电来保持数据,而且数据的读写可以随机指定地址[9]。使用的SDRAM型号为W9825G6KH,存储容量为256 Mbit,内部含有4个L-Bank,地址位宽13位,数据位宽16位。在存储阵列中,一个阵列为一个L-Bank,确定数据的存储地址,需要先确定L-Bank地址,再确定行地址和列地址(先行后列),进而定位到存储单元,再实现某一存储单元数据的读写操作。

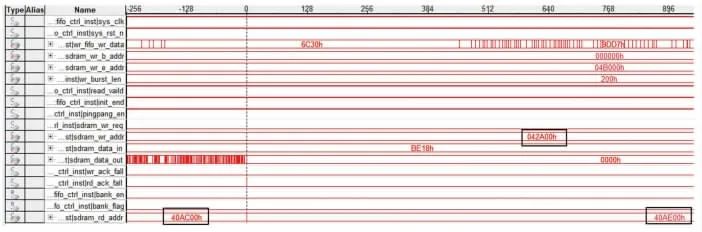

由于摄像头传感器的传输格式是640×480@60 Hz,因此每秒输出的数据量为281.25 Mbit(640×480×60×16 bit),大于百兆以太网的最大传输带宽(100 Mbit/s),所以需要SDRAM模块暂存摄像头采集到的图像数据。SDRAM读写控制模块包括SDRAM控制模块和FIFO(first in first out)控制模块。PLL锁相环为该模块提供125 MHz和125 MHz相位偏移的驱动时钟。其中,SDRAM控制模块的初始化、自动刷新、数据写、数据读以及仲裁操作,保证了数据的正确读写。FIFO控制模块包括读、写FIFO,常用于高速异步时钟之间的数据传输[10]。当OV7725模块输出的写能使信号有效时,在OV7725_pclk时钟下,将采集到的图像数据写入到FIFO控制模块的写FIFO中,当数据量达到写突发长度时,SDRAM控制模块将数据写入SDRAM中。当图像数据打包模块的读数据请求信号有效时,在外部PHY芯片传入的时钟信号二分频(25 MHz)后的时钟下,并当读FIFO的数据量小于读突发长度时,将SDRAM中的数据读出再传输至UDP模块。此外,对数据读写使用乒乓操作,其原理是当模块1被写入时,数据流从模块2读出;当模块1被写满后,再写入模块2,同时数据流从模块1读出,即切换SDRAM的读写地址,作用是使数据的读写源源不断以及使用低速模块处理高速的数据流[11]。图3为Quartus软件自带SignalTapⅡ逻辑分析仪实时抓取的FIFO控制模块波形。

图3 SignalTap波形抓取图

从图3可知,写、读地址的高2位均为Bank地址,当写Bank地址为00时,读Bank地址为01;当写Bank地址为01时,读Bank地址为00,即该模块实现了SDRAM的乒乓读写操作。

2.3 以太网数据通信模块

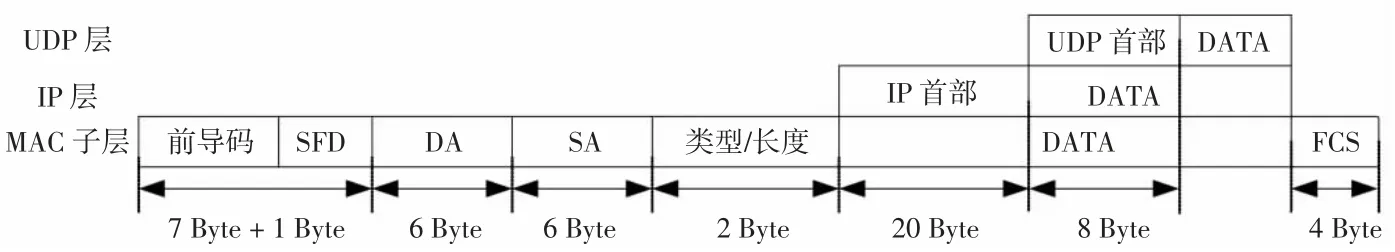

传输控制/网际通讯协议(transmissioncontrol protocol/internet protocol,TCP/IP)是现代互联网的基础和标准协议[12]。TCP/IP协议定义了网络互连的4层模型,即网络接口层、网络层、传输层和应用层[13]。其中,网络层常用的协议是IP协议;传输层包括TCP协议和UDP协议,TCP协议常用于对数据完整性、正确性要求较高的场合,而UDP协议是一种无连接的协议[14],传输速度比TCP快,占用逻辑资源少,适合实时数据的传输,所以选用UDP传输层协议。以太网通信是以数据包的形式传输。UDP数据包格式如图4所示。

图4 UDP数据包格式

以太网数据包包括前导字段、帧起始定界符、以太网帧头、IP首部、UDP首部、有效数据以及校验[15]。介质访问控制(media access control,MAC)子层位于TCP/IP协议的数据链路层的下层,是物理层和网络层的直接纽带[16],负责和物理层进行数据交接,如通过核对数据包的MAC地址和IP地址,观察是否能发送数据等。当MAC数据包发送到网络层时,只有IP首部和有效数据传入,网络层接收到数据后,将有效数据发送到传输层,包括UDP首部和有效数据。

以太网的通信还需要硬件PHY芯片[17],可以发送和接收来自MAC的数据包。通过媒体独立接口(media independent interface,MII)可以连接以太网MAC层和PHY芯片,实现以太网通信。常用的接口协议有:MII、RMII、SMII、GMII、RGMII。其中,RMII(reduced MII)接口是2位宽的数据位。实验使用的PHY芯片型号为LAN8720A,板载网线接口(RJ45),利用该芯片通过网线实现网络的通信功能,其通信速率支持10 Mbps和100 Mbps,该芯片支持通过RMII接口与以太网MAC层通信。图5为RMII接口连接示意图。

图5 RMII接口连接示意图

UDP模块包括数据发送模块和CRC-32(cyclic redundancy check)校验模块。其中,CRC校验模块由CRC Generation Tool生成。UDP模块的功能是实现以太网数据的收发,数据发送模块的功能是将数据按照以太网格式进行打包发送。首先,以太网数据包一般以32 bit为单位传输,为了保持格式一致,当图像数据打包模块的读数据请求信号有效时,读取存储在SDRAM中的16 bit的图像数据,拼接为32 bit数据,并且当图像格式配置完成时,将该数据传入UDP模块,由于RMII接口为2 bit数据接口,因此该模块需要将32 bit数据转换为2 bit数据,经CRC校验无误后,通过RMII将数据发送到PHY芯片,再将数据传输到上位机。测试结果显示发送数据与接收数据一致,说明该模块工作正常。

2.4 图像格式配置及数据打包模块

由于UDP协议性能的提高是以数据完整性和正确性为代价,因此为保证以太网传输图像数据的准确性,降低丢包带来的影响,需要遵循传输的指令协议,包括图像格式指令包和数据指令包。格式指令包由包头、设备地址、包长度、指令、图像格式、宽、高及校验位构成。其中,包头为固定数据(32’h59_48_5A_53),包长度为17 Byte,指令为数据包类型。数据指令包由包头、设备地址、包长度、指令、图像数据及校验位构成。其中,该包长度为614 412(640×2×480+12)Byte,图像数据针对的是一帧完整图像。

该格式配置和数据打包模块均工作在由外部PHY芯片传入的时钟信号二分频后的时钟下,在以太网传输模块输出的读数据请求信号有效,且在单包数据发送完成的前提下,当格式配置未完成时,图像格式配置模块生成需要配置的数据包,并通过以太网模块发送到上位机,配置图像格式;由于以太网数据包最大约为1 500 Byte,因此发送完整的图像数据包需要使用多个以太网数据包[5]。在每帧首包数据包中,图像数据之前添加包头、设备地址、包长度、指令,共10Byte(32’h59_48_5a_53_00_00_09_60_0c_02)。在每帧末包数据包中,图像数据之后添加2 Byte校验位。当格式配置完成时,图像数据打包模块将读取暂存在SDRAM中的16 bit的图像数据,按照数据指令包格式打包,拼接为32 bit的数据,传输至以太网模块,输出2 bit的数据。因此,数据读入比读出快,需要在数据打包模块中例化FIFO模块,存储需要发送的数据。通过UDP模块发送至上位机,实现视频的实时显示,仿真结果显示各个指令包的指令均正确。

3 以太网视频实时传输实验结果及分析

3.1 实验步骤

(1)对系统图像数据的采集、存储、传输各个模块进行测试与验证,通过联合ModelSim和嵌入式SignalTap工具进行仿真和调试,分析结果查看是否实现了设计模块的功能,如果未能实现其功能,需要根据仿真的波形图进行代码修改,直至能仿真出正确波形。如上文所示,经验证各个模块运行正常无误,达到预期要求,即仿真通过,最后绑定管脚编译工程。

(2)将开发板与12 V的直流电源、下载器JTAG端口、网线以及OV7725摄像头相连接,网线的另一端连接电脑端,也可与路由器进行连接,再使用另一根网线将电脑端与路由器相连。线路连接完成后打开开关为开发板上电。

(3)将代码中的地址改为与PC机相一致的IP和MAC地址,或者也可以使用广播方式,确保电脑端能够接收到传输的以太网数据。将开发板的IP地址、MAC地址与电脑端进行绑定,并配置上位机的协议类型、电脑IP地址及端口号。

(4)打开监听开关,即可接收到实时传输的视频图像。最后,打开Wireshark进行网络信号抓取。

3.2 实验结果

工程重新编译后,通过软件Quartus II 13.0向开发板下载程序文件,实时显示视频图像如图6所示。

图6 实时显示的视频图像

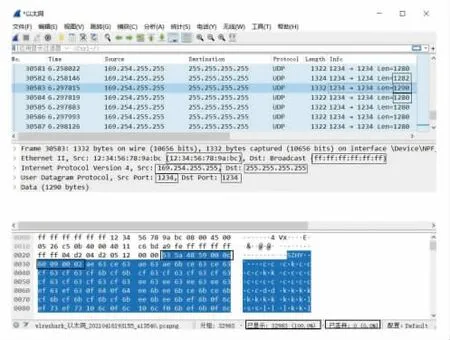

上位机将实时显示OV7725摄像头采集到的视频图像,其中摄像头的分辨率为640×480,上位机显示的视频清晰流畅,即满足实验要求,图像数据的传输速率达到5.89 MB,接收帧率为10~12 fps,吞吐量为54 Mbps。为了进一步验证其传输数据的正确性,使用Wireshark工具进行信息抓取,Wireshark抓取的数据包如图7所示。该包可以抓取网络信号、开发板和电脑的IP地址、MAC地址和端口号,以及接收的数据。普通的单包数据包为1 280 Byte,首包数据包为1 290 Byte,末包数据包为1 282 Byte,图7中抓取的是首包数据包的详细数据,其中,包头、设备地址、包长度和指令都与设置的一致。

图7 Wireshark抓取的数据包

从图7可知,Wireshark抓包的丢包率为0,不丢失图像数据信息,故该视频实时传输系统通过测试。此外,还可以将程序固化,存储到片外flash中,使开发板在重新上电后能继续工作。

3.3 实验分析

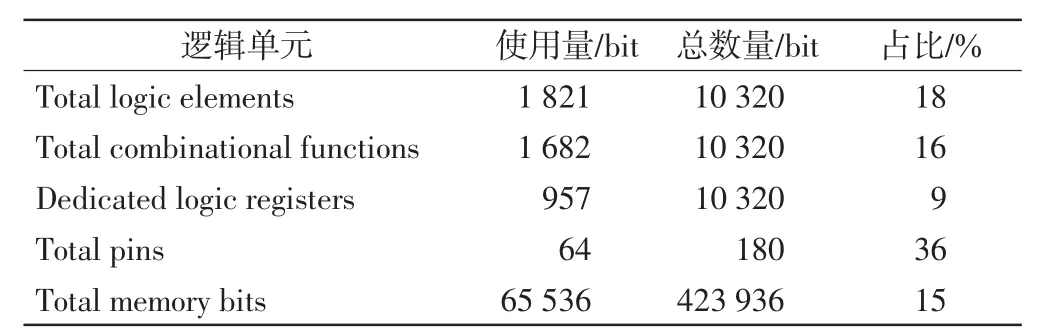

本文设计了摄像头驱动模块、SDRAM数据读写控制模块和以太网数据通信模块,在Quartus II环境中使用Verilog语言对各模块进行描述,并进行ModelSim仿真和板级验证,检验系统各模块功能的正确性,实现了对高质量视频图像的数据采集、传输和实时显示。系统实时显示的视频图像清晰流畅,满足实验要求。该系统采用乒乓操作和UDP协议进行视频数据传输,提高了传输的速度和质量,同时具有耗能低,稳定性高的优点。FPGA硬件逻辑资源消耗如表1所示。

表1 系统资源消耗统计表

从表1可以看出,使用65 536 bit的片内内存,占总片内内存的15%,没有耗费大量资源,满足硬件资源要求。

4 结语

本文利用FPGA的快速并行处理、可重复编程、片内逻辑资源丰富,以及UDP协议传输占用FPGA逻辑量少等特点,实现了基于FPGA的以太网视频实时传输系统。该系统性能稳定,硬件平台便于携带,且移植平台的主芯片的逻辑资源只要能满足该系统的占用资源,更改管脚分配即可进行移植,具有可移植性。而对于图像的接收帧率和吞吐率可通过提高CPU处理能力或更改以太网接口设计等进一步改善,还可以在该系统基础上增加对图像的算法处理,即形态学滤波、边缘检测等。该系统能够通过路由器使用网线连接PC机和板卡,增大了图像信息的传输距离,可应用于智能家居、网络监控等有视频实时传输要求的场景。