过孔残根对信号完整性的影响

2021-12-08邱小华杨鹏飞曾宪悉胡玉春

邱小华 杨鹏飞 曾宪悉 胡玉春

(惠州中京电子科技有限公司,广东 惠州 519029)

0 前言

高速PCB线路设计的目的是使得数据能够高效准确的传输,就必须要保证所设计电路的信号完整性(SI)。在高速线路中工作频率越来越高,在信号的传输过程中受多种不利因素的影响致使信号失真。内层信号线过孔时导通孔的残根(Stub)产生的寄生电容不仅会影响阻抗的大小与时延,反射也会干扰信号的传输导致损耗的增加,为得到更好的信号传输质量,一个常用的方法就是对带状线(Strip line)的信号传输孔进行背钻,将残根进行钻除或减少,从而减少寄生电容和电感对信号传输的影响。

本文主要就是从背钻对内层带状线过孔或不背钻与不同残根值时对信号传输时阻抗以及插损两个方面的影响进行研究。

1 试验板

试验采用12层电性测试板设计损耗及阻抗模块,选用低介质损耗等级材料Synamic6GX,设计2层背钻(走线L3→测量L1层与走线L11→测量L12层)来对比不同残根值与阻抗和插入损耗之间的关系。试验板结构如图1所示。采用网络分析仪(VNA),测试产品阻抗、内层带状线(Stripline)的损耗数据。

图1 试验板背钻设计示意图

2 试验方案

本次试验所使用的板材选用生益Synamic6GX,背钻设计的两个层次(L3&L11)对应残根值长度信息如表1所示。测试设备为四端口网络分析仪E5071C。L3层信号层设计在L1层测试,因此从L12层进行背钻;L11层信号层设计在L12层测试,因此从L1层进行背钻。在成品测试时依据顺序依次测试不同残根值时的阻抗及损耗数据。

表1 残根值长度

3 测试结果与分析

3.1 实测残根值情况

如图2所示,实测残根值与设计目标残根值基本上都在0~0.075 mm内,符合要求。

3.2 不同残根值对阻抗的影响

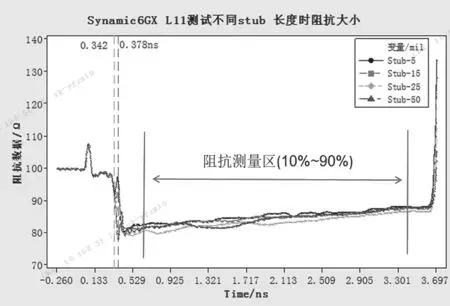

如图3、图4所示测试得到不同残根值时采用VNA测得的阻抗值大小情况,可以很明显看出在0.34~0.38 ns的范围内有阻抗值下降的情况,而且下降程度随着残根值的增加而加大。另外可以发现下降的位置也是不固定的,与残根大小也有一定的关系。从表2可以看出:L3层Stub值凹陷的最小阻抗处的凹陷点时间从0.354 ns逐渐转移到0.378 ns,L11层Stub值凹陷最小阻抗处的凹陷点时间从0.342 ns逐渐转移到0.378 ns。

表2 阻值下降最低点时间及对应阻值

图3 Synamic6GX L3层不同Stub值时阻抗测量数据

图4 Synamic6GX L11层不同Stub值时阻抗测量数据

常规阻值测量方面,取值范围不管是10%~90%还是20%~80% 均为中间的平滑区域,此区域内阻抗并不受0.34~0.38 ns阻值下降的影响,因此常规手段监控的阻抗测量输出结果并没有影响(如图5所示)。

图5 不同Stub值凹陷最大处阻抗值数据

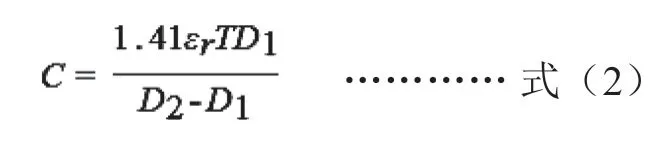

造成过孔阻抗减小现象的主要原因是随着Stub的增长,寄生电容变大,信号过孔传播时就好比高速信号的容性负载,造成信号在过孔处阻值变小,而且寄生电容也造成了信号的延迟和上升沿。其寄生电容的计算方法如式(2)[1][2]所示。

其中:C表示过孔的寄生电容,εr表示PCB的相对介电常数,T表示PCB的厚度(过孔深度),D1和D2分别表示差分阻抗线所在层过孔焊环及相邻层反焊环的直径[3]。上式中介电常数εr、差分线为同层次同设计的焊盘直径D1和D2均可看作是固定值,所以过孔的寄生电容C会随着过孔深度T值增加而变大。当Stub为过孔未背钻时的深度时,即PCB厚度时,此时寄生电容最大,对交流信号的阻碍最小,此时过孔阻抗值最小,同时的电容增加也使得信号变缓和时延的发生[3][4]。随着Stub长度的减小,过孔处连接的PCB厚度也相应减小,此时对应的过孔寄生电容将会逐渐减小,过孔处的阻抗值随之而增加。

3.2 不同残根值对插入损耗的影响

对两组材料测试254 mm(10 in )带状线(L3+L11)的损耗数据(含夹具和过孔),测试插入损耗的结果如图6、图7所示。

图6 Synamic6GX L3层不同Stub值测量损耗数据

图7 Synamic6GX L11层不同Stub值测量损耗数据

(1)可以看到L3层的Stub:0.25 mm-0.51 mm-0.76 mm-1.14 mm插损值之间的差异整体随着stub增大而增加但增幅并不明显(从0.25 mm到1.14 mm变化最大值@8 GHz时8.2%);

(2)L11层设计的Stub值:0.13 mm-0.38 mm-0.64 mm-1.27 mm也是类似情况,12GHz前Stub值从0.13 mm-1.27 mm的增幅最大值@8 GHz 4.2%,但是在12 GHz后Stub值1.27 mm的损耗明显加大,在20 GHz时超出0.13 mm设计达58.7%;从以上测试结果可以得出:不同Stub对于损耗结果有一定的影响,但是Stub值在1.14 mm范围内时20 GHz的测量范围内stub值增加对插损结果影响在10%以内。Stub值超过到达1.22 mm以上时在12 GHz频率开始就会产生明显的插损变大的情况,而12 GHz之前同样差异不明显(10%内)。

4 结论

本文通过对高速材料Synamic6GX设计电性测试板,在两个层次分别测量残根值变化对阻抗及损耗的影响,得出如下结论。

(1)残根值大小对阻抗测量时的阻值测量(范围10%~90%或20%~80%)不会有影响;

(2)残根值大小会影响过孔处的阻抗,且值越大过孔处的阻抗越小;

(3)残根值大小影响信号的上升沿和时延,且值越大时延越明显;

(4)残根值大小在1.14 mm以内对损耗几乎无影响,在1.22 mm以上时在12 GHz就会产生明显的损耗增加的问题。