高频高速通信覆铜板信号损失分析及研究进展

2021-12-02苏晓渭赵海波王成勇王冬艳盛小涛

苏晓渭,赵海波,王成勇,王冬艳,盛小涛

(1.安徽鸿海新材料股份有限公司,安徽安庆246121;2.合肥工业大学材料科学与工程学院,合肥230009)

1 引言

覆铜箔层压板(Copper Clad Laminate,CCL)简称覆铜板,是印制电路板(Printed Circuit Board,PCB)的重要基板。为了提高通讯速度,必须提高通讯频率。目前4G网络频率在0.7~3.5 GHz之间,而5G网络频率远高于4G。5G高频高速通讯领域如基站及其配套设施、交换机、服务器、通讯终端、毫米波雷达等都需要大量新型CCL[1]。

在数据传输过程中,传输速度是首要考量因素,但要达到高质量通讯的要求,通讯过程中的信号损耗和失真必须重点考虑。不断提高通讯频率,就会使原本在低频下可以忽略的信号损失变得不可忽略。本文分别讨论了高频下集成电路损耗的4类损失机理及国内研究进展。

2 集成电路损耗

高频下集成电路损耗主要由4个部分组成,如式(1)所示:

其中αT为总传输损耗,αC为导体损耗,αD为介电损耗,αR为辐射损耗,αL为泄漏损耗[2]。

3 导体损耗

3.1 导体损耗产生的原因

导体损耗是由多种因素引起的,如铜箔表面粗糙度、导体的等效电阻、趋肤效应等。CCL所用铜箔无论是电解铜箔还是压延铜箔,其原料都是电解铜,铜的纯度很高,电阻的差别较小,因此上述3个要素的综合作用是导体损耗的关键因素。

当交变电流通过导体时,会产生不断变化的磁场,而变化的磁场又会引发额外的电流,额外电流方向与原电流方向相反,在导体中心部位的磁场最强,在这个位置产生的额外电流与原电流相互抵消,最终表现出来的是电流在导体表面聚集,这种现象被称为趋肤现象。在某一深度内,电流密度为表面电流密度的1/e,该深度称为趋肤深度,可用式(2)表示[3]。

其中δ为趋肤深度,f为频率,μ为磁导率,σ为电导率。

承载电流导体的有效横截面减小,从而导致更高的等效电阻;由式(2)可知,频率越高,趋肤深度越小(浅),粗糙铜箔中高频电流和低频电流的走向对比如图1所示,对于粗糙轮廓的导体,较低的趋肤深度将导致电流跟随材料的轮廓,从而实质性地增加了传播路径的有效长度。

图1 粗糙铜箔中高频电流和低频电流的走向对比

由于趋肤效应和粗糙度的综合影响,高频下的粗糙导体损耗与平滑导体损耗就会有不同,HAMMERSTAD和JENSEN通过导体损耗修正因子Ksr将粗糙导体损耗和平滑导体损耗联系起来,建立了式(3)[4]。

αc(粗糙)为粗糙导体损耗,αc(光滑)为平滑导体损耗。

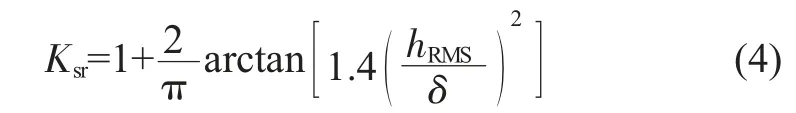

导体损耗修正因子的大小与趋肤深度和导体表面粗糙度有关,可用式(4)表示:

其中hRMS为表面粗糙度均方根,δ为趋肤深度。hRMS的大小与导体表面粗糙度有关,粗糙度越大其值越大,由式(2)可知趋肤深度是电流频率的函数,随着电流频率的增加,趋肤深度不断变小。从式(4)中可知导体损耗修正因子最大为2,即导体表面粗糙度对于导体损耗的影响最大可达2倍。

HAMMERSTAD和JENSEN建立的上述模型与实际情况稍有偏差,相关学者进行了进一步研究,引入了电感因素,为精确量化分析导体表面粗糙度与信号损失提供了更加细化的理论依据[5]。

综上所述,降低导体损耗最有效的方法还是降低铜箔表面的粗糙度,通过控制铜箔生产工艺和后续粗化参数,可以大幅降低信号损耗。

3.2 铜箔粗糙度控制

电解铜箔是硫酸铜溶液在直流作用下,筒状阴极表面电沉积金属铜并持续剥离制成原箔,再对原箔进行粗化、耐热及防氧化处理得到的[6]。其粗糙度主要受到以下3个方面影响:(1)阴极辊表面形态;(2)阴极极化作用的强弱;(3)添加剂的影响。

当钛制阴极辊的表面粗糙度为0.4 μm时,生产的铜箔表面会有明显凸起,光面色泽不均,表面质量差,而当阴极辊表面粗糙度降至0.2 μm时,生产出的铜箔相对平整。因此在生产电解铜箔的过程中要注意对阴极辊的养护和抛光[7]。

提高金属结晶时的阴极极化作用可提高晶核生成速度,易得到致密的细晶组织,一般通过以下方法提高阴极极化作用:(1)提高电流密度;(2)提高铜离子浓度,随着铜离子浓度的升高,毛面粗糙度降低,适宜的铜离子浓度为80~90 g/L;(3)适当降低溶液温度,但会影响反应速率;(4)增加电解液流速[8-9]。

电解铜箔的粗糙度也可以通过在电镀液中添加有机添加剂来控制。在电沉积过程中,电流密度和电场强度在铜箔衬底的突起峰上集聚度较高,因该峰趋于更快地生长而产生了粗糙的表面。如果某些有机分子优先吸附在表面的峰上,此时铜离子有利于在谷底进行沉积,从而生成粗糙度更低的铜箔。常见的添加剂有明胶和羟乙基纤维素等[3,6]。

压延铜箔的表面粗糙度主要与以下因素有关:一是轧辊的表面粗糙度;二是轧制油的粘度,粘度越大,油膜就越厚,阻碍了轧辊的碾压作用,使粗糙度增大;三是轧制速度,根据油膜轴承原理,轧辊转动速度越高,油膜形成的压力越大,油膜厚度越厚,也会使粗糙度增大[10-11]。

3.3 低粗糙度铜箔的抗剥离强度控制

降低CCL铜箔的粗糙度在降低信号损失的同时,将带来与半固化片压合后剥离强度下降的问题。为了保证铜箔低粗糙度的同时还要有足够的剥离强度,常规增强铜箔的附着力方法是对铜箔与树脂粘附的那一面进行粗化处理,但这样得到的表面会参差不齐,信号损失严重。国内外学者在该领域进行了深入研究。日本Namics公司的SUZUKI[12]对铜箔表面进行纳米化处理,先将铜箔进行酸洗去除氧化层,再使用专用处理溶液在铜表面形成纳米结节。经显微分析,处理后的纳米级铜箔表面较传统超低轮廓铜箔表面更加致密且均匀,纳米级结节大幅增加接触面积,纳米尺度的锚固效应使铜箔与半固化片粘合更紧密,剥离强度满足特定应用要求。SUZUKI[13]进一步利用4种不同纳米尺度的铜箔与参照组的超低轮廓度铜箔进行对比,通过与3种不同的低介电损耗的半固化片进行交叉结合实验,得出的结论是:在40 GHz下,超低轮廓度铜箔的损耗约为-0.9 dB,而几种纳米尺度铜箔的损耗接近于0 dB。

上述纳米粗化铜箔通过微观锚固技术可以获得良好的附着力,然而,为了用平坦表面的铜箔制造可靠的高密度集成电路布线,在铜和绝缘层之间还需要新的粘合技术。日立公司开发出一种新的无轮廓铜箔,表面粗糙度Rz<1.5 μm,通过微观锚固技术可获得更高的粘合强度。该技术通过对无轮廓箔片的粘合侧进行适当微观处理,获得与常规粗糙化箔片相当的剥离强度(0.8 N/mm以上)[14]。

利用对低粗糙度铜箔表面进行处理来获得较高的剥离强度的做法也是目前国内的研究热点,WANG等[15]为了使铜箔表面平滑地粘合到预浸料上,开发了一种新的表面化学处理方法,可以实现铜箔与半固化片界面的微观物理互锁。处理后样品的剥离强度更高,可达0.89 N/mm。这种表面处理方法主要就是在铜箔表面镀一层厚度约为250 nm的锡层,经测定证实剥离强度的提高主要是锡的氧化物起了作用。

在生产低频使用的CCL时,优先追求较高的抗剥离强度,即要求铜箔毛面的粗糙度更大,粗化后粗化层更大,因为低频时趋肤效应不明显,即使铜箔表面粗糙度较大也不会造成较大的损失。但在生产高频使用的CCL时,既要保证铜箔的粗糙度较小且有足够的抗剥离强度,又要在生产铜箔时控制铜箔的表面粗糙度,在铜箔的表面处理时需要提高其与树脂基体的结合力。处理方法包括铜箔表面的纳米化、建立过渡连接层以及硅烷偶联剂的使用。

(1) 灌浆材料中的块状渣体含量对化学灌浆固结效果影响明显,块状渣体占比越高(由5%提高至10%),其孔隙率相对增大,浆液扩散越容易,固结强度越高。

4 介质损耗

4.1 介质损耗产生的原因

理想的绝缘介质是不存在的。介质分子根据其中被束缚的带电粒子的分布特征分为无极分子和有极分子,无极分子中正、负电荷中心重合,相互抵消;有极分子中正、负电荷中心不重合,会构成一个电偶极矩。外加电场会使带电粒子产生微观位移,使介质中的偶极子随电场方向规则排列,称为介质极化,极化过程会消耗能量造成介质损耗。介质损耗与信号频率、介电常数及损耗正切值有关,可用式(5)表示:

其中αD为介质损耗,k表示常数,f表示信号频率,εr表示介质相对介电常数(Dielectric Constant,Dk),tan δ表示介质损耗正切值,也称介质损耗因子(Dielectric Factor,Df)。

介质中信号传播速度如式(6)所示:

其中K表示常数,c表示光速,εr表示介质相对介电常数。

从式(5)和(6)可以看出,CCL中的信号传播速度与εr(即Dk)的平方根成反比;信号传播损耗αD与频率f、Df和Dk的平方根成正比。因此,为了获得更低的介质损耗和更快的信号传播速度,需要介质有更低和更稳定的相对介电常数和损耗因子。这就是为何常规环氧树脂基CCL难以满足高频高速通信在信号损耗方面的控制要求。引入双环戊二烯基团能有效改善环氧树脂的介电性能,但由于羟基的存在,此类改性环氧树脂的极性仍然较大,导致其不能达到超低损耗的要求[16]。

祝大同[17]在2015年中国电子材料行业协会覆铜板材料分会技术论坛上的报告中讨论了高速CCL等级划分的量化指标,提出按损耗因子将高速基板材料划分为5类(等级),即所能达到低传输损耗的5个等级,高速基板分类如表1所示。

?

4.2 高频覆铜板用基板材料

非极性聚合物由于自身分子结构的对称性具有较低的相对介电常数,通常为2~3,同时介电损耗也较小。表2为常见基板材料的相对介电常数与介质损耗因子[18]。下面重点介绍聚四氟乙烯(PTFE)和聚苯醚改性研究进展。

?

PTFE分子链上的氟原子完全对称分布,偶极矩几乎为零,绝缘性能优异。体电阻可达1015Ω·m以上,相对介电常数在1.8~2.2之间。且介质损耗角小,达10-4数量级,同时介电常数和介质损耗角在1010Hz内不随频率和温度的变化而变化。由于其优异的电气性能,使其成为高频电路板优选基材之一[19]。

PTFE用于高频电路板也存在不足,表现在Z轴膨胀系数大和表面能较低。表面能较低使基板与铜箔的粘结性较差,尤其是在为了追求高速板极低的导体损失而大幅降低铜箔粗糙度时,粘结强度会大幅下降。Z轴膨胀系数与铜箔差异较大,使得受热后铜箔易脱离,集成电路板上插孔内金属引脚可能拉断。上述不足制约了PTFE在高速板领域的应用。

为了扩大PTFE的应用,需要对其进行改性。改性研究目前聚焦在3个方向:表面改性、填充改性以及共混改性[20]。

表面改性主要是通过化学处理、离子注入、等离子改性等方式使其表面活化,提高浸润性来改善粘结性能。李荣等[21]通过低温等离子体技术将PTFE薄膜与丙烯酸接枝聚合。与原始PTFE膜相比,由于丙烯酸接枝链的存在有效改善了PTFE膜的亲水性,从而有效地增强了PTFE膜表面与其他材料之间的相容性。

填充改性主要是在PTFE中添加有机或无机填料,以降低其膨胀系数和成本。常用的有二氧化硅、二氧化钛等,为了增强PTFE的力学性能,也会使用短玻璃纤维与陶瓷粉进行复合填充[22-23]。

共混改性主要是利用聚四氟乙丙烯与PTFE进行共混,可增强CCL剥离强度。张勇等[24]研究了PTFE中聚四氟乙丙烯乳液比例对CCL性能的影响,发现铜箔的剥离强度随着聚四氟乙丙烯的乳液含量增大而增大[25]。

4.2.2 聚苯醚(PPE)改性研究

PPE是一种耐高温的热塑性树脂,分子链中不含强极性基团,介电损耗小且稳定,较适合作为高频CCL的基体树脂。聚苯醚的改性是围绕着将聚苯醚的热塑性变为热固性展开的,主要有两种思路:共混改性与互穿网格技术,一是通过引入一些热固性树脂进行改性,另一个是通过引入一些活性基团,使之能发生交联而成为热固性树脂[6]。

GUO[26]等通过将活性烯丙基引入PPE,再加入苯乙烯-乙烯/丁烯-苯乙烯(SEBS)共聚物,利用SEBS出色的介电性能以及与PPE的高相容性作为增韧剂,当重量比为5∶1时,可得到高玻璃化温度和较高弯曲强度的改性产品。

MENG等[27]研究了聚苯醚与溴化环氧树脂共混制备高性能CCL,为了增强树脂间的相容性,向反应体系中加入了相容剂,制备出的产品玻璃化温度达204℃,介电常数为3.2,各方面性能要好于普通FR-4 CCL。

5 辐射损耗与泄露损耗

辐射损耗是指电路向周围环境辐射的耗散能。辐射损耗大小取决于电路设计,并与布线方式密切相关。辐射损耗还与频率、介电常数(Dk)和基板厚度有关。低速低频下辐射损耗可忽略不计,但在高速高频下,尤其是电路进入毫米波时,辐射损耗则不可忽略。Rogers公司的JOHN[28]深入研究了辐射损耗与布线的关系。3种不同的PCB布线方式如图2所示。

图2 3种常见的PCB结构[28]

微带线配置通常作为多层PCB电路的外层。带状线配置较微带配置产生的辐射损耗更小。微带和共面电路易产生辐射损耗是由于传输线的电磁场不完全存在于介质中,有一部分在空气中。而带状天线的电磁场则完全在介质中。辐射损耗可以用式(7)和(8)表示。

其中αr、h、λ0和εeff分别代表辐射损耗、基板的厚度、信号的波长和相对介电常数[28]。

从式(7)中可以看出辐射损耗与电路厚度的关系密切。较厚的电路将可能存在更多的辐射损耗。式(7)中αr与λ0的平方成反比,即在更高频率下的应用会增加辐射损耗。从式(8)可以看出,在所有其他因素不变的情况下,使用具有高介电常数基板的电路将比使用低介电常数基板的电路具有更少的辐射损耗。但较高的DK会使介质损耗增加。因此解决高频电路下辐射损耗较大的问题通常采用薄化基板的方案,而不会采用较高介电常数基板的方案。

泄露损耗是指PCB板形成微弱的接地电流而产生的损耗,但PCB板的体电阻都很大,干燥环境中,一般不会产生接地电流,所以泄露损耗可以忽略。

6 总结

对于高频CCL,铜箔的粗糙度对导体损耗有较大影响,需尽量减小粗糙度,同时需要使用表面纳米化处理或引入过渡层等方式解决剥离强度下降的问题。

介质损耗主要是由于树脂中的极性基团在电场作用下产生微观位移而导致的能量消耗和信号损失。文中给出了3种改性方案,使基板材料不含强极性基团。

高频状态下,辐射损耗会被放大,首先不同的电路设计的辐射损耗是不同的,一般带状线不会产生辐射损耗。理论上可以通过降低基板厚度和提高介电常数解决。但提高介电常数会使介质损耗增大,那么在保证强度和韧性的前提下,最大限度降低覆铜板厚度可能会成为高频覆铜板的潜在研究方向。