MOSFET器件质量与可靠性的互补表征体系研究

2021-12-02王党会郑俊娜

张 阳,王党会,郑俊娜

(西安石油大学材料科学与工程学院,西安710065)

1 引言

数十年来,单位集成电路上可容纳的晶体管数目一直较为严格地遵循摩尔定律[1],实现了高密度、低价格、高速度和低功率的超大规模集成电路(Ultra Large Scale Integration,ULSI)系统。如今,数十亿晶体管级别的处理器已经广泛地实现了商用化。最先进的工艺制程已接近3 nm,实际量产的工艺器件集中于7 nm和14 nm[2]。在尺寸不断减小、集成度不断提高、功耗不断降低的情况下,如何保持并提高器件的性能已经成为业界普遍关心的问题之一[3-5]。

作为一种广泛使用的场效应晶体管,金属-氧化物半导体场效应晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor,MOSFET)的等比例缩小引起了研究人员的关注。众所周知,当MOSFET器件的特征尺寸降低到纳米级,并接近其物理极限时,会引起一系列的可靠性问题[6-8],如短沟道效应(Short Channel Effect,SCE)、栅极隧穿效应、热载流子注入效应[9](Hot Carrier Injection,HCI)、漏极诱生势垒降低效应(Drain Induction Barrier Lower,DIBL)等。这些缺陷会降低器件的性能,引发的可靠性问题阻碍了摩尔定律的延续。

MOSFET器件的可靠性问题与其栅极界面处的缺陷密度密切相关,需要采用恰当的表征方法来确定器件的缺陷类型和缺陷密度。目前,电学测量法是栅极氧化层缺陷密度和界面态陷阱密度的常用表征方法,包括电导法、电荷泵浦法和电容-电压法等[10-12]。与电学表征法形成鲜明对比,低频噪声法能更加灵敏地表征缺陷类型和噪声起源[13]。近年来,低频噪声法以其高度的灵敏性和无损性,越来越受到重视。

对于MOSFET而言,当器件开始导通时,沟道中载流子迁移率涨落/载流子数涨落成为低频噪声的起源,能够反映载流子迁移率等输运行为。低频噪声在MOSFET器件中的应用始于1989年美国橡树岭国家实验室FLEETWOOD等的发现——低频1/f噪声对MOSFET器件中的辐照损伤极为敏感[14]。与此同时,美国耶鲁大学和亚利桑那大学也开展了1/f噪声用于MOSFET辐照损伤表征研究[15-17]。国内,西安电子科技大学杜磊和何亮教授课题组的低频噪声研究方法也取得了重要进展,应用于DC/DC变换器和功率VDMOS的筛选评估中[18-20]。作为一种有效而敏感的表征技术,如何在新型MOSFET器件中建立普适的低频噪声模型,并将低频噪声的起源与电子元器件中的缺陷和电学参数等关联起来,成为后摩尔时代低频噪声应用和发展的关键问题之一。

为了有效抑制栅极泄漏电流,高介电常数氧化物(如Al2O3、ZrO2、HfO2等)已 经 在 新 型 栅 极 堆 栈MOSFET器件中代替了传统的SiO2[21-22],但同时,高k介质引起的电子元器件质量与可靠性问题也愈发突出。研究表明,当栅氧化层的厚度每降低0.2 nm,栅极泄漏电流将增加一个数量级。本文通过对插入Al2O3帽层结构的nMOSFET进行电学测试和低频噪声测试,并对器件的阈值电压、栅极泄漏电流、亚阈摆幅、低频噪声的起源、电流噪声功率谱密度以及栅氧化层中的缺陷密度等进行系统的研究,建立了MOSFET器件的电学方法和低频噪声方法的互补表征体系,可以较为全面地对MOSFET器件的质量与可靠性进行表征。

2 实验与测试

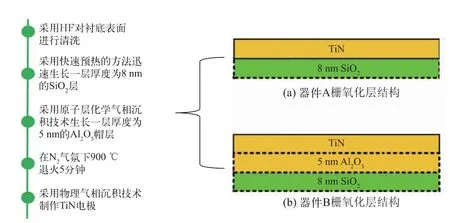

实验测试器件在比利时微电子中心(Interuniversity of Microelectronics Center,IMEC)完成生长和测试(电学特性测试和低频噪声测试)。MOSFET器件生长在厚度为200 mm的p型硅衬底上,并采用HF对衬底表面进行清洗;之后,采用快速预热的方法迅速生长一层厚度为8 nm的SiO2层;接下来,采用原子层化学气相沉积技术(Atomic Layer Chemical Vapor Deposition,ALCVDTM)生长一层厚度为5 nm的Al2O3帽层,并在N2气氛条件下900℃退火5 min;最后,采用物理气相沉积技术制作TiN电极,nMOSFET器件的生长工艺和栅氧化层结构如图1所示。沟道参数W/L=1 μm/10 μm,其中器件A为无Al2O3帽层结构的nMOSFET器件,器件B增加了厚度为5 nm的Al2O3帽层结构的nMOSFET器件。电学性能测试采用HP4156B半导体测试分析仪进行,低频噪声测试方案如下:

图1 nMOSFET生长工艺流程

(1)将器件置于纳米探针台上,在室温下连接器件的源极、栅极和漏极,源极接地,源/栅电压范围为0~2.0 V,步长为0.03 V,设定漏极电压为50 mV;

(2)源/漏极电压设定范围为0~1.5 V,步长为0.02 V;

(3)室温下,栅极电流依次设为20 nA、30 nA、50 nA、100 nA、200 nA、300 nA和500 nA时,测试MOSFET器件的输入输出电学特性。

3 实验结果及讨论

3.1 MOSFET器件的电学特性

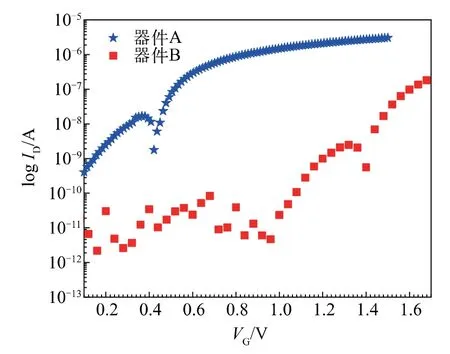

MOSFET器件的I-V转移特性曲线以漏源电压VDS为参变量,测量漏极电流ID和栅源电压VG间的函数关系。曲线的斜率定义为跨导,用gm表示,表征VG对ID的控制作用。图2为室温下器件A与器件B的I-V转移特性曲线(VDS=50 mV)。

图2 室温下测试器件的I-V转移特性曲线

阈值电压Vth是重要的电学参数之一,给出了使半导体表面达到强反型时所需的栅压,是区分MOSFET器件导通和截止的分界点。阈值电压一般由3部分组成,可表示为:

式(1)、(2)中VFB为半导体的平带电压;Vox为栅氧化层上的压降,φs为半导体表面耗尽层上的压降,φF为半导体费米势。阈值电压与金半接触电势差、氧化层中电荷密度、单位面积栅氧化物电容和衬底掺杂浓度等因素有关。文献[23]分别对长沟道MOSFET阈值电压模型和短沟道高k栅介质MOSFET阈值电压模型做了详细的分析。在高k栅介质MOSFET中,边缘场效应是影响MOSFET阈值电压的新现象[24]。短沟道效应、热载流子效应和漏极诱生势垒降低效应等都会导致阈值电压漂移和退化[25-26],最终对器件性能造成严重影响。根据图2所示的I-V转移特性曲线,使用二阶求导法提取了器件A与B的阈值电压Vth分别为0.42 V、1.52 V。器件B栅极结构中Al2O3帽层的插入有效调制了阈值电压。

众所周知,随着MOS器件尺寸越来越小,栅极关态泄露电流成为影响MOS器件性能的重要参数。较高的栅极关态电流会对器件的开关性能带来严重的影响[27],不仅会增加功耗、影响导通特性,而且会降低可靠性[28]。若MOSFET器件栅氧化层中电场强度较大,电子隧穿进入栅氧化层,形成栅隧穿电流。隧穿电流不仅加大了电路静态功耗,还会造成MOSFET器件的阈值电压发生漂移。

根据图2提取的栅极关态电流如图3所示。从图中可以看出,器件A栅极关态电流的大小约为4×10-10A,器件B栅极关态电流的大小约为1×10-11A。器件B的数值低于器件A,表明Al2O3帽层能有效地降低栅极关态泄漏电流。

图3 室温下测试器件的栅极关态电流

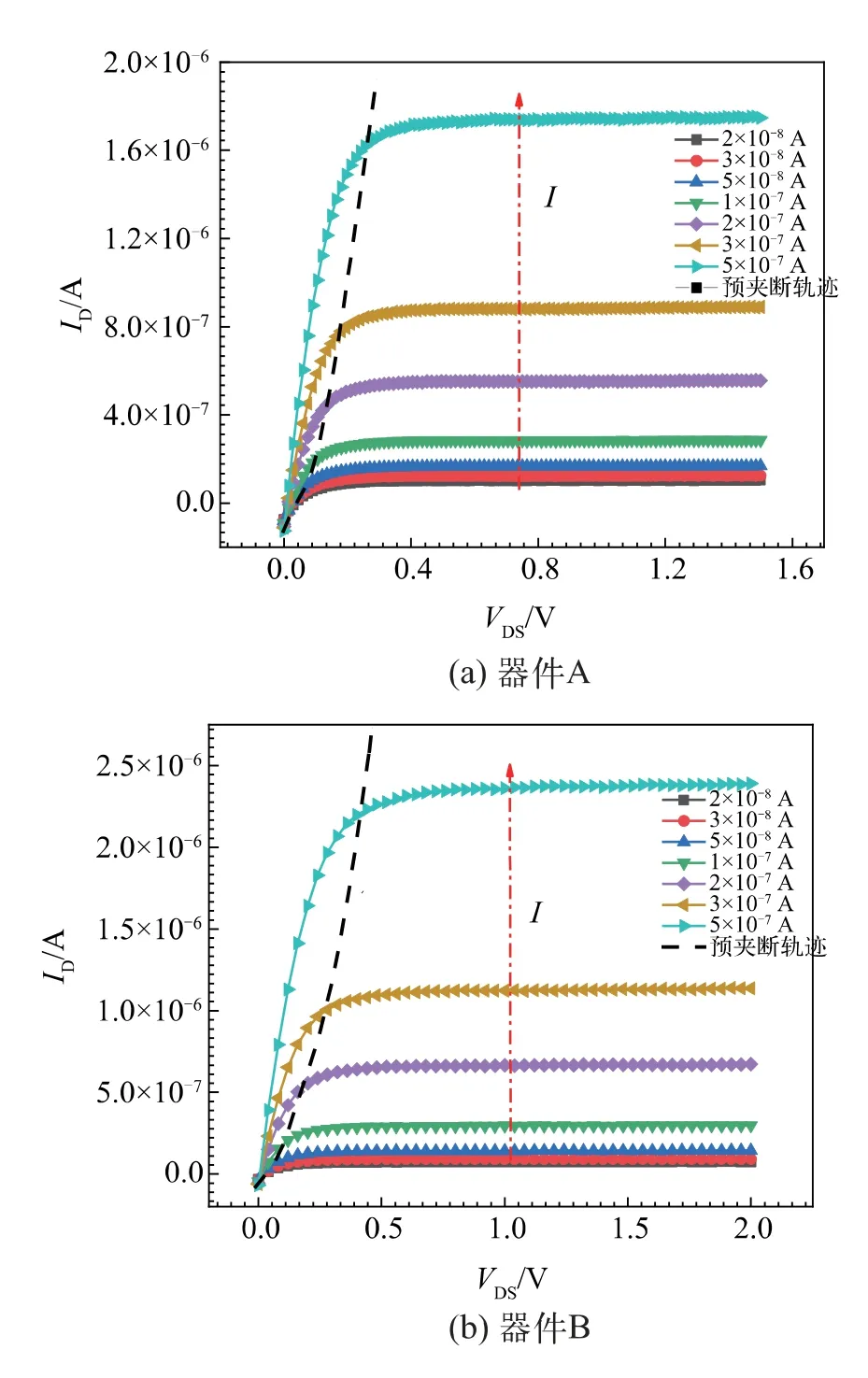

MOSFET器件的输出特性也称为漏极特性,即当VG>VT且恒定时漏极电流ID随漏源电压VDS变化的规律。图4给出了nMOSFET器件的输出特性曲线。从图4中可以看出,器件A与B均具有较好的输出特性,但器件B的输出功率更高。

图4 室温下测试器件的I-V输出特性曲线

亚阈值区用于描述MOSFET器件的导通特性和截止特性。亚阈值摆幅(Subthreshold Swing)又称为S因子,是表征MOSFET开关器件的重要性能参数。它表示漏极电流ID改变一个数量级所需的栅压摆幅,S越小,器件的导通截止转换就越容易,开关特性越好[29]。其定义如公式(3)所示:

式(3)中m=1+(Cs/Cins),其中Cs和Cins分别为沟道半导体电容和栅极电容密度。图5为log10ID和栅极电压VG关系图。根据图5和式(3)计算得到器件A的亚阈值摆幅约为35 mV/dec,器件B的亚阈值摆幅约为54 mV/dec。两者均小于室温下的理想值(60 mV/dec),这表明器件A与B均具有良好的开关性能。

图5 室温下测试器件的log10(ID)和VG关系

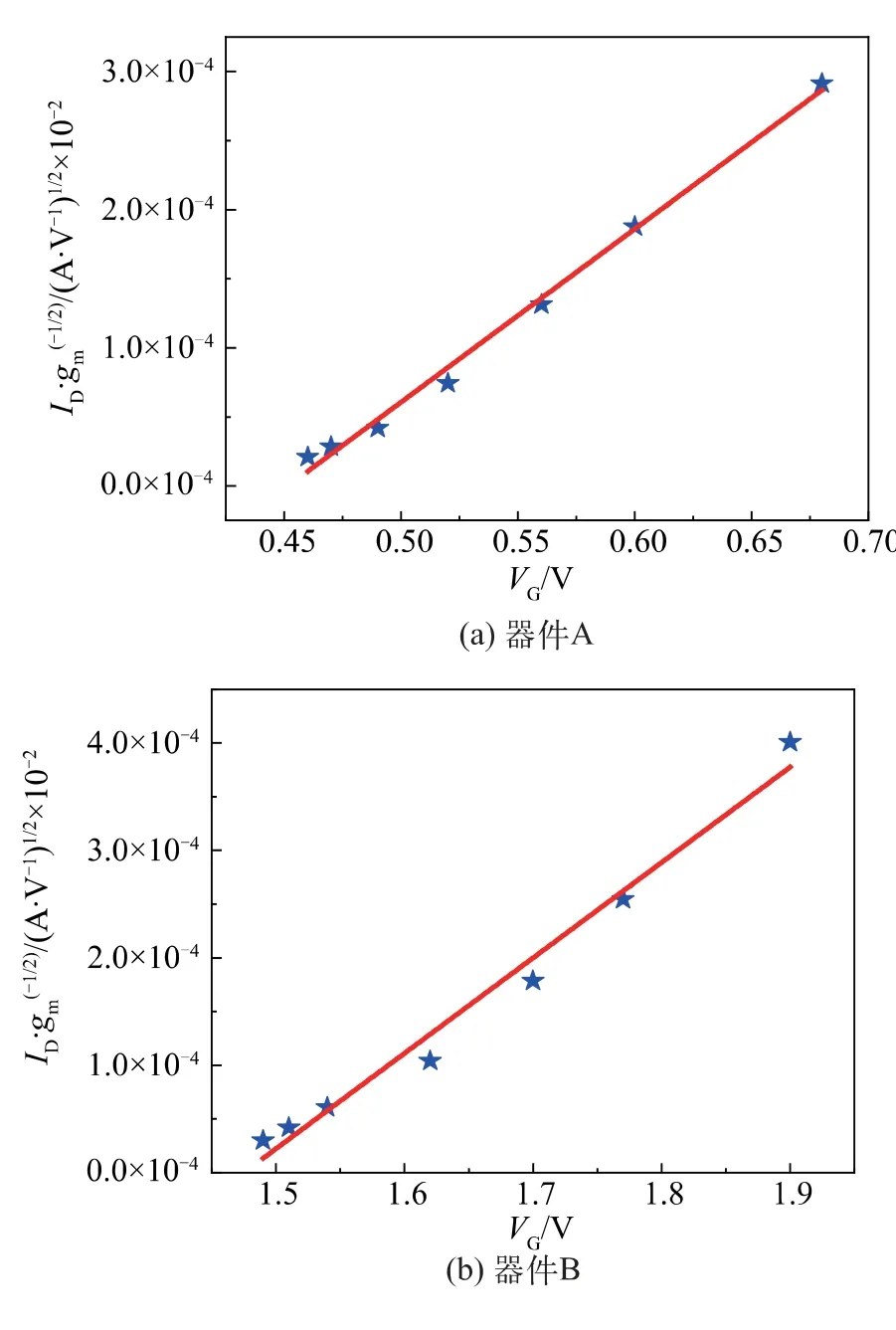

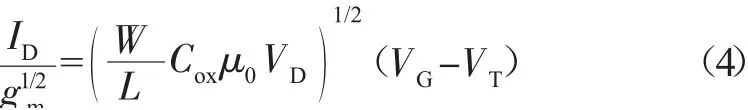

载流子迁移率是衡量半导体导电性能的重要参数,Y-函数法作为提取载流子迁移率μ0的有效方法受到了广泛认可[30],其基本原理如式(4)所示。图6展示了器件A与B的ID·gm(-1/2)与栅极电压VG的关系图。从图6中可以看到,ID·gm(-1/2)与VG之间具有良好的线性关系。根据式(4),器件A与B的载流子迁移率分别为723 cm2/V·s和365 cm2/V·s。器件B的迁移率小于器件A,这可能是由于Al2O3帽层的插入增大了阈值电压。同时,栅极氧化物界面处引入了陷阱,导致载流子在界面处的散射几率增大,从而降低了迁移率。

图6 室温下测试器件的ID·gm(-1/2)与栅极电压VG关系

图7 对迁移率衰减系数θ进行了拟合,根据式(5)拟合的器件A与B的θ值分别为0.048、0.054,这与文献[30]报道的结果是一致的。

图7 室温下测试器件的{ID/[gm·(VG-VT)]-1}和(VG-VT)关系

3.2 MOSFET器件的低频噪声特性

为了研究MOSFET器件的低频噪声特性,分别在10 nA、100 nA和3000 nA的电流偏置下对nMOSFET的电流噪声进行了测量,测试结果如图8所示。

图8 室温下测试器件的电流噪声功率谱密度与频率关系

从图8可以看出,随着漏极电流逐渐增加,器件A和B的电流噪声功率谱密度增加,所有曲线都表现出良好的1/f特性。根据电子元器件中的低频噪声理论[13,31-32],MOSFET中的低频1/f噪声来源于载流子数涨落模型和载流子迁移率涨落模型。式(6)通常用来探究低频噪声的起源机制[33],若SID/ID2与(gm/ID)2随漏极电流ID呈线性变化,低频1/f噪声来源于载流子数涨落模型;反之,存在附加的迁移率涨落模型,采用式(6)进一步探究了低频噪声的起源机制,室温下测试器件的SID/ID2和(gm/ID)2的相关性如图9所示。

式(6)中αsc为库伦散射系数,μ为低场迁移率,Cox为等效氧化层电容密度,SVGfb为栅极平带电压噪声。

从图9(a)中可知,器件A在ID>1×10-7A时,SID/ID2和(gm/ID)2变化趋势基本平行,证实了载流子数涨落机制[33-34],沟道中的自由载流子将被氧化物陷阱动态地俘获并释放,从而引起界面氧化物电荷的变化;在ID<1×10-7A时存在明显偏差,说明存在附加的迁移率涨落模型,在这种情况下,氧化物陷阱可通过调制库伦散射机制影响迁移率[35]。从图9(b)中可知,器件B也具有类似的噪声起源机制,在ID>5×10-8A时,SID/ID2和(gm/ID)2趋势基本平行,引起界面氧化物电荷的变化;ID<5×10-8A时,存在明显偏差。

图9 室温下测试器件的SID/ID2和(gm/ID)2的相关性

此外,采用低频1/f噪声还可以确定栅极氧化层中的缺陷密度,其原理如下。

根据低频噪声理论,栅极等效输入栅极电压噪声SVG与VG之间的关系可以用式(7)所示[35]。

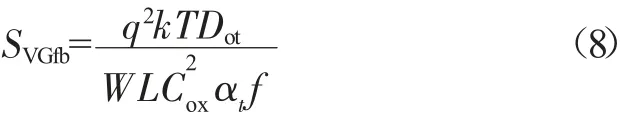

该噪声与氧化物陷阱密度Dot成正比,见公式(8)[33-34]。

其中k为玻尔兹曼常数,T为热力学温度,q为电子电荷,αt为隧穿常数。从式(6)的斜率和截距得到库伦散射系数和平带噪声,进而求出氧化物陷阱密度Dot。通过式(7)可以得到器件平带电压下的栅极电压噪声SVGfb。图10为SVG1/2和ID关系图,曲线截距表示SVGfb,提取器件A与B的SVGfb分别为8.1×10-7V/rtHz和1.69×10-6V/rtHz。由于SVGfb和氧化物陷阱密度Dot成正比,器件B中的Dot大于器件A,表明器件B的迁移率小于器件A,这是由氧化层陷阱所致。

图10 室温下测试器件的SVG1/2和ID关系图

4 结论

本文在室温下对nMOSFET器件的电学性能和低频噪声进行了测试,并对阈值电压、栅极关态泄漏电流、亚阈摆幅、电流噪声功率谱密度、低频噪声的起源以及栅极氧化物中的缺陷密度等进行了系统的研究。通过分析低频1/f噪声的行为,研究了低频噪声的起源和缺陷类型,建立了MOSFET器件质量与可靠性的互补表征体系。结果表明,栅极结构中插入5 nm Al2O3帽层能有效调制器件的阈值电压,降低关态泄漏电流,并提高了输出功率;但由于Al2O3层的引入,在栅极氧化物界面处引入了陷阱,增加了载流子的散射几率,从而降低了沟道中的载流子迁移率。本文的研究结果为量子尺寸降低效应引起的电子器件质量与可靠性的表征提供了一种简单且有效的方法。