基于40 nm CMOS 工艺的电荷泵锁相环设计

2021-12-01唐重林杨发顺

路 哲,马 奎,2,唐重林,杨发顺,2,梁 蓓,2

(1 贵州大学 大数据与信息工程学院,贵阳 550025;2 贵州省微纳电子与软件技术重点实验室,贵阳 550025;3 牛芯半导体(深圳)有限公司上海第一分公司,上海 201210)

0 引言

如今,高速数据传输系统已成为各大研究机构、高校、企业研究的焦点[1]。高速SERDES 接口芯片作为高速数据传输系统的一部分,主要包括3 部分:发送端(transmitters,TX)、接收端(receive,RX)以及锁相环(Phase Locked Loop,PLL)。锁相环负责SERDES 各个模块所需要的时钟信号,并管理这些时钟之间的相位关系[2]。SERDES 的一个重要性能指标是抖动(jitter),因为抖动直接和误码率(BER)相关[3]。锁相环的相位噪声是SERDES 抖动的重要来源。也可以说锁相环的相位噪声性能决定着SERDES 的误码率水平。

本文设计的锁相环主要应用于SERDES 接口芯片中,因此对锁相环进行噪声的研究与分析尤为重要。要保证SERDES 内部系统工作时信号传输的稳度与精度,就要求锁相环的输出信号时钟稳定,尽量减少噪声干扰,降低输出信号的抖动[4]。因此需要设计出一种低噪声锁相环,以满足SERDES 对时钟信号低误码率的要求。

为了尽可能减小面积,且优化输出噪声,一般采用三阶锁相环,即LPF 内部为二阶。这样既节省了面积又滤除了频带内的高频噪声,达到低噪声、低抖动的目的。为了扩大锁相环的输入输出频率范围,最有效地方法是增加输入输出分频器[5]。本文的CPPLL 包含3 个分频器,在不含输入输出分频器的情况下,本文的输入范围为25~200 MHz,输出范围2.4~4 GHz。根据不同规格与需求,通过增减分频器来达到所需的频率范围。为了减小面积与输出抖动,振荡器采用环形振荡器(ring vco)。为了简化电路,延迟单元采用负阻结构。通过优化参数以达到降低振荡器噪声,从而降低锁相环整体噪声的目的。

1 电荷泵锁相环的整体结构

如图1 所示,电荷泵锁相环(CPPLL)由鉴频鉴相器(PFD)、电荷泵(CP)、环路滤波器(LPF)、压控振荡器(VCO)、分频器(Divider)等模块构成。

工作原理分析如下:

首先给锁相环的鉴频鉴相器提供一个参考输入信号,此信号和通过环路分频器后的反馈信号相比较,输出一个和两者相位差成正比的电压信号。该电压信号控制后级电荷泵电路中开关的打开或者关断状态,电荷泵把输入的电压信号转换为输出电流信号。该电流信号会通过环路滤波器中电容的充放电机制,将电流信号再转换为电压信号。这时的电压通过控制压控振荡器的振荡频率,实现锁相环输出频率的调节。锁相环的输出频率通过分频器后,再将反馈频率和输入参考频率进行比较,重复上述过程,直到输入参考频率和环路反馈频率同频同相,这时称锁相环锁定。

2 锁相环模块电路设计与仿真

CPPLL 是数模混合类电路,其中分频器、鉴频鉴相器属于数字模块,而电荷泵、低通滤波器、压控振荡器则属于模拟模块。

2.1 鉴频鉴相器(PFD)

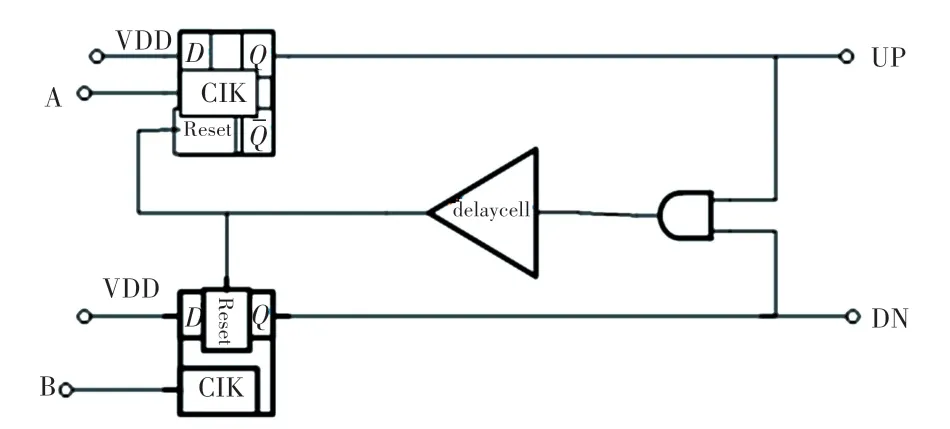

本文所采用的PFD 为常用的可以减小“死区”效应功能的鉴频鉴相器。“死区”是指锁定之后,UP/DN 信号没有输出。此问题,一般采用图2 的结构形式来解决。

图2 减小死区效应电路示意图Fig.2 Schematic diagram of reducing dead zone effect circuit

图中:A 为Fref 时钟信号,B 为Fbk 反馈时钟信号。经过DFF,产生一个RESET 信号,将DFF 重置,使得每隔一个周期,DFF 将至少输出一个脉冲信号,脉冲宽度取决于RESET 的延迟时间[6]。设计中,加入一个延迟单元来减小死区,可以通过增减延迟单元来控制脉冲宽度。

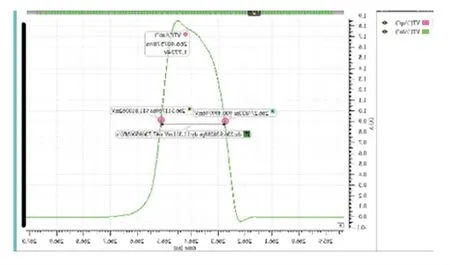

PFD 死区时间仿真结果如图3 所示,仿真验证得到鉴频鉴相器的死区时间,在典型工艺角下只有180 ps。

图3 鉴频鉴相器的死区时间Fig.3 Dead time of the frequency discriminator

2.2 电荷泵(CP)

本文采用的电荷泵如图4 所示。

图4 电荷泵电路原理图Fig.4 Schematic diagram of charge pump circuit

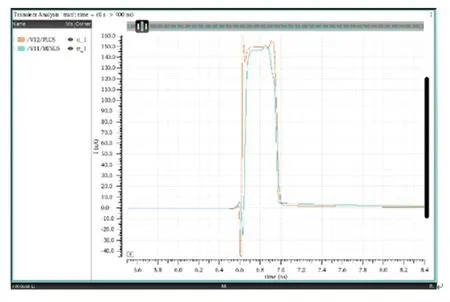

在图4 中,电流镜采用了可以大大的增加输出阻抗共源共栅结构(M5、M8与M9、M14),增加电流匹配性,可以减小由于沟道长度调制效应带来的误差。由于使用了运算放大器,使得M6的漏端电压被钳位,M6的漏端电压近似等于M12的漏端电压。如果电流源对应的晶体管的尺寸相等,则有I3=I4,又因为I1=I3,且I1=I2,所以I2=I4。电路中通过多种方法来提高电流匹配性,因此电流匹配性很高,静态电流匹配可以达到99%以上,动态电流匹配也可以达到90%以上。另外,本结构在电流镜像管和开关管之间采用并联MOS 电容,来防止电荷泄露和时钟馈通[7]效应,以进一步减小电流失配和电荷杂散等不利因素,提高电流的匹配。电荷泵电流不匹配的瞬态仿真波形如图5 所示。

图5 电荷泵电流不匹配的瞬态仿真波形Fig.5 Transient simulation waveform of charge pump current mismatch

仿真结果表明:在全工艺角条件下,电荷泵电流的瞬态失配小于7%。

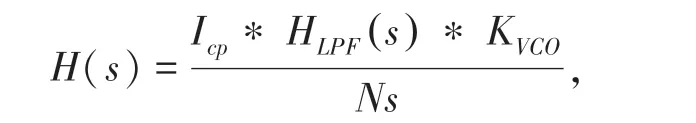

2.3 压控振荡器(VCO)

压控振荡器通常采用单端延迟单元,但这种结构电源抖动会对其产生较大干扰。为了抑制电源噪声,本文使用的差分结构的环形振荡器,由3 个延迟单元组成。差分结构VCO 的另外一个好处是,可以由任意级数的延迟单元构成,而传统的单端输出的延迟单元则只能使用奇数级来产生振荡[8]。

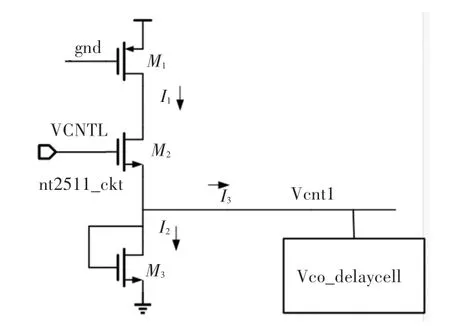

本文压控振荡器的控制电压相较于文献[9]采用的V2I 结构,使用了超低阈值的native MOS 管来进行优化,使压控振荡器可以工作在VCNTL 电压很低的情况下控制频率,理想情况下可以达到0 附近。在电路设计中,M2管采用大尺寸沟道长度和沟道宽度,达到减小相位噪声的目的。压控振荡器的电路框图如图6 所示,其工作原理如下:

图6 压控振荡器的电路框图Fig.6 Circuit block diagram of voltage controlled oscillator

首先VCNTL 开启M2,同时M1、M3自启动打开,形成一个总电流I1。当VCNTL 变化时,总电流I1发生变化,同时I2基本不变,所以I1的变化量全部都转化为I3的变化量。即转化为延迟电路的电流变化。通过延迟电路电流的变化,可以改变电路的延迟时间[5]。电路的延迟与压控振荡器的振荡频率直接相关,即可改变压控振荡器的频率,达到电压控制频率的目的。VCO 的调谐曲线如图7 所示。

图7 VCO 的调谐曲线Fig.7 Tuning curve of VCO

根据图8 的仿真结果表明:在偏离中心频率1 MHz处的相位噪声为-91.8 dBc/Hz。

图8 压控振荡器相位噪声仿真波形Fig.8 Voltage- controlled oscillator phase noise simulation waveform

2.4 低通滤波器(LPF)

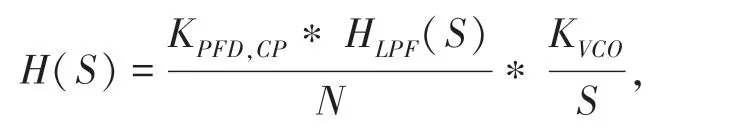

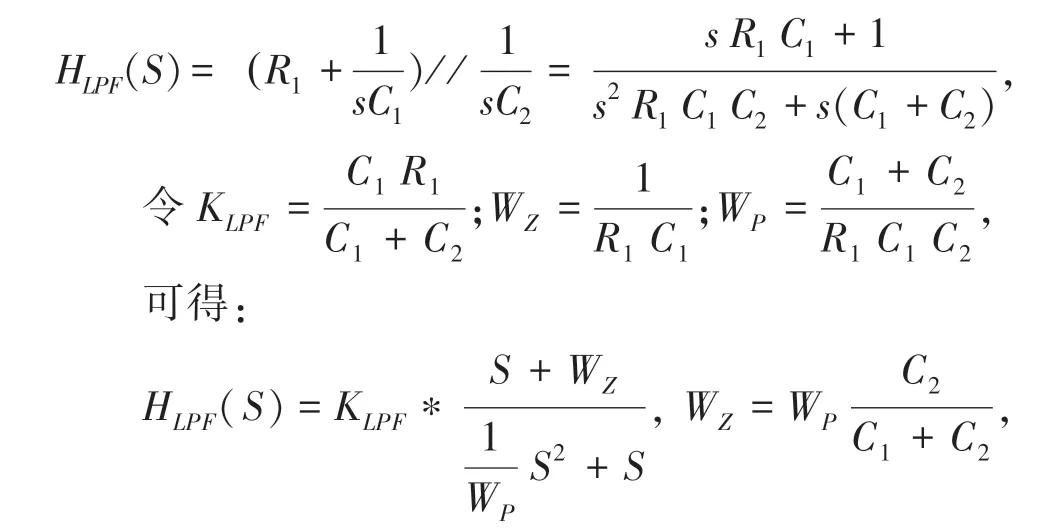

滤波器是整个PLL 环路中非常重要的组成部分。环路的稳定性、带宽等多项指标与低通滤波器密切相关。整个PLL 环路的开环传递函数可以表示为:

其中,kPFD,CP为PFD 和CP 的增益乘积;HLPF为LPF 的传递函数;N为环路分频器的分频比;kvco为VCO 的增益。将表达式代入之后可以得到开环增益为:

显然,当S =wn时,H(S)=1,此时的wn称为环路带宽。

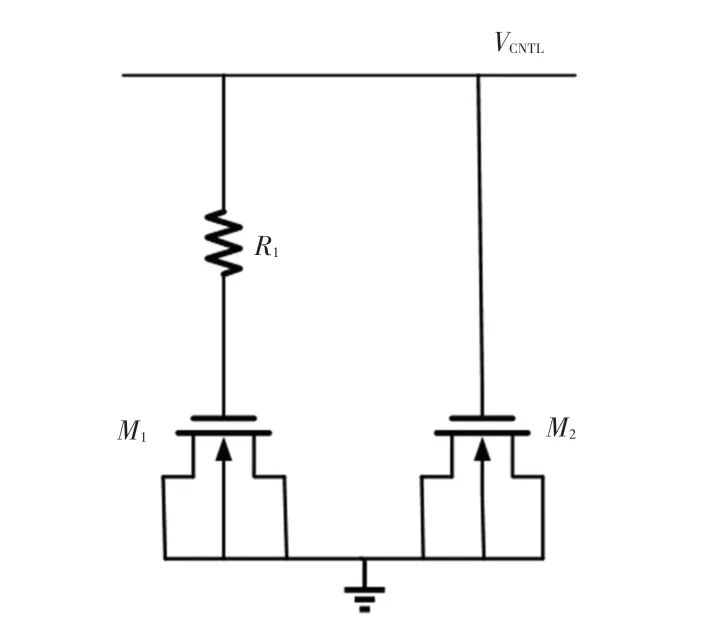

LPF 采用无源形式,结构如图9 所示。

图9 低通滤波器电路结构图Fig.9 Low-pass filter circuit structure diagram

其传递函数可以表示为:

系统的相位裕度为:

对wn求偏导,令其等于0 可得:

带入H(S)=1,通过解方程可以得到LPF 各变量:

本文综合锁相环电路的稳定性、面积和具体应用环境,滤波采用无源二阶低通滤波器。电阻选用多晶硅电阻,该类电阻在电路设计中用途很多且精度也较高。在电容的选用中,MIM 电容虽然精度较高但占用的版图面积过大。所以采用工作于强反型状态NMOS 管的MOS 电容[10]。其在版图中所占用的面积可以大大减小,且精度也较高。

图9 为本文所设计的二阶环路滤波器的电路图。其中M1管和M2管分别代表电容C1和C2。在只有一个电容C1的情况下系统不够稳定,加入R1在环路中引入一个零点,用来提高系统的相位裕度,使系统稳定。引入电容C2来抑制控制电压上的跳动[11]。

3 系统仿真结果

本文采用SMIC 40nm CMOS 工艺,对所设计的锁相环电路进行了仿真验证。主要验证压控振荡器控制电压纹波和抖动眼图,以及锁相环抖动眼图。

在TT_65_NV 下,输入频率为Fin =100 MHz、电荷泵电流ICP =150 uA、低通滤波器电阻R =1.5 kohm、电容C1=200 p、C2=10 p、分频器的分频比DIV_FB =40。控振荡器的输出频率Fvco =4 GHz,经后置分频器的输出Fout =500 MHz。

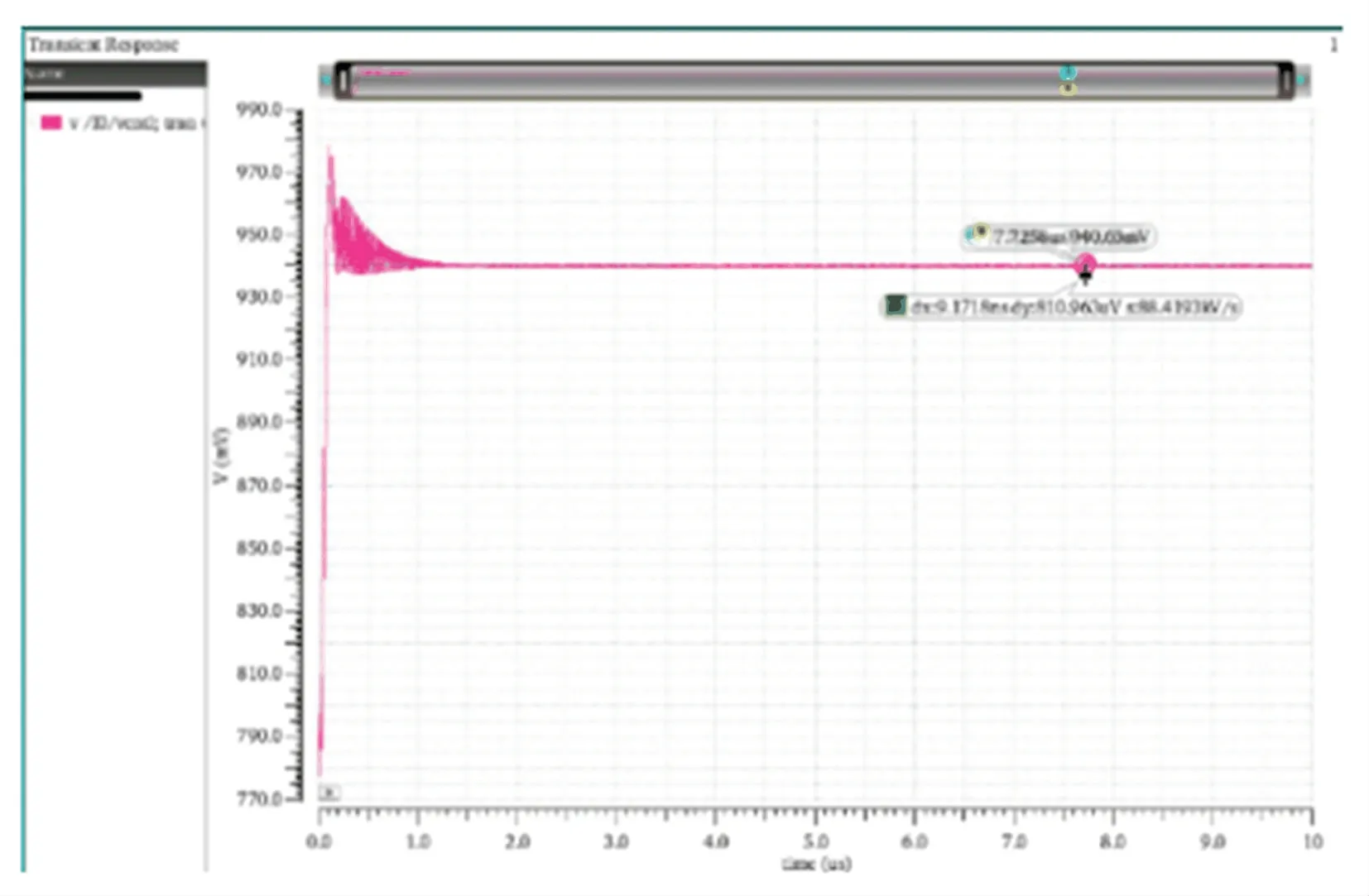

由图10 可知,压控振荡器上的电压纹波为810 μV(小于1 mV)。压控振荡器输出波形的抖动眼图如图11 所示。

图10 压控振荡器控制电压上的纹波Fig.10 Ripple on the voltage controlled oscillator control voltage

图11 压控振荡器输出波形的眼图Fig.11 Eye diagram of the output waveform of the voltagecontrolled oscillator

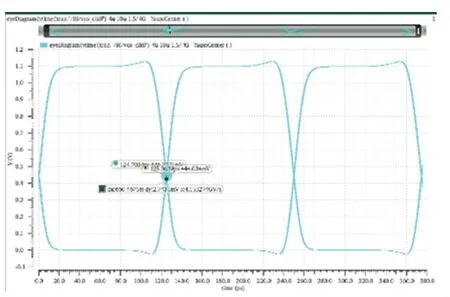

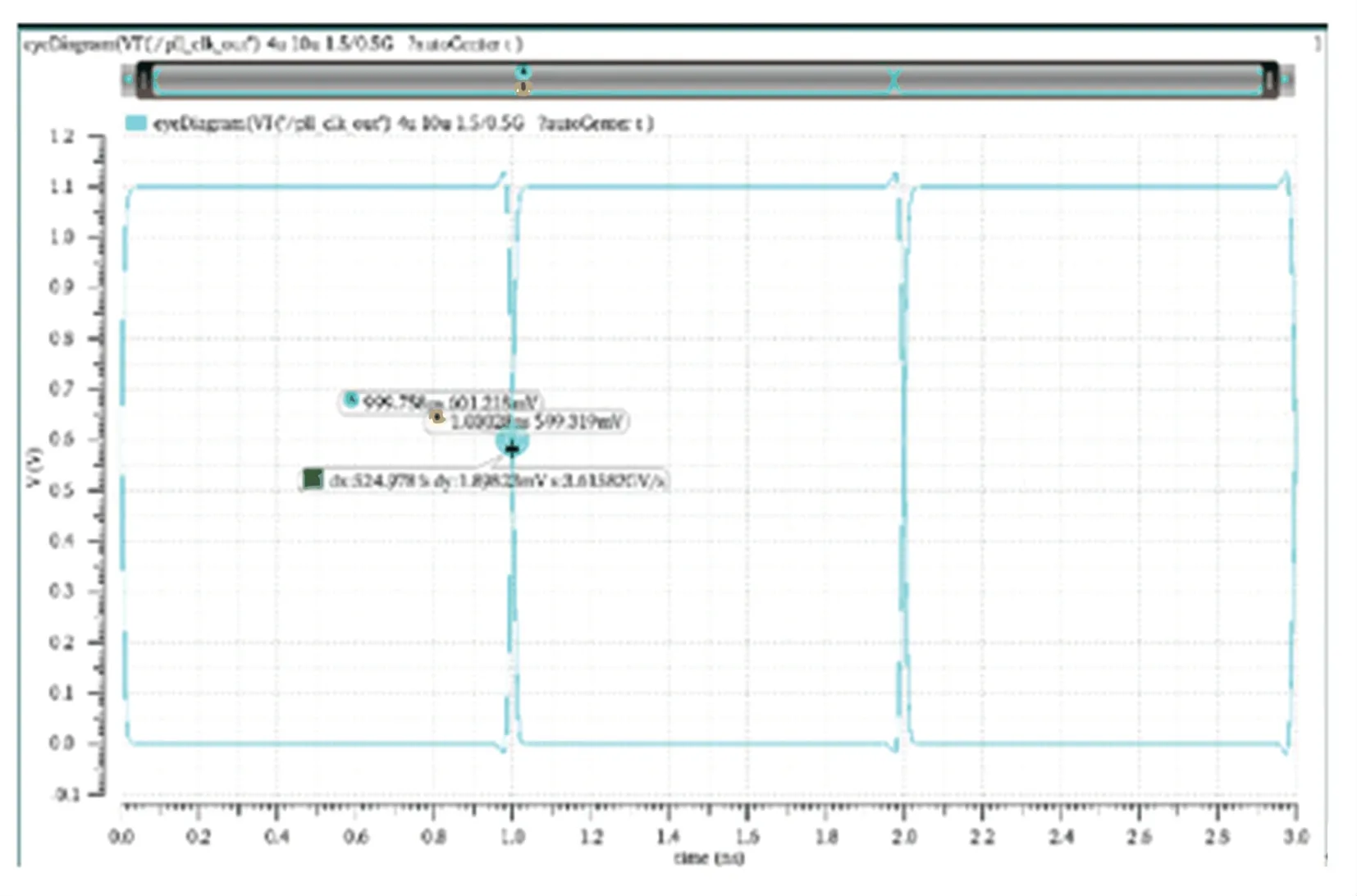

由图11 可知,此压控振荡器输出波形眼图的抖动为0.66 ps。锁相环输出波形的眼图如图12 所示。

图12 锁相环输出波形的眼图Fig.12 The eye diagram of the output waveform of the phaselocked loop

锁相环总的抖动为各模块单独抖动的加权和。从图12 可以看出,锁相环总的输出波形眼图的抖动为0.53 ps。满足在典型情况下锁相环低抖动的性能要求。

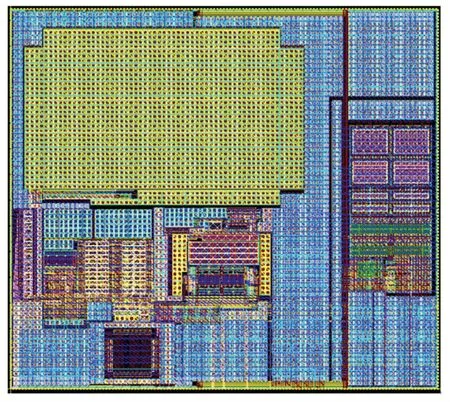

4 版图与后仿真

电路基于SMIC 40 nm 工艺,其版图使用Cadence公司的版图工具Virtuoso 进行设计。使用Calibre进行DRC 和LVS 验证,提取寄生参数进行后仿真验证[12]。锁相环整体版图如图13 所示,芯片尺寸为0.4×0.45 mm。图14 和图15 分别为压控振荡器的输出电压杂散仿真和锁相环的抖动眼图仿真结果。从仿真结果中可以看出压控振荡器的输出电压杂散小于1 mV,锁相环的绝对抖动小于1 ps。

图13 锁相环整体版图Fig.13 The overall layout of the phase-locked loop

图14 压控振荡器的输出电压杂散仿真结果Fig.14 The output voltage spur simulation results of the voltagecontrolled oscillator

图15 锁相环的眼图仿真结果Fig.15 Eye diagram simulation results of the phase-locked loop

5 结束语

本文基于SMIC 40 nm 工艺,通过对压控振荡器的控制电压方式进行改进,简化了压控振荡器电路,优化了VCO 的相位噪声。

完成了锁相环各模块电路的结构和参数设计以及版图设计,提取寄生参数并进行了后仿真。由仿真结果显示,本文所设计的锁相环的锁定时间小于2us,抖动小于1ps,功耗小于20 mW。