便携式冲击电流测量装置的设计及测试

2021-11-06施政远李文婷徐晓东

施政远,徐 雁,李文婷,徐晓东

(1.华中科技大学电气与电子工程学院,湖北武汉 430074;2.中国电力科学院计量中心,湖北武汉 430074)

0 引言

冲击电流测量应用广泛。在雷电监测领域,冲击电流传感器可以监测雷电流波形,提供雷电流安全防护;在电力系统中,故障冲击电流的可靠监测可为电力系统的设备与人员安全提供保障。

冲击电流具有频带分布宽、幅值大、不确定度高等特点[1],这对其测量带来了挑战。传统冲击电流测量采用分流器,但分流器需接入主回路,没有电隔离,易对测量回路产生干扰,而且分流器因集肤效应和温度变化带来的参数变化也影响测量精度[2-3]。近年来,磁光法等冲击电流测试新技术得到了应用,但增加了系统的复杂性[4],可靠性大为降低。基于罗氏线圈原理的测试方法由于成本较低、非侵入特性,逐渐成为冲击电流测量的主要方法[5-6]。

现有的冲击电流测量多采用高速采集卡结合台式PC机,其体积大、质量重,不易携带,在现场多点冲击电流测试中需在一定范围内移动测试装置,故亟需便携式的测量装置,在保证基本功能与测量精度的前提下,提高测试效率。本文针对典型冲击电流波形设计了一套便携式冲击电流测量装置,其体积小、质量轻,可实现全波采集,并现场显示被测冲击电流的幅值与上升时间,可本地存储1 300次冲击电流全波波形。

1 冲击电流频谱分析

8/20 μs冲击电流波形指波前时间tf为8 μs、半峰值时间td为20 μs的电流波形,是冲击电流测试中的典型波形,如图1所示。本文将8/20 μs典型冲击电流作为试验对象,首先对其电流波形进行频谱分析。8/20 μs冲击电流波形常表示为双指数函数[7],如式(1):

i(t)=Im(e-t/T1-e-t/T2)

(1)

式中:Im为冲击电流峰值;i为冲击电流瞬时值;1/T1为波前衰减系数,令1/T1=α;1/T2为波尾衰减系数,令1/T2=β。

8/20 μs、峰值为5 kA的冲击电流波形的双指数表达式为

i(t)=29 000(e-105t-e-1.6×105t)

(2)

冲击电流的相对能量累积频谱为

(3)

式中ω为频率。

利用式(3)计算出冲击电流能量累积频谱如表1所示。

表1 5 kA 8/20 μs冲击电流相对能量累积频谱

根据表1的能量分布,可得出各频率段波形能量占总能量的百分比,如图2所示。其中:1为0~500 Hz;2为500 Hz~1 kHz;3为1~10 kHz;4为10~100 kHz;5为100~300 kHz;6为300~500 kHz;7为500 kHz~1 MHz。

由图2可知,8/20 μs冲击电流波形的能量主要集中在10~300 kHz间。若要保证冲击电流测量精度优于±3%,测量装置的工作频带则应设置为500 Hz~1 MHz[8]。

2 传感器原理及设计

针对被测电流的频谱分析结果进行传感器的设计。传统无磁芯罗氏线圈由于电感较小,下限频率较高,在采集时间跨度较大的冲击信号时易产生低频失真[9-10],若采取低频补偿,带来的额外电路将提高系统复杂度[11],难以保证稳定性与可靠性。本文在罗氏线圈中加入磁芯,可加大线圈的电感以改善传感器的低频性能[12],将带磁芯的罗氏线圈称为磁芯线圈。磁芯线圈的感应电势与被测电流成微分关系[13],所以要获得正确的一次电流值,需要加入积分环节[14]。冲击电流测试中一般采取自积分方式[15],自积分磁芯线圈电流传感器等效电路图如图3所示。

其中i2为磁芯线圈中流过的感应电流,L0、R0、C0分别为磁芯线圈的自感、内阻以及杂散电容,Rm为积分电阻,u(t)为积分电阻两端的电压,则当C0阻抗远大于积分电阻Rm时有:

(4)

化简可得

(5)

联立式(4)、式(5)得线圈在零初始条件下的传递函数

(6)

幅频特性为

|H(jω)|=

(7)

自积分限制条件为

(8)

一般线圈设计按3 dB带宽计算上下限频率,如式(9)、式(10)所示:

下限频率为

(9)

上限频率为

(10)

本文为取得更高精度,将式(8)两边相差10倍得上下限频率[16]:

下限频率为

(11)

上限频率为

(12)

由式(11)、式(12)可知,线圈的上限频率与积分电阻和分布电容有关,下限频率与线圈内阻、积分电阻以及线圈电感有关。

结合上述分析,0.5~5 kA、8/20 μs冲击电流传感器的设计参数见表2,制成的传感器灵敏度为3 mV/A,幅值为5 kA冲击电流对应输出电压为15 V。经国家高电压计量站标定,其幅值测量的拓展不确定度为1.5%,包含因子为2,波前时间与半峰值时间的测量拓展不确定度为2.1%、2.1%,包含因子为2。

表2 线圈参数

3 测量装置设计

冲击电流测量装置主要由冲击电流传感器、高速A/D转换器、数字逻辑电路FPGA及其外设组成。传感器输出的模拟电压信号通过信号调理电路进入A/D转换器转换为数字信号,再进入FPGA进行信号处理与计算,并通过外设进行存储与显示。装置数据流框图如图4所示。

3.1 硬件设计

3.1.1 信号调理电路

信号调理电路是模拟信号进入A/D转换器前的媒介,使模拟信号输入符合A/D转换器要求。调理电路将±15 V内的双极性电压进行电阻分压,然后经过电压跟随器和差分放大器将信号衰减,叠加+2 V的直流电压基准电平后变为1~3 V的单极性电压信号。信号调理电路输入输出设置如式(13)所示:

Vout=(1/15)Vin+2.00

(13)

3.1.2 A/D转换器

根据8/20 μs冲击电流波形频谱分析,A/D转换器需至少满足500 Hz~1 MHz频带内的波形还原,采用12位AD9226芯片,非线性误差最大为0.05%,最大采样速率为65 MSPS,满足对8/20 μs冲击电流波形的测量要求。

3.1.3 数字逻辑电路FPGA

为配合高速A/D转换器采集速率,同时满足高实时性、高性能运算,采用FPGA作为数字逻辑处理电路。利用FPGA的并行处理能力,可以在一个时钟周期内完成数据的处理运算。FPGA采用50 MHz外部晶振时钟,通过锁相环对时钟进行分频与倍频,同时驱动A/D转换器工作。FPGA与A/D转换器采用板间直插避免时钟信号偏移与采样信号干扰。本文使用EP4CE30型号FPGA芯片,提供28 848个逻辑门和533个I/O口,满足本设计要求。

3.1.4 存储器

8/20 μs标准冲击电流全波时间跨度最大为100 μs,频带上限约为1 MHz,为兼顾存储容量,设置A/D转换器采样速率为25 MSPS,分辨率为12 bit,为方便通讯将数据补齐至16位,即完整采集一个8/20 μs冲击电流波形需要24 kbit存储容量。本文采用一块32 Mbit容量Flash作为数据存储器,可存储1 300组试验波形。

3.2 逻辑设计

采用FPGA作为数字信号处理电路,同时作为A/D转换器的控制驱动器,对FPGA内部的逻辑时序要求较高。测量装置逻辑部分主要包含触发判断模块、时钟管理模块、FIFO缓存模块、计算模块、数据合并模块与接口控制模块,以下逐一进行说明。

3.2.1 触发判断模块

为保证测量系统在冲击电流信号产生后及时响应,避免误触发的现象,采用电平触发与边沿识别相结合的方式。分别设置正负2个触发电平,当输入电压信号大于正极性触发电平,同时边沿检测为连续4 h周期的上升沿,则判断冲击电流为正极性,或当输入电压信号小于负触发电平,同时边沿检测为连续4 h周期的下降沿,则判断冲击电流为负极性。此时产生触发信号,并使能主存FIFO与计算模块,如图5所示。

3.2.2 时钟管理模块

FPGA采用外部晶振驱动模式。外部晶振将50 MHz频率的时钟信号传输至FPGA中,FPGA通过锁相环将时钟信号进行分频与倍频,得到不同频率的时钟信号驱动不同模块工作。

3.2.3 FIFO缓存模块

传统信号采集装置采取单级FIFO缓存,在触发信号响应时会丢失达到阈值前的部分波形,造成波形缺失,为达到全波采集功能,采取暂存FIFO和主存FIFO两级缓存模式,称达到触发阈值前的波形为前波,达到触发阈值后的波形为尾波,触发时刻数据流图如图6所示,当触发判断模块的触发信号生效后,前波信号还储存在暂存FIFO中,这时使能主存FIFO读取暂存FIFO中的信号就可实现全波信号完整储存。

3.2.4 计算模块

计算模块用于计算输入冲击电流的幅值与上升时间。为防止A/D转换器采集信号的扰动,设置计算模块的工作频率为A/D转换器工作速率的1/5。设t为计算模块的工作周期,At为第t个时钟周期输入至计算模块的12位二进制数据,At-1为前一时钟周期输入的12位二进制数。由于已知A/D转换器采集速率,通过计算点数乘采集速率系数即可得出冲击电流的上升时间,根据输入12位二进制数的最大值乘幅值系数即可得出冲击电流的幅值,计算流程如图7所示。

3.2.5 数据合并模块

数据合并模块对主存FIFO与计算模块传输的数据进行合并处理以方便通讯。同时为方便通讯,将主存FIFO传来的12位数据补齐至16位,并在主存FIFO结束传输后接收计算模块的数据。

3.2.6 接口控制模块

接口控制模块将数据合并模块的数据进行通讯协议匹配,其中分为三路传输,一路通过UART协议传输至上位机,一路通过SPI协议传输至Flash存储器,一路通过显示控制器控制LCD显示被测冲击电流幅值与上升时间,如图8所示。

4 实验测试

测量装置硬件主板采用双层PCB板设计,总体体积约为15 cm×15 cm×5 cm,质量约为500 g,功率约为1 W,使用2节5号电池进行供电,可连续工作3 h。使用S6C6型冲击电流发生器产生幅值为3 kA的单周期8/20 μs冲击电流,对测量装置进行测试。冲击电流发生器的参考输出端接入示波器,作为标准波形校验本装置精度,测试场景如图9所示。

幅值为3 kA的标准波形与装置测得的波形如图10所示。

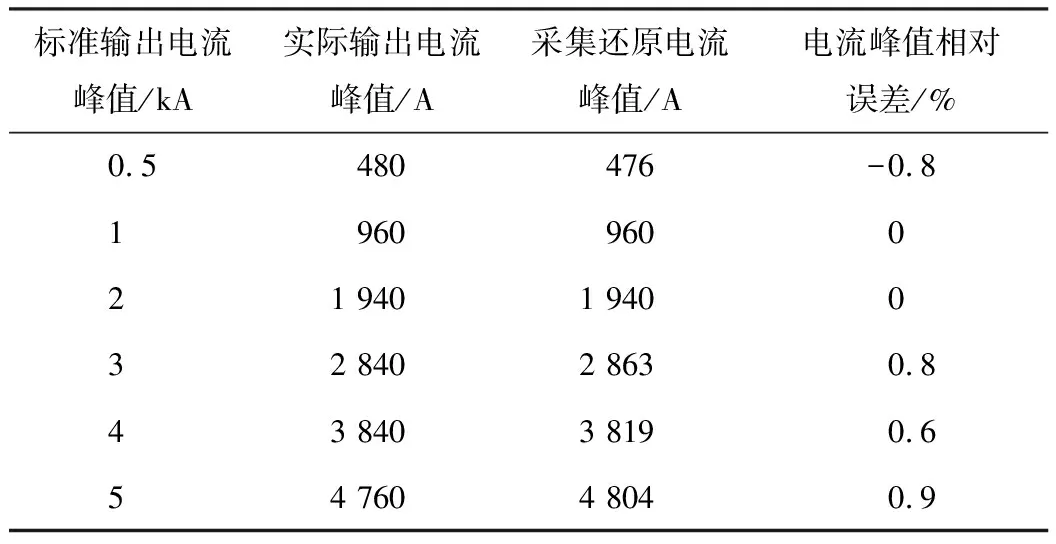

在0.5~5 kA不同幅值冲击电流下的幅值响应测试结果如表3所示,可知幅值响应精度在±1%内。

表3 幅值响应测试结果

在0.5~5 kA不同幅值冲击电流下的上升时间测试结果见表4。可知上升时间测量精度在±4%内,输入波形的毛刺可能会影响计算模块对波形的正确处理,后续可在计算模块中加入平滑处理,提高计算有效性。

表4 上升时间测试结果

5 结论

根据8/20 μs典型冲击电流频谱,设计并研制磁芯线圈冲击电流传感器,采用FPGA作为信号处理运算电路,同时控制A/D转换器工作,利用两级FIFO实现冲击电流波形的全波采集,并将被测冲击电流的幅值与上升时间实时显示。测量装置体积小、质量轻、功耗低,便携性佳,可显著提高现场多点冲击电流测试工作的效率。