宽带横电磁波小室设计与测试应用

2021-10-14袁钟柱万发雨

袁钟柱 万发雨

0 引言

随着电子技术的高速发展,集成电路的工作频率不断提高,而加工芯片的尺寸却在进一步减小,单个芯片集结了越来越多的功能,这些发展使得芯片级电磁兼容显得尤为重要[1].传统横电磁波(TEM)小室的测量带宽仅为1 GHz,远远不能满足集成电路的测试要求.而TEM小室法作为一种最方便准确的用来测量辐射发射的方法,亟需提升其可用的上限频率.目前最先进的符合IEC标准的国外商业TEM 小室的设计频率为3 GHz,但是产品仅提供S参数指标,对集成电路电磁辐射测试非常重要的参数如场均匀性、加载被测物(EUT)后的场分布等参数都还欠缺.

国内关于TEM小室的研究有很多,文献[2]介绍了传统横电磁波小室的分析方法,包括TEM小室的高阶模截止频率与谐振频率、特性阻抗、场分布的均匀性并采用时域有限差分(FDTD)的方法计算可用上限工作频率,与实测结果相吻合,但其尺寸标准并不统一.国外学者也对提升TEM小室的上限频率给出了很多改进方案.文献[3]采用金属线列结构的内导体大幅场均匀性同时削弱了EUT的耦合;文献[4]采用吸波材料的方法使其可用带宽翻倍;文献[5]加装吸波材料、铁氧体、磁环、开缝等措施抑制高次模,使其频率达到2.5 GHz;文献[6]证实了纵向开缝可抑制谐振,但谐振的模式仍然复杂;文献[7]设计了一种新型TEM小室实现了优良的驻波性能并给出了开缝的结果,但未进行实验验证.上述文献的上限频率只能提高到2.5 GHz,还有进一步改善的空间.

本文设计了一款符合IEC标准的宽带TEM小室,可将其工作带宽提升至3 GHz;同时设计一款与之匹配的集成电路(IC)测试板,并采用TEM小室对IC芯片进行辐射测量以改善IC的电磁兼容性.本文第1部分介绍TEM小室的结构设计;第2部分给出关键参数的仿真结果以及和实测结果的对比;第3部分采用TEM小室对设计的PCB测试板进行辐射测量与分析;第4部分为总结.

1 TEM小室设计

1.1 TEM小室的介绍

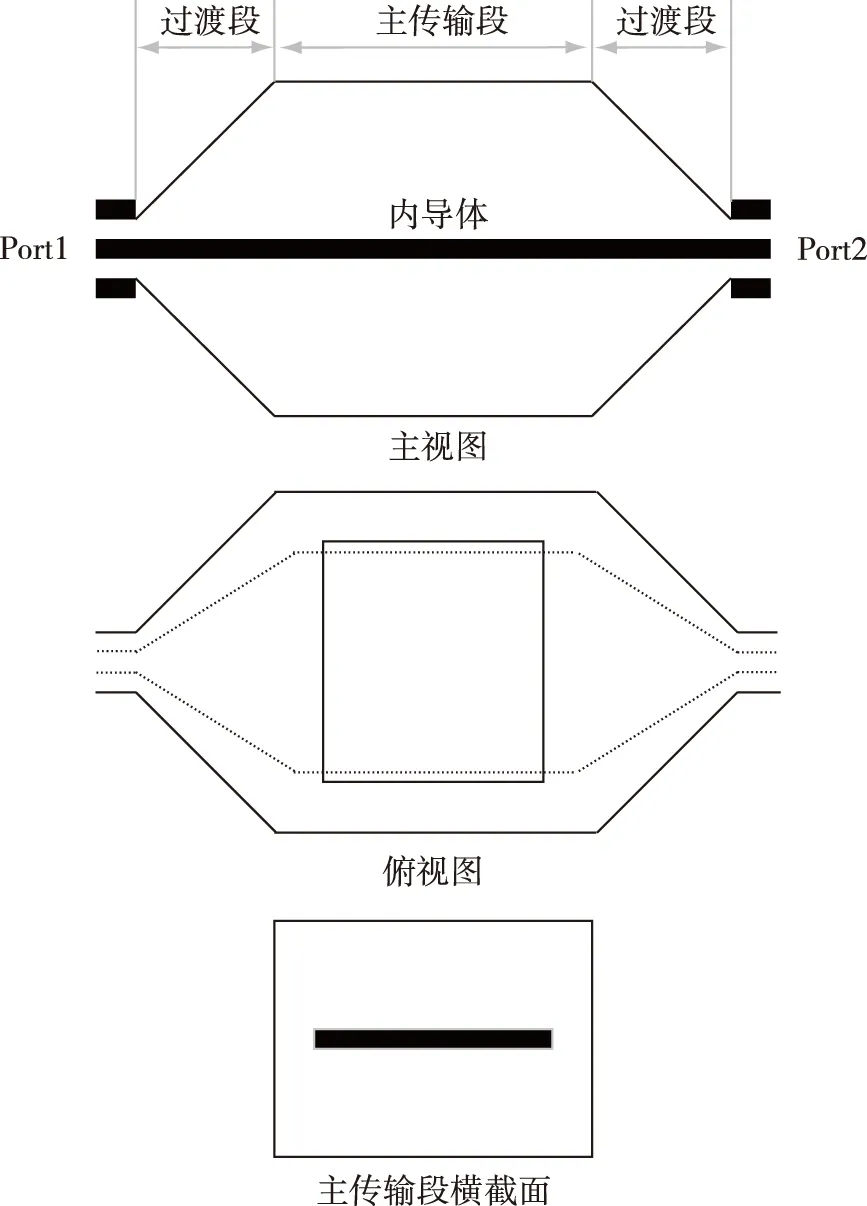

标准的TEM小室的三视图如图1所示,包括一个主传输段、两个过渡段以及两端的转接头.

图1 TEM小室的三视图Fig.1 Three views of the TEM cell

整个TEM小室由内外双导体组成,主传输段类似于封闭的带状线结构,内导体处于中心位置,下方有4根低介电材料的圆柱棒作为支撑.在主段上方留有一开孔用以放置待测的PCB,内导体的渐变段将连接到同轴线的内芯上,外导体连接至同轴的屏蔽壳体部分.整个TEM小室呈中心对称结构,测试时两个端口可以互换使用.

TEM小室是一种TEM波导装置,可传输横电磁波,可用来产生或检测已知场的密度,也可用于场的计量校准等.此外,TEM小室还广泛应用于集成电路的辐射发射测试和抗扰度测试中.TEM小室内场分布如图2所示.

图2 场线分布Fig.2 Field distribution

TEM小室内的场强值可通过输入功率计算,由于小室结构阻抗不完全连续,会形成驻波.所以小室内传输的电压波和电流波一般是由入射波和反射波两部分叠加而成的.电压波和电流波之比等于传输线的特性阻抗.如果驻波效应不明显,测出通过小室的净功率Pn,则

(1)

式中Rc为小室特性阻抗的实部,Pn为通过小室的净功率.

1.2 TEM小室的结构设计

完整的TEM小室结构包括主传输段、由主段向同轴线过度的渐变段以及50 Ω的同轴转接头.整个TEM小室为对称结构,其设计应从以下几个方面考量:

1)使可用的测试区域尽可能大;

2)使可用的上限频率尽量高;

3)保持小室各段阻抗的稳定性;

4)使测试区域的电磁场值波动尽量小.

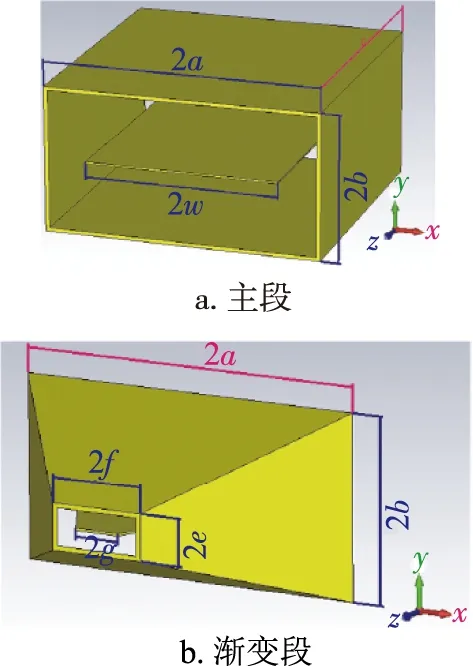

整个参数化建模如图3所示,其尺寸由表1给出.由于整个模型成中心对称分布,为了简化建模的复杂度,所设的各单位均为实际长度的一半.完成参数化建模后,设置仿真频率、波导端口、网格以及边界条件便可以对内导体的宽度参数进行扫频分析,以保证各段的特性阻抗在50 Ω左右.

图3 TEM小室结构示意Fig.3 Schematic diagram of TEM cell

表1 TEM小室尺寸参数

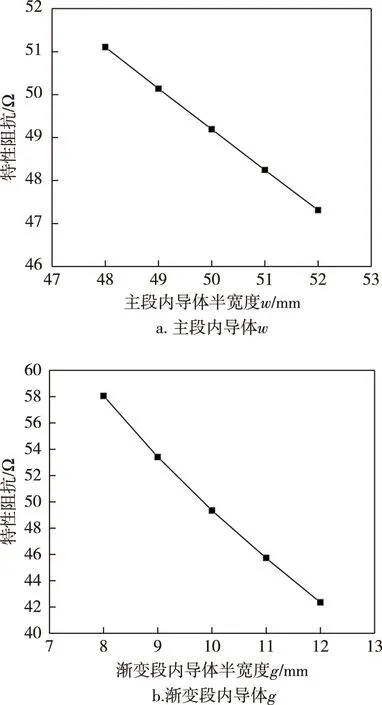

通过对主段宽度进行参数扫描分析,结果如图4a所示,整个主段的特性阻抗的大小随着内导体宽度的增加而线性减小,取w值为49.15 mm,即内导体宽度为98.3 mm时,主段的特性阻抗正好符合设计要求.主段的设计可以保证测试区域的稳定以及减弱EUT对场的影响.

图4 内导体宽度扫描结果Fig.4 Parameter sweep of inner conductor width

末端内导体宽度对特性阻抗影响较大,对其进行参数扫描,结果如图4b所示.取g的值设为9.8 mm,即宽度为19.6 mm时可以得到50 Ω的特性阻抗.TEM小室的设计中,整体需与同轴转接头相连,采用的N型法兰板外壳需与小室的外导体相连.将外导体延长一小段并封闭其端口,在封闭板上挖出适配于接头大小的孔洞并将其和内导体连接使之成为一个完整的TEM波导结构.

2 TEM小室参数仿真与实测对比

2.1 S参数仿真

TEM小室的性能参数包括S参数、场均匀性及EUT对场分布的影响.性能良好的TEM小室一般要求:反射系数小于-12 dB,传输系数大于-3 dB,场均匀性优于2 dB.

从图5的仿真结果可知:整个TEM小室在0~1.95 GHz的频段内基本保持在反射系数小于-19 dB的水平,传输系数则大于-1 dB,在2~3 GHz内也基本满足了反射系数小于-15 dB.此外,频段内还出现了3个谐振点使其在1.99、2.30和2.72 GHz频率附近的性能急剧恶化.可能是由于整个小室近似为谐振腔,谐振频率处的TE模扰乱了电场分布,需采取磁环或吸波材料等对横向电流进行抑制.

图5 S参数仿真结果Fig.5 Result of S-parameters simulation

2.2 测试结果

对加工的TEM小室用矢量网络分析仪(罗德施瓦茨,型号ZNB20,频率100 kHz~20 GHz)进行S参数测试,测试平台如图6所示,测试频带为50 MHz~3 GHz.测试结果如图7所示,在50 MHz~2 GHz,满足设计指标,但是在2~3 GHz有3个谐振点,导致反射系数和传输系数都不满足指标要求.下一节讨论谐振抑制方法.

图6 测试配置Fig.6 Test configuration

2.3 谐振频率的抑制

抑制谐振频率的方法有很多,诸如放置磁环、磁条、铁氧体、吸波材料等,还有切割内外导体以开缝的形式抑制表面电流的方法,但具体的效果如何,还有待实验验证.

本节采用置入磁环的方法对其进行测试.图7是加入磁环前后的S参数对比,在置入磁环后,谐振频率处的峰值得到了较好的抑制,反射系数低于-12 dB,传输系数优于3.5 dB,可以满足0~3 GHz内测试的基本要求.

图7 置入磁环前后的S参数对比Fig.7 Comparison of S-parameters before and after inserting the magnetic ring

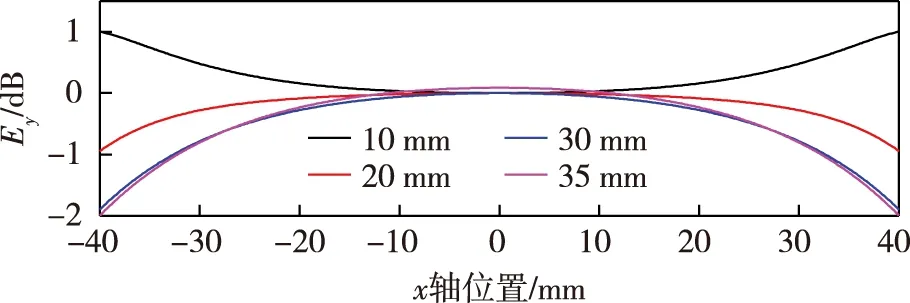

2.4 场均匀性仿真

在TEM小室的测试区,垂直场分量是主分量,水平场分量一般比垂直场分量小一个数量级,可不予考虑.本文仅考察芯板与底板间(即上半腔)垂直场分量Ey的分布情况.在绘制测试板时,一般将芯片置于PCB正中间,因此可在小室中间取4条距离顶端不同高度的线上的场值来进行评估各处的场的均匀性,并按下式归一化:

(2)

场均匀性仿真结果如图8所示,对于20 mm×20 mm的大小的IC芯片,其场均匀度可以达到±0.5 dB,而80 mm×80 mm的区域内仍然可以获得±2 dB的场均匀性.芯片尺寸一般较小,本文设计的TEM小室完全满足要求.EUT的大小对场分布的影响将在下一节中予以探究.

图8 归一化场均匀性仿真Fig.8 Normalized field uniformity simulation

2.5 EUT对场分布的影响

TEM 小室会对放入其中的EUT(被测物)耦合而产生影响,从而改变TEM 小室的特性阻抗及场分布等关键参数.当置入金属物体后,由于理想导体导电率无限大,表面是等势面,内部没有任何电场存在,电磁波将被反射,反射系数取决于金属的复介电常数.而反射的部分电磁波将在TEM小室内来回反射从而影响能量的传输.

IC尺寸较小时,其对场的影响很小.随着尺寸增加到可与开口尺寸比拟时,EUT会在一定程度上影响场的分布与均匀性.本节对置入金属导体的影响进行仿真分析.基于1/3准则,本节将在中心位置的金属尺寸设定在50 mm×50 mm,对其厚度进行扫描分析.

场分布仿真结果如图9所示.当EUT 小于1/10时,对特性阻抗几乎没有影响;当EUT 在1/3左右时,已经对阻抗产生了较大的影响,反射系数已经达到-10 dB,但此时小室依然是可用的.当厚度超过20 mm时,反射系数已接近-5 dB,阻抗已经严重失配,将导致其反射大幅提高,不仅对场分布产生恶劣的影响还会加大测试误差.

图9 金属EUT厚度对S11的影响Fig.9 Influence of metal EUT thickness on S11

2.6 与国外商业TEM小室的对比

美国的Fischer Custom Communications,Inc(FCC)公司对于不同需求的集成电路提供了一系列TEM小室,可用于辐射发射和抗扰度测试.本文设计的TEM小室与商业产品的性能对比如表2所示.

表2 与国外商业TEM小室的对比

本文所设计的TEM小室与FCC-TEM-JM系列适用同样的IEC标准,并在最大的受试设备的尺寸、最大功率容量、转接头等方面有着几乎相当的水平.总体而言,反射系数相差3 dB左右,传输系数相差1 dB.但本TEM小室场均匀性更佳且制作成本远远低于商业TEM小室.

3 IC辐射发射测试

3.1 测试PCB

本次实验所选用的芯片型号为STM32F103RCT6,32位高性能处理器,其时钟频率高达72 MHz.芯片供电电压3.3 V,内部还有40 kHz的RC振荡器,同时也外接了一个32.768 kHz的晶振作为RTC时钟源.芯片内有多达12个通信接口.

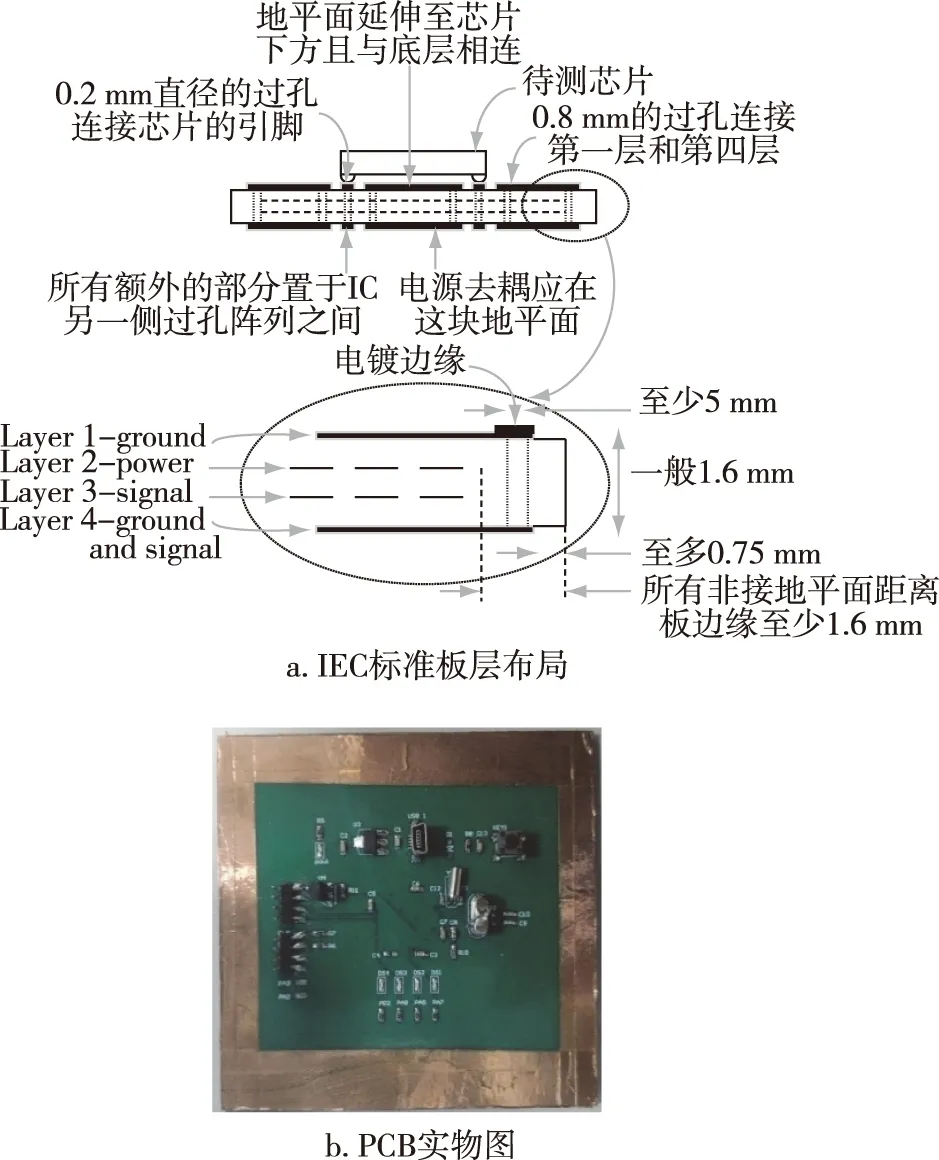

根据IEC的标准[8],如图10所示,整个PCB分为4层:第1层为电源层,受试IC处在底层并通过0.2 mm的过孔将引脚连出;第2层为电源走线层,同时须保证电源去耦电容处在过孔阵列的内测;第3层则是信号线层,将芯片引出的引脚线与各个模块相连;最后一层是与第3层共用的信号线层,在走线完毕后还需将整层进行铺地以隔绝外界的辐射,提升TEM小室本身的抗干扰能力.在板层设计完成后,在板边缘部分需将一定范围内的阻焊层开窗,这样可以使得裸露出的电镀层在与TEM小室的外导体相连以保证接地的完整性,进一步增强其对外界的抗干扰能力.

图10 IEC标准测试板Fig.10 Layout(a) and picture(b) of IEC standard test board

在完成硬件调试后对4种测试代码进行编译,采用ST-LINK将程序烧录至板中,显示红灯闪烁则说明程序已烧录成功.通过USB-TTL线将测试板连接至电脑的端口并打开串口监视器发送任意字符,端口可返回目前的室内温度.本次实验包括了I/O口、温度传感器、串口、ADC以及SPI FLASH 4种测试代码.

3.2 测试结果与分析

TEM小室用于辐射发射测试配置如图11所示,实际测试平台如图12所示.TEM小室的一个端口连接50 Ω负载,另一个端口通过预放大器将结果输出至频谱分析仪,但实际用于测试尚有很多需注意的地方.TEM小室内必须没有被测频率范围内的高次谐波;使用EMI接收机的频谱仪模式时,需采用最大保持模式;若信号被淹没在噪声中,则需采用低噪声放大器对微弱信号进行放大,提高信噪比;放大器需与小室的输出端口直连,避免外部的干扰耦合进入小室的内部而影响测量结果;在使用电源供电时,可以在电源线上加载磁环用以抑制电磁脉冲.

图11 测试配置示意图Fig.11 Schematic diagram of test configuration

图12 IC辐射测试图Fig.12 Picture of IC radiation test

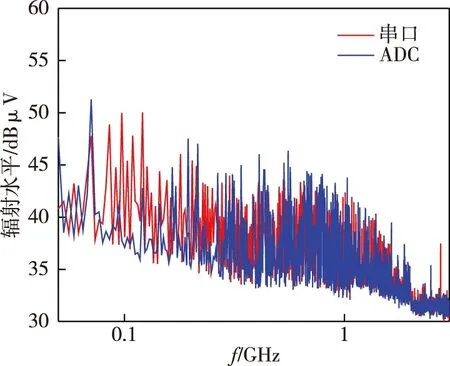

分别对串口通信、ADC、SPI以及温度传感器的运行代码分别烧录,并对同一方向的结果进行比较.串口和ADC辐射测试结果如图13所示,将串口和ADC两个结果对比可发现其主要的差异集中在70 MHz至120 MHz之间,其中SPI和ADC分别为芯片内部的调用与读取,而温度传感器和串口通信需要外部的数据传输线,这可能是导致121 MHz左右相差较大的原因.

图13 串口与ADC辐射水平对比Fig.13 Comparison of serial port and ADC radiation level

如表3所示:在使用ADC时所产生的辐射最大,在70.6 MHz最大可达51.3 dBμV;其次是外部的串口和温度传感器在使用数据线传输数据时,会在121 MHz左右产生最大值;读取SPI Flash缓存时所产生的的辐射最小.

表3 各状态下的辐射水平对比

EUT在运行ADC代码时,所产生的辐射骚扰最大,这些辐射可能是由数据传输时所对应的时钟频率或其谐波所造成的.所以在晶振或振荡电路外围需要以最短的布线与尽量多的滤波电容接地才能较好地抑制这种辐射.

4 结束语

本文设计了一款符合IEC标准的TEM小室,在0~3 GHz内获得了小于-12 dB的反射系数与优于-2.5 dB的传输系数.此外,该TEM小室的测试区域场均匀性优于±2 dB并给出了EUT大小对场分布的影响.最后本文采用所设计的TEM小室对IC辐射进行了测试与分析.