车用塑封集成电路封装失效率估计

2021-10-13吴世芳潘进豊谢杰任

吴世芳,潘进豊,谢杰任

(1.蔚思博检测技术(合肥)有限公司车电功能安全服务事业处,上海 201203;2.虎尾科技大学,台湾云林 63230)

1 引言

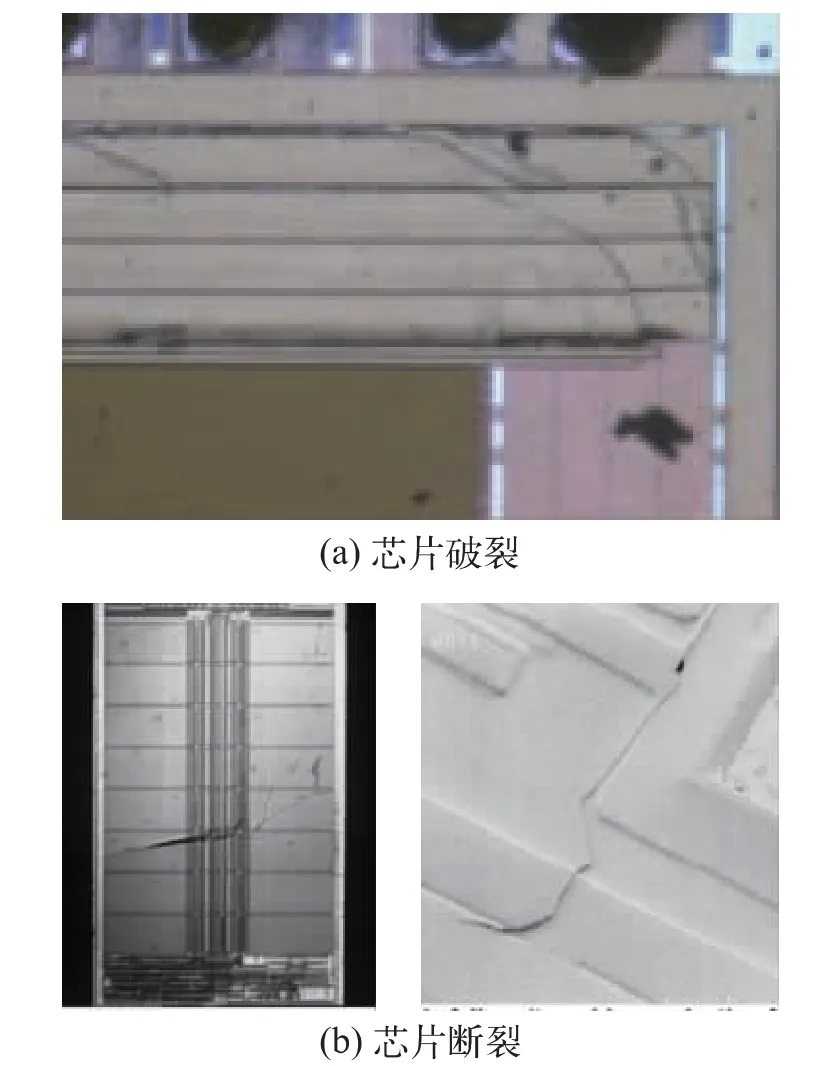

芯片(IC)封装常见的封装失效物理机制(Physical of Failure)有封装材料分层、芯片破裂、焊点疲劳等,本研究的出发点为基于封装失效模式评估封装失效率(λpackage)。

就研究性而言,有许多研究采用有限元分析方法(Finite Element Analysis,FEA)建模,建模过程须多方数据、假设和仿真,众多研究已对材料分层方面进行探讨[1-3],FEA适用于一种或两种失效机制建模,常用于特定失效模式更深入或精准的研究。

就普遍性而言,可靠性工程师常用可靠度手册或国际标准进行可靠性评估,常见的可靠度手册为某公司或组织收集自家产品的数据所整理出来的失效率估计方法,例如贝尔通讯Telcordia SR-332,西门子SN 29500,法国空巴FIDES;而常见的国际标准有MIL-HDBK-217F、IEC TR-62380、IEC 61709等。相对于有限元分析,直接引用可靠度手册或国际标准令人垢病的是,没有在足够科学的基础上考虑设计、制造过程和选用材料/零件(Bill of Material,BOM)对产品可靠性的影响[4];往往未针对故障机制先进行准确建模,也未考虑故障物理现象;或者没有给出预测的任何置信度(Confidence Level);另一个主要问题是过时的参考数据和资料,除了FIDES 2009A(2010)[5]、IEC 61709(2017)[6]、SN29500-2(2010)[7]、SN29500-11(2015)[8]、SN29500-15(2016)[9]及SN 29500-16(2015)[10]外,其余最新版本皆早于2010,众所皆知,先进封装技术的发展日新月异,从单一芯片封装到系统级封装(System in a Package,SiP),演进2D、2.5D直至3D;增加工艺如金属凸块(Bumping)、再布线工艺(Redistribution Layer,RDL)、中介层(Interposer)、硅通孔(Through-Silicon Via,TSV)等,发展出各类型的封装,如天线封装(Antenna in Package,AiP)、集成扇出型封装(Integrated Fan-out,InFo)、芯片在晶圆基板封装(Chip on Wafer on Substrate,CoWoS)、芯片在基板扇出型封装(Fan-out Chip on Substrate,FoCoS)、扇出型晶圆级封装(Fan-out Wafer Level Package,FOWLP)等,单一手册或标准已难以涵括各类型封装的失效率预估,如果IEC 62380继续被认同,则重新梳理修整是必然的,本研究提出可参考增修的方向。

就通用性而言,国际电工委员会(IEC)发布的IEC TR-62380[11]是当前产业界常被引用的国际标准,该标准以电子产品整个任务轮廓中的热效应用于故障率预测。IEC在2018年通告IEC 62380下架,并以IEC 61709取代,其采用的可靠性影响因子数值仍是1992—2001年间所采集的数据,而且失效率预估前未先就故障机制准确建模。尽管如此,欧美各主要芯片供货商并未放弃使用IEC 62380,其原因是欧美芯片供货商自使用IEC 62380起,芯片失效率估算经过后续几个世代现场或者测试数据的可靠度发展及校正,俾助精确的预测该产品系列的失效率,其失效率预估只是其预测的起点值,而非终点值;另一方面,IEC 61709未提供其数学公式中参考条件下(40℃)的故障率λref,单单引用IEC61709并无法独立完成故障率预测。

本文以IEC 62380探讨车用塑封芯片λpackage为主轴,以标准的数学估算模型为基础,就以下3个方面进行了研究与探讨:1)车用供应链彼此间任务轮廓信息交换的方式和内容;2)发展封装失效率估算方法和流程;3)延伸发展估算合理化方法和流程。

未来几年,汽车行业的发展路线图是电动汽车和自动驾驶,它的实现将带来与汽车本身的发明同等质的变化。传统机动车辆主要是机械传动系统,但未来是电子控制系统,智能化新功能提高了驾驶员和其他道路使用者的安全性,这意味着许多电子组件必须重新以面向安全的开发过程才能实现安全目标,而其最直接的要素便是电子化系统的可靠性提升。而大部分芯片供货商原是提供消费类产品的解决方案,对于消费类产品而言,仅约3~5年的使用寿命就足够了,但汽车行规的使用寿命标准却长达10~15年,因此功能安全与可靠性设计将是开发阶段首先要面对的课题,而失效率预估正是功能安全与可靠性设计的必要输入,所以,本文以一个实际汽车芯片封装验证案例为例,提供佐证以协助理解车用塑封集成电路封装失效率估算。

2 任务轮廓

IEC 62380的可靠度估计必须根据其现场使用条件进行,即首要定义任务轮廓,因为任务轮廓足以左右电子组件的可靠性,所谓的任务轮廓为“在完整的生命周期中,电子部件或组件在其所有预期应用环境中,由工作条件表述其工作周期或热负荷、功能负荷和其他应力等相关条件”,然而因个人使用条件、使用环境、操作习性的差异,电子部件任务轮廓肯定都无法对完整生命周期给予完善的定义,为此,IEC 62380建议考虑以下不同的操作模式阶段,给复杂的任务轮廓有可循的方向去描述:各种平均外部温度的开/关工作阶段(热循环);具有各种平均外部温度波动的永久工作阶段(日间/夜间,及春夏秋冬,周期性升温);存储或休眠阶段模式具有各种平均外部温度波动(日夜温差)。

即便有规范建议,对于产业下游的芯片供应商,建立任务轮廓仍有障碍,因为只有OEM知道各个电子组件上的外部环境负载、组件的安装位置以及确切生命周期[13],通常也只有Tier1/Tier2供应商才知道电子化系统本身产生的总负载(例如自热)及限制,而任务轮廓主要在汽车环境中用于指定热负荷、功能负荷和其他应力,具体取决于电子控制单元(ECU)、芯片等的特定工作状态,这却是芯片供货商负责的范畴。因此,安全可靠的开发项目要求必须透过OEM牢固地传递给Tier1/Tier2直至IC供货商,并对供应链内的提案加以考虑和审查,任务轮廓在整个供应链中交换信息如图1所示,如果这些信息的交换是明确的并且基于共同标准,则可以避免许多迭代甚至错误。

图1 供应链上的任务轮廓信息交换

当前汽车开发过程中,在供应链上的开发合作伙伴之间没有开启交换有关任务轮廓信息的管道,尤其是芯片供货商大多属于SEooC[15](Safety Element out of Context),更难取得上游厂商的确切信息,虽然在IEC 62380中提供了引擎室(Motor Control)和乘客舱(Passenger Compartment)两种应用场景,仍不能以一概全,芯片开发商必须根据芯片的工作场景及操作型态给予相应的调整,并经由可靠度发展建立该车用电子的任务轮廓。

3 封装失效率预估数学建模及估算流程[11,14]

芯片封装在正常工作期间功耗散发的热量或环境温度变化导致热波动或热循环,触发热涨冷缩的物理现象,从而导致封装材料之间、封装与芯片间或封装本体引脚与电路板互连焊点的应力和应变,亦或是热循环产生反复伸张/压缩(Tension/Compression)的剪应力。这是由于封装各个组件间的材料特性和热膨胀系数(Coefficient of Thermal Expansion,CTE)的不同而导致,最终造成芯片功能失效或降级(Degradation),这即是IEC 62380封装故障率建模的基础理论。

It should be noted that this might be the first time that the word “independence”was associated with Tibet within a United States government document.

IEC 62380将整体IC故障率λ分为3个数学模型:硅芯片故障率λdie、封装故障率λpackage和过压故障率λoverstress。本文只探讨λpackage。

式中,πa为电路板和封装材料之间的热膨胀系数差相关的影响因子,

αs和αc的参考值见表1;ΔTi为任务曲线第i个任务的平均振幅变化,

表1 封装与PCB材料CTE[11]

(tae)i为任务轮廓第i阶段设备周围环境温度的平均值,(tac)i为在邻近组件的PCB平均环境温度,tac等于PCB附近组件的平均升高温度与tae的和,ΔTj为在τon阶段消耗功率导致的组件内部温度增加量;(πn)i为第i个影响因素,与热变化的年循环次数有关,其温度振幅为ΔTi,ni为第i个影响因素热循环年次数,当ni≤8760次/年时,

当ni>8760次/年时,

πa、ΔTi和(πn)i等3个失效因子相加成的效应被认为是造成封装失效模式的根本原因。对应于加速寿命实验方法,可用JEDEC的功率循环[16](Power Cycling,PC)和热循环[17](Thermal Cycling,TC)判断电子封装组件的允收与否。在此效应下,最容易受到伤害的区域是硅芯片表面边缘和此区域的焊球,因为边缘位置上的表面应力和剪力应变量最大[1],另外芯片中心所受到的弯曲应力(Bending Stress)最大,常见的失效模式是芯片破裂,如图2所示,这两种加速测试方法非常接近实际故障情境,可作为测试验证。

图2 温度变化造成的封装失效

关于集成电路封装的基本故障率λ3,IEC 62380提供了两个查表,见表2及表3。表2视为非表面黏贴(non-SMT)类型芯片,λ3个别以引脚数量(S)为函数。表3则为SMT类型芯片,λ3以封装体对角线长(D)为函数,再细分为两种类型:一种是导线架(LF)的封装,以S和引脚间距(Pitch)取代长度来计算D,如表3中Note(1)及Note(2);另一种是球栅阵列(BGA)封装,以长度和宽度来计算D,如表3中note(3)及note(4)。不可否认的是,表列的封装类别无法囊括所有的封装型态,尤其是先进封装类型,如2D/2.5D/3D IC封装,如果表上没有合适的封装类别,建议找相似类型的封装来做评估,毕竟从数学模式来看,影响λ3最大的因素是S或是D,而影响λpackage最大的是λ3与热涨冷缩效应的加乘效果。

表2 λ3值:以封装引脚数S为函数[11]

表3 λ3值:对于SMT,以封装对角线D为函数[11]

这个失效率预估数学模型缺少了高温老化的失效效应,即便ΔTi已经包含了ΔTj,但是其高温效应仅局限于1/3的ΔTj量度,对于当代高度可靠要求的复杂先进封装结构建模是不足的,当2.5D/3D IC封装处于高热环境下,会引起封装材料之间、封装材料与芯片间诸如分层和开裂之类的失效机制[3],可用JEDEC高温存储[18](HTSLT)作为寿命加速实验方法,其失效原理是因为长期处于高于底部填充材料玻璃化转变温度(Tg)的环温下,造成填充材料(Underfill)的老化质变,使填充材料/硅的界面强度减弱,而发生TSV中介层及底部填充材料分层或开裂的失效机制,如图3所示,此时对失效的芯片进行FT(Final Test),很容易看见Open/Short现象,这将是IEC 62380数学模型未来改善的方向之一,高温场景下操作可考虑将阿瑞尼斯方程式(Arrhenius Equation)加入数学模型之中,譬如JEDEC 122H[19]以Norris Landzberg Model加乘Arrhenius Equation来估计可靠度。

图3 高温老化的失效效应

另外,此数学模型也没有相对湿度的影响效应,主要是因为与温度效应相比,湿度相关的故障率微不足道,特别是对于现代芯片,氮氧化物(Oxynitride)保护层对抗水气的能力超强,因此可假设潮湿环境导致的密封外壳的故障率是零(λ0RH=0)[5,11]。

本文根据IEC 62380数学模型,发展了一个有层级、有顺序、有逻辑的λpackage估计流程(见图4),此流程可协助封装失效率估算循序渐进、按步就班地完成。

图4 λpackage估计流程

4 芯片封装失效率估计合理化

第3节中估计λpackage数学模型是基于对器件封装本身以及和系统印刷电路板的结构和热特性的理解而建立,此数学模型同时包含封装体内部和电路板焊点所有的故障模型,根据第3节数学模型不难发现蛮多焦点关注于热应力循环造成芯片封装体与电路板(焊点)之间的连接问题,事实上,封装连接点和电路板之间连接的失效率取决于更多的因素,这些因素往往涉及电路板的特定设计,因此业界认同芯片封装体与电路板的焊点故障可在电路板设计与电路板组装工艺中克服,应归类于电路板失效或是工艺改善的议题[15],理当在系统或组件级的FMEA分析期间由系统集成商考虑,况且其他标准的失效率估计也不含焊点失效率,而封装连接电路板之间相关的失效率估计约占整个λpackage的20%[20],芯片封装体的失效率(λpackagew/osolder)约占λpackage的80%。

先将λpackagew/osolder平均,再分布给每支引脚的失效率(λpin),即λpin是通过将封装体失效率除以封装的总引脚数得到的。

而芯片并非每支引脚/焊球(Pin/Ball)都有引线键合,芯片封装中有若干属于非接触(No Contact,NC)引脚/焊球,该引脚失效并不会造成芯片功能异常,故而只加总实际引线键合引脚/焊球数量的失效率,即是有效封装体失效率(λpackage_true):从而达成了芯片封装失效率的合理化估计,详细合理化流程如图5所示。

图5 封装失效率估计合理化流程

5 实际验证案例

IEC 62380中λpackage预估根据热效应和任务轮廓,环境热效应具有温升兼热循环;操作热效应会产生ΔTj,ΔTj的计算基于组件芯片的功耗和封装热阻(取决于封装类型、封装引脚数和气流),欲降低λpackage亦应慎选封装类型。

以下案例分析采用如表4所示的IEC 62380任务轮廓。τon为在有电源的工作模式下的总时间占比;τoff为在非工作或存储/休眠模式下设备的总时间比例,τon+τoff=1;白天平均温度为15℃,夜间平均温度为5℃;开车时间为每天白天4次,每夜2次,整天都未使用的车辆每年30天;全年度总开车时间平均500 h。

表4 车用电子任务轮廓[11]

案例分析:

有一通讯芯片应用于车内的讯息传递,其封装为0.50 mm节距,PQFP 128(14 mm×20 mm),芯片引脚分配如图6所示,ΔTj=30℃,共有18支NC引脚,以SMT方式组装在FR4电路板上,其合理封装失效率预估见表5。

图6 芯片引脚分配(Pin Assignment)

表5 案例:封装失效率整理

λ3使用表3 SMT类别,取决于D的函数,其宽度为14 mm,S为128,pitch为0.5 mm,先计算D值,如表3中Note(2),再计算λ3,如表3中型2。使用式(2)计算影响因子πα,表1给出了αs(电路板CTE)=16和αc(封装体CTE)=21.5。个别计算白天开车、夜间开车及不开车的温度振幅ΔTi,如式(3)及表4。对于温度年循环数(开关次数)都小于等于8760的汽车操作轮廓,参数(πn)i使用式(4)计算,ni为振幅ΔTi的年循环数。使用表4所示的“乘客舱电机控制”任务轮廓,结果总封装失效率(包含与电路板连接焊点)如式(1),λpackage=97 FIT。不包含焊点的封装的总故障率如式(6),λpackagew/osolder=77 FIT。假定封装故障率在引脚之间平均分配,引脚故障率如式(7),为λpin=77/128=0.6(FIT)。只计算110支(128-18)接触引脚的失效率,封装体失效率如式(8),λpackage_true=0.6×110=66(FIT),其值仅约占总封装失效率的2/3。

6 结论

本文藉由IEC 62380的芯片封装失效率预估,讨论与封装失效有关的影响因子和对应的失效模式,特别是温度变化造成封装材料之间、封装材料与芯片间、封装本体与焊点互连中的应变和应力而引发的封装材料分层、芯片破裂、焊点疲劳等失效,同时也说明了IEC 62380的不足之处,如高温老化效应。此外,本文建议上下游供应链间应进行任务轮廓信息交换。

同时本文根据数学模型发展λpackage估计流程和合理化逻辑,因为中型封装体以上的封装失效率如依据IEC 62380的数学模型预估,结果动辄超过100 FIT,使用的方法可得到较合理、准确且较低的估计值,以实际验证案例结果而言,比原预估值降低近1/3,这对后续的功能安全设计与可靠度设计有较大帮助。