虚拟示波器硬件设计

2021-10-13李鸿松李泽宏季尔优

李鸿松,武 锦,李泽宏,周 磊,季尔优

(1.电子科技大学电子科学与工程学院,成都 610054;2.中国科学院微电子研究所,北京 100029)

1 引言

示波器是一种功能众多的电子测量测试仪器,可以将肉眼看不见的模拟信号转换为肉眼可见的波形图像,便于人们研究和分析处理模拟信号。虚拟仪器是以计算机软件为核心,功能可以由用户自由定义、修改和设计,具有虚拟面板的一种新型仪器模式。基于虚拟仪器的思想,本文提出了一种基于FPGA和国产ADC芯片的虚拟示波器的硬件结构设计和实现方案。该方案以FPGA作为主逻辑控制单元,当硬件电路检测到模拟信号输入时,经过模拟前端处理和AD转换,在时钟信号控制下将转换后的数字信号同步到FPGA控制的存储单元中,最后通过PCIE接口传输至上位机完成信号处理、分析、测量、显示等功能。

虚拟仪器是一种新型仪器模式,通过电子仪器与计算机应用深层次结合而成,比传统仪器和一般智能仪器具有更强大的功能,是仪器发展的又一次飞跃。虚拟示波器就是虚拟仪器的一种,可以实现传统示波器大部分的功能,而且在很大程度上有着传统示波器无法比拟的优点,比如丰富齐全的功能、使用简单灵活和低廉的价格等。

2 总体硬件结构设计

本次设计是基于数据采集上的虚拟仪器系统方案来完成实现的虚拟示波器功能,通过FPGA与ADC完成数据采集并借助于上位机来完成各种信号的处理、分析、显示和存储等功能[1],其硬件结构如图1所示。

图1 系统硬件结构

本文采用FPGA在整个硬件电路作为主逻辑控制单元完成外部输入信号的采集工作。当硬件电路检测有外部模拟信号进入时,首先通过模拟前端信号处理电路完成对信号的衰减放大等处理,能够使该输入信号幅值满足ADC转换电路的输入要求;之后ADC将其接收到的模拟信号转换为数字信号并在时钟信号的控制下同步输入到FPGA控制电路的存储单元中;最后通过PCIE接口将数据传输至计算机,再由相应的应用软件完成信号的处理和参数测量、频谱分析、波形显示等工作。

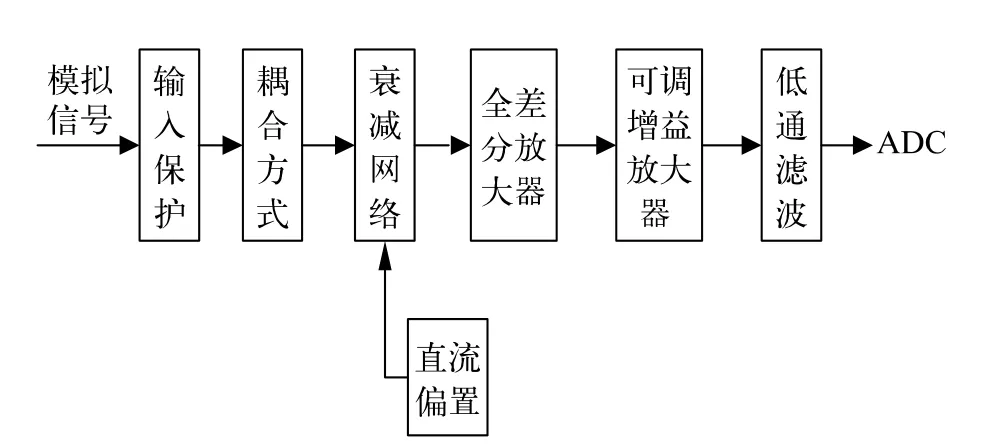

2.1 模拟前端

模拟前端处理就是一个信号调理电路处理的过程,是指把来自传感器或外界输入的模拟信号经过衰减、放大和滤波等操作后,转换为可用于数据采集、分析处理和计算显示等其他目的,且更容易存储、处理的数字信号的电路过程。其电路的作用有两个:一是通过衰减和放大电路将被测模拟信号的幅值调整至符号ADC芯片要求范围以内,保证ADC采样测试有较大的动态范围;二是为了不对被测模拟信号产生其他影响,同时需要保证调理电路有高的输入阻抗[2-3]。

本文设计的模拟前端信号调理电路结构如图2所示。由于在数据采集过程中信号大小是未知的,为了防止因采样信号过大损坏信号调理电路中的其他器件,在采样信号进入前加入了由两个二极管组成的输入保护电路。衰减网络主要是利用电阻分压,再加上用于频率补偿的电阻和电容组成[4],并通过继电器来选择多少大小的衰减。同时增加直流偏置模块对被测信号偏置电压进行调节,进而实现波形显示偏置调节。选用了一款低噪声、低功耗全差分放大器LMH5401将衰减后的被测单端信号转换为差分信号,再通过一个可调增益放大器实现信号的放大,最后通过低通滤波器去除掉高频分量和干扰的噪声进入到ADC模数转换器中。

图2 模拟前端结构

2.2 ADC模数转换

2.2.1 ADC芯片简介

ADC模数转换器是将连续的模拟信号转换为离散数字信号的器件,也是测试测量领域中关于数据采集硬件系统的核心器件[5]。本次设计选用全国产的ADC芯片AAD08D2250,是采用硅基工艺制造的高速宽带模数转换器。该芯片可将差分420 mV输入模拟信号转换成8 bit数字信号,芯片内包含2个最高工作在2.5 GS/s的子ADC,可工作在交织和非交织模式,在对数据进行2倍解复用(Demux)之后通过LVDS接口输出。输出信号包括1路时钟(2或4分频)、32路数据输出以及2路超量程比特输出,均为LVDS电平标准。芯片采用+4.6 V/+3.3 V/+1.8 V电源供电,总功耗约为4.2 W。芯片有144个引脚,为增强型导热焊盘LQFP封装,芯片封装及引脚如图3所示。

图3 AAD08D2250封装结构

管脚INI_P/INI_N和INI_Q/INI_Q为2路模拟信号输入通道,单路输入时最高采样率为2.5 GS/s,双路输入时交织状态下最高采样率为5 GS/s;I1A-I8A和Q1A-Q8A、I1B-I8B、Q1B-Q8B为32对差分数据输出端口;SDOUT和SDIN、SCLK、LDN为4线SPI接口,用于对ADC芯片的功能配置及性能校准。

2.2.2 ADC芯片特点

AAD08D2250高速宽带模数转换器电路结构如图4所示。根据虚拟示波器的性能要求,其主要性能指标如下。

图4 AAD08D2250内部结构

(1)分辨率:8 bit;

(2)采样精度:双通道模式1~2.5 GS/s,单通道模式2~5 GS/s;

(3)输入信号带宽:3.5 GHz;

(4)ENOB:6.4 bit;

(5)功耗:4.2 W;

(6)芯片封装形式:LQFP。

2.3 PCIE接口电路

2.3.1 PCIE总线简介

随着高速串行计算机扩展总线标准(PCIE)技术的发展逐渐成熟,同时为了满足高速率的数据传输要求,越来越多的数据采集设备使用了PCIE接口进行数据传输[6]。PCIE总线采用的是高速差分信号线连接发送端和接收端而成,其总线链路结构如图5所示。PCIE总线上的数据发送端和数据接收端分别连接在PCIE链路的两端,形成一个数据传输通道。除了总线链路外,PCIE总线在发送和接收数据时还被划分为多个层次。PCIE的总线层次结构与网络协议相仿,但与一般的计算机网络协议不同的是PCIE总线采用硬件逻辑来实现不同层次的功能[7]。

图5 PCIE总线的物理链路结构框图

由图5所示,在PCIE总线物理链路的每个数据通路(Lane)中,包含2组发送和接收的差分信号。其中发送端的发送链路同时也是接收端的接收链路,由一组差分信号连接发送端的TX部分与接收端的RX部分组成;而发送端的接收链路同时也是接收端的发送链路,使用另一组差分信号连接发送端的RX部分与接收端的TX部分组成[8]。每一个PCIE链路都可以由单个或多个Lane组成。

2.3.2 PCIE总线的层次结构

PCIE总线采用了串行通信连接方式,在其发送和接收时数据使用数据包(Packet)来进行数据传输,很大程度上去除了在PCI总线中存在的某些边带信号,如INTx和PME#等信号。如图6所示为PCIE总线的层次结构,通过其层次结构可知数据包在PCIE总线的收发过程中需要依次通过包括设备核心层、事务层、数据链路层和物理层等在内的多个层次[7]。

图6 PCIE总线的层次结构框图

在某种程度上PCIE的层次结构类似于网络的层次结构,但是PCIE总线的每个层次结构都是通过硬件逻辑来完成实现的。在PCIE总线收发数据的层次结构中,首先报文数据通过发送端设备的核心层中产生,依次经过事务层的封装、数据链路层的可靠性处理和物理层封装后发送至其他设备。接收端设备的物理层接收到数据报文后经数据链路层、事务层处理,最后到达核心层。其中在发送数据时事务层将来自PCIE总线中的核心层的数据封装为TLP(Transaction Layer Packet)后发送至数据链路层;然而在接收数据时事务层的流程与发送数据时恰好相反,是将数据链路层中接收到的数据报文发至PCIE总线的核心层。数据链路层将来自事务层的数据报文添加Sequence Number前缀和CRC后缀进行可靠性处理,保证数据在发送过程中能够完整可靠地进入到其他设备接收端的数据链路层。物理层是PCIE总线的层次结构中的最底层,它将需要PCIE通信的设备连接在一起,同时也是PCIE体系结构中最重要、最难以实现的组成部分,它为数据通信的PCIE设备间提供可靠的传送介质,为数据报文的收发提供一个合法可靠的物理系统环境。

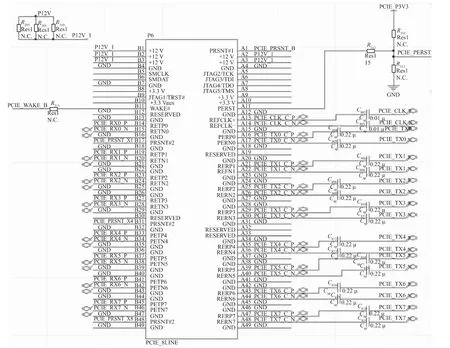

2.3.3 PCIE接口实现

PCIE的物理链路可以由单条或多条Lane组成,当前PCIE可以支持1、2、4、8、16和32个Lane,而总线上的每一个Lane与外部设备间的数据交换速率和带宽与PCIE总线版本相关,以×1为例,PCIE 1.0的吞吐量为250 MB/s,而PCIE 4.0的吞吐量高达2 GB/s,在性能上提升了近8倍[8]。为满足需求,本文采用的是×8宽度的PCIE 2.0链路结构,其电路设计结构如图7所示。

图7 PCIE接口外围电路设计

随着频率的提高,对于PCI并行接口传输出现问题:高速传输的时候,并行的连线直接干扰异常严重,而且随着频率的提高,干扰越来越不可跨越。而在PCIE总线的每一个物理链路中的数据通路中有2条低压差分信号线,一条用于发送,另外一条用于接收。相同内容通过一正一反的差分信号传输,干扰可以很快被发现和纠正,从而可以将传输频率大幅提升,同时PCIE接口是串行全双工通信,那么从频率提高所得到的收益大于一次传输多个bit的收益,而且在PCB设计时布线更简单,也可使用更多Lane整合成为更高带宽的线路。

3 测试与验证

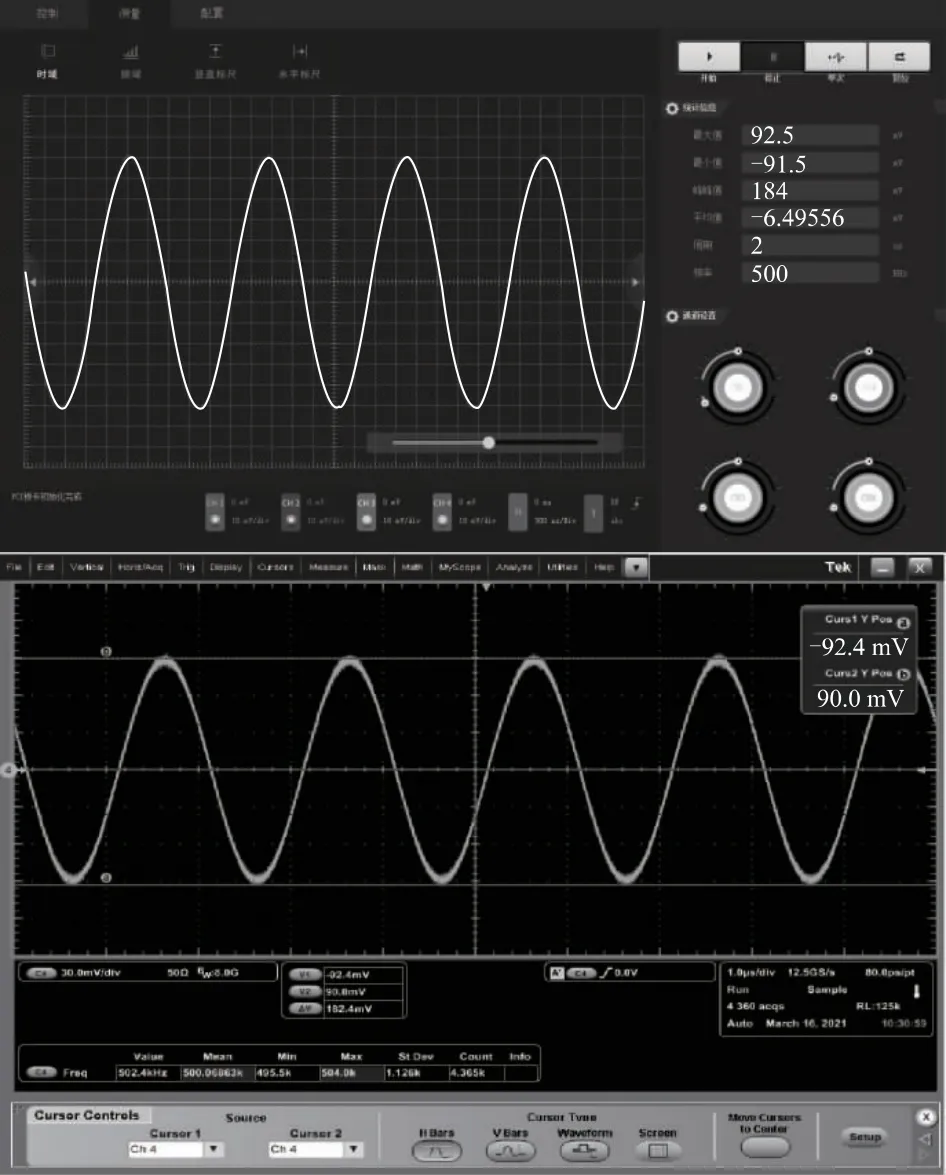

通过DG1022U函数发生器依次输出一个峰峰值为183 mV的500 kHz正弦波信号、5 MHz方波信号和500 kHz三角波信号为该系统提供输入采样信号,其测试结果与原始信号对比如图8、9、10所示,图片上方为实际测量结果,下方为真实信号参数。

图8 正弦波信号虚拟示波器测试对比结果

图10 三角波信号虚拟示波器测试结果

从上述实际测量结果可知本次设计的虚拟示波器能够基本实现传统示波器的测试功能,且实际测量的信号频率大小和幅值大小与真实值基本相同。为了观测实际测量结果与输入信号的误差情况,给定幅值为400 mV、频率大小为500 kHz~100 MHz的输入信号进行测试,实验结果见表1。

4 结束语

通过测试验证,本文基于国产ADC设计的虚拟示波器能够实现高速高精度采样,并具有稳定性好、抗干扰能力强等特点。该系统单路最高采样4 GS/s,双路使用最高采样2 GS/s,同时具有PCIE接口可直接与PC端连接进行数据传输,便于后续的信号处理、数据分析判断和显示以及数据存储。