基于FPGA+FT2232H多通道并行数据USB采集系统设计

2021-09-30杨会伟周先飞

杨会伟,周先飞,李 敏

(芜湖职业技术学院 信息工程学院,安徽 芜湖 241000)

随着电子技术和超大规模集成电路的发展,传感器的种类越来越多,为我们从外界获取各种信息提供了保障。大数据与云计算的出现方便我们从大量的数据中提取准确有用的信息,为了降低信息的误差,通常会对信息进行多次、多点同步采样,然后通过多通道AD将多点模拟信息转换成数字信号进行后期处理,提高信息的准确性。[1-4]

大多的数据处理系统往往通过计算机中专用的数据处理软件来完成。随着USB总线的快速发展,大多数计算机尤其是笔记本接口都被USB总线接口取代。为了快速有效地将多通道并行数据传输至计算机,设计一种基于FPGA+FT2232H多通道并行数据的USB采集系统,实现多通道并行数据向USB串行数据的转换,具有很好的实际意义。

1 系统分析与方案设计

要实现多通道并行数据的USB采集,一方面需要将多通道的并行数据依次进行传输,这需要对每个通道的数据进行缓存,然后进行选通传输;另一方面还需要将每个通道的并行数据转换成USB串行数据,还没有专用的芯片可直接实现并行数据到USB的转换。目前FTDI公司的FT2232B具有 FIFO数据到USB数据转换的特点,结合FPGA的可编程、并行、多IP核等优点可设计实现基于FPGA+FT2232H的多通道并行数据USB采集系统。该系统主要以FPGA作为主控制核心,采用专用的FIFO-USB器件与FPGA连接,通过在FPGA内部定制FIFO数据缓存IP核,再通过FIFO乒乓操作将数据传输至FIFO-USB器件,最终完成多通道并行数据向USB数据的转换。转换成USB串行数据后通过USB数据线传输至计算机进行显示和存储。系统结构如图1所示。

图1 采集系统框图

具体执行流程:(1)系统以FPGA作为主控制核心,前端可连接1~4片8通道16位精度AD模块;利用Verilog硬件编程语言设计该AD模块的控制时序电路逻辑并模块化;(2)利用FPGA内部的存储IP核资源,在FPGA内部建立4个与AD参数匹配的FIFO存储单元,根据实际前端AD模块个数,进行FIFO选通参数设置。例如 :如果只连接一个AD,那么只选通1个FIFO有效,不使用其他3个FIFO,如果连个2个AD,那么选通2个FIFO有效,不使用其他2个FIFO,依此类推。并结合步骤(1)控制时序逻辑电路,将采集的数据依次存储到各个FIFO中;(3)利用Verilog硬件描述语言,采用多分支结构,实现对多个FIFO的选通输出,保证某一时刻只有一个FIFO数据输出;(4)根据FT2232H器件的数据手册,利用Verilog语言编程完成FPGA内部FIFO数据到FT2232H器件数据的传输;(5) 通过专用USB数据线将FIFO-USB模块连接至计算机;(6)上位机软件开发实现人性化软件交互界面,利用FIFO- USB模块成熟的驱动和函数库实现多通道数据的动态显示和存储。

2 系统详细设计

2.1 硬件电路设计

系统主要完成多通道并行数据到USB串行数据转换,电路设计暂不考虑FPGA前端与多路AD 模块的硬件连接,故硬件电路主要包括:FPGA主控单元外围电路设计、FIFO-USB模块FT2232H电路设计、FPGA与FT2232H电路连接。

(1)FPGA电路设计

根据系统需求:在FPGA内部创建1~4个8*16的FIFO核资源,考虑到多通道并行数据转换成USB串行数据的效率要快、外部端口资源丰富、集成度高等因素,系统选用Altera公司65 nm工艺的Cyclon IV系列EP4CE6E22C8型号芯片,其电路主要包括电源模块、外部时钟、串行配置设备电路。

电源模块以外部USB接口5 V电源作为外部输入电压,通过AS1117芯片转换得到FPGA所需的1.5 V内核电压、3.3 V端口电压以及2.5 V锁相环电压,电压与地之间连接0.1 uF的滤波电容;FPGA的串行配置设备选用EPCS4作为FPGA设备串行接口闪速存储装置;外部时钟选择50 MHz外部时钟。

(2)FT2232H电路设计

FT2232H是具有通道A、通道B的两通道高速USB2.0 芯片,可支持FT232异步串行接口、FT245 FIFO接口、处理器型FIFO接口以及快速串行接口多种模式。这些模式可在复位后通过外接EEPROM芯片中配置信息进行模式选择。其外围电路主要包括:3.3 V IO电压和1.8 V内核电压,为了系统的安装调试方便,统一采用USB接口5 V电压转换得到;根据需求外接12 MHz晶振;EEPROM配置模块采用93C46芯片,通过IIC总线与FT2232H连接;FT2232H输出的USB数据通过专用的两个USB引脚DM、DP连接至外部USB接口。

(3)FPGA与FT2232H电路连接

本系统主要实现多通道并行数据的USB采集,根据需求,确定采用FT245异步FIFO模式。在该模式下,只有A通道为有效数据通道,用到的主要引脚包括:①双向A通道8位宽度数据总线ADBUS[7:0];②读FIFO数据有效控制信号RXE#,写FIFO数据有效控制信号TXE#;③FIFO读使能信号RD#,FIFO写使能信号WR#,这些信号都是低电平有效;④有效数据USB输出控制信号SIWU,该信号与PWREN#信号结合使用,将FT2232H的PWREN#信号引脚连接外部的下拉电阻,固定为低电平,使FT2232H工作在正常模式下。FPGA与FT2232H电路连接如图2所示。

图2 FPGA与FT2232H电路连接框图

2.2 时序控制设计

FT2232H作为高速USB2.0 芯片,在FT245异步FIFO模式下可自动完成FIFO与USB间转换传递,但是为了保证有效数据传递的正确性,需要编写时序控制程序。在FPGA内部,通过Verilog语言编程建立FIFO选通数据输出控制模块和FIFO-USB控制模块。如图3所示。

图3 FIFO-USB接口转换模块及内部电路连接图

(1)FIFO选通数据输出控制

系统前端连接4片8通道16位精度AD模块,在FPGA内部建立了4个FIFO存储单元分别用于缓存4片AD采样数据,4个FIFO通道数据需要经过FIFO数据选通模块完成循环交替输出。FIFO数据选通模块主要通过建立iA0-iA4四个选通控制信号,结合多分支结构if…else if…else完成多FIFO的循环交替输出。

(2)FIFO-USB控制[5-9]

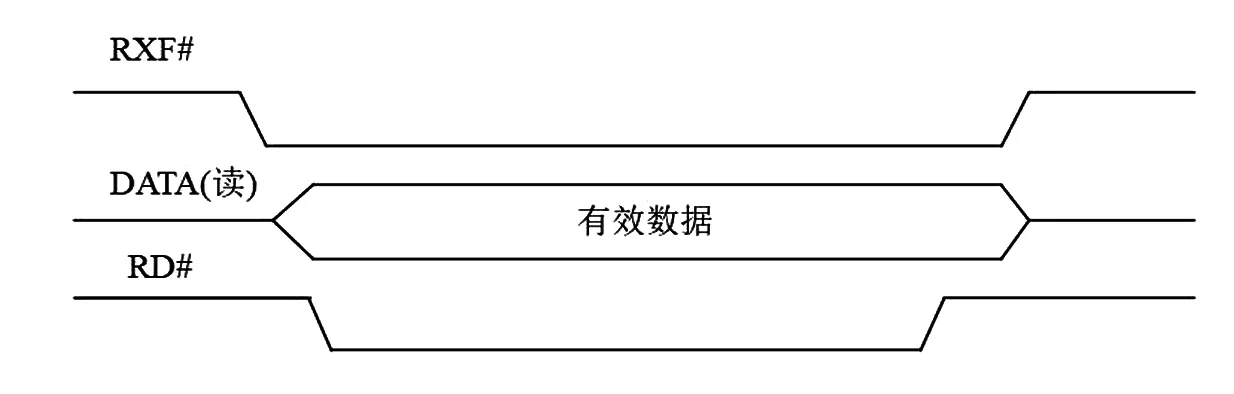

FIFO数据到USB转换控制主要通过ADBUS[7:0]、RXE#、TXE#、RD#、WR#、SIWU信号来完成。其中,RXE#、RXE#信号由FT2232T产生,RD#、WR#、SIWU由FPGA编程提供。读写控制时序如图4、图5所示。

图4 FT245异步FIFO接口读时序

图5 FT245异步FIFO接口写时序

设计思路如下:①首先通过FPGA将PWREN#信号设置为高电平,使FT2232处于正常模式;②将SIWU信号设置为1,使设备发送到缓冲区的任何数据都要通过USB接口发送出去,提高数据传输效率。③读操作:判断从FT2232发出的TXF#信号,当该信号为低电平时,每从FIFO选通数据输出模块读取一个通道数据,就生成一个WR#低电平脉冲给FT2232;在WR#为低电平的时间内,将16位的AD数据通过ADBUS[7:0]上传至FT2232芯片中,完成16位并行数据到USB数据的传输,数据的传输格式为:高8位、低8位分别发送,并且在低8位和高8位数据前加上1个字节的校验数据,以保证数据传输的正确性。④写操作,判断从FT2232发出的RXF#信号,当该信号为低电平时,生成一个RD#低电平脉冲给FT2232,并在RD#为低电平的时间内,通过ADBUS[7:0]读取FT2232内部FIFO数据到FPGA内部,完成USB数据到并行数据传输。

3 上位机软件设计与测试

3.1 上位机软件设计

FTDI公司为USB-UART和USB-FIFO提供了两种可供选择的软件接口。一个软件接口提供了一个虚拟COM端口(VCP),它在系统中显示为一个遗留COM端口;另一个软件接口D2XX是通过一个专用DLL (FTD2XX.DLL)提供的,该软件接口提供了十分完整的库函数和驱动程序,支持VB.net、Visual C++6.0、LabView多种软件开发环境。由于VB.net开发环境可视化编程效果好,并且对FTD2XX.DLL操作方便,本设计选用VB.net完成USB上位机数据的采集显示与存储。

具体设计流程如下:①通过调用库函数FT_Open打开USB设备,根据返回值判断是否打开成功,若打开成功,设置USB的波特率和读写功能,建立读线程pThreadRead = New Thread (AddressOf ReadThread);②然后通过对USB端口进行初始化,设置波特率、清除输入输出缓存和访问超时时间;③创建读线程并启动;④执行数据读线程ReadThread,调用库里的读函数FT_Read提取有效数据,并将各个通道数据分离出来;⑤将各个通道的数据经过处理后动态显示出来,并利用StreamWriter()将各个通道数据写入文件中进行动态保存。

3.2 数据采集测试

将多通道并行数据的USB采集系统的USB接口与计算机的USB接口相连,打开电源;打开上位机软件,选择通道A的USB转FIFO模式,选择HEX格式显示接受的内容,打开USB设备,开始采集数据,采集界面如图6所示。

图6 系统数据采集界面

本次测试共完成5个标准电压值的16通道采样,然后计算16通道采样的平均值作为测试值,采样结果如表1所示。

表1 16通道采样表

测试结果表明:本采集系统能够完成十六通道并行数据到USB接口的转换,均值采样绝对误差约为0.000 8 V,可满足电力线监控、多相电机控制、仪表控制等领域应用需求。

4 结语

传统的数据采集往往采用并行数据转RS232串口来完成,传输效率低。目前大多数计算机尤其是笔记本都利用高速的USB接口取代了RS232串口,基于此,设计一种基于FPGA+FT2232H多通道并行数据的USB采集系统,实现多通道并行数据向USB串行数据的转换。采用FPGA作为主控单元,充分利用了FPGA的可编程、并行、多IP核的优点,简化外部硬件电路设计,降低分立器件的数量,系统体积小、功耗低、抗干扰强,稳定性高;利用Verilog语言并行特点保证多个任务模块同步并发执行,提高数据传输效率;上位机采用可视化编程开发环境VB.net,可实现人性化的软件交互界面,利用FIFO- USB模块成熟的驱动和函数库实现多通道数据的采集,采样绝对误差约为0.000 8 V,准确性和稳定性高。在多通道数据采集、处理领域具有一定的应用价值。