基于CRC+ECC 双校验的高速长线LVDS 传输设计

2021-09-08甄国涌陈晓锦

甄国涌,陈晓锦,王 迪

(1.中北大学仪器科学与动态测试教育部重点实验室,太原 030051;2.空军装备部驻太原地区军事代表室,太原 030051)

0 引言

现代测试领域对数据传输的速度、传输距离和可靠性有着越来越高的要求。在远距离数据传输时,串行传输较并行传输有着可靠性高、成本低以及布线简便的优势,所以一般采用串行传输的方式 。但是一般的串行传输速率往往达不到特定测试领域的设计要求,而LVDS 传输技术采用极低的电压摆幅高速差动地传输数据,在满足高速传输的同时具有低功耗、低误码率等优点[2]。但是LVDS信号自身的传输距离极短,仅有几米,若在可靠性不降低的情况下增加传输距离,势必要在硬件和逻辑进行适配。

本文设计中,硬件设计上在LVDS 发送端添加驱动电路,提升信号压差,延长信号传输的距离。在LVDS 接收端加入自适应均衡器,补偿因长距离传输LVDS 信号在传输介质中引起的信号衰减[3]。同时在逻辑设计中引入CRC+ECC 双校验结合的方式,既利用了FPGA 并行传输特性消耗极少的时钟资源,同时又提高了单校验方式下数据传输的准确度,解决了LVDS 信号在长距离高速传输时可靠性较低的问题。

1 整体设计方案

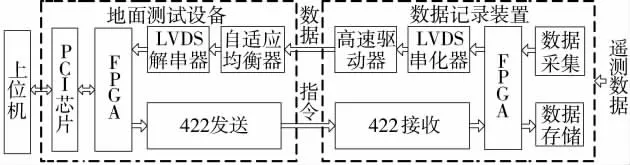

该数据传输系统主要是由数据记录装置、地面测试设备以及上位机组成。如图1 所示,其中数据记录装置主要是将飞行器的遥测数据编码存储起来,地面测试设备主要是回读存储起来的遥测数据,上位机软件对遥测数据执行回读指令并进行数据分析。

图1 系统整体设计框图

为实现地面测试设备高速回读数据记录装置存储的遥测数据的要求,接口选用LVDS 高速数据接口。在数据发送端使用,可将由FPGA 发出的高速并行数据转化为串行数据的LVDS 串化器,转化为串行数据可有效延长数据的传输距离。为增强LVDS 信号的驱动能力,在数据发送端增加高速驱动器,同时为补偿LVDS 信号经过长距离传输而引起的衰减问题,在数据接收端使用自适应均衡器以提供补偿[4]。

2 硬件电路设计

2.1 LVDS 信号发送端设计

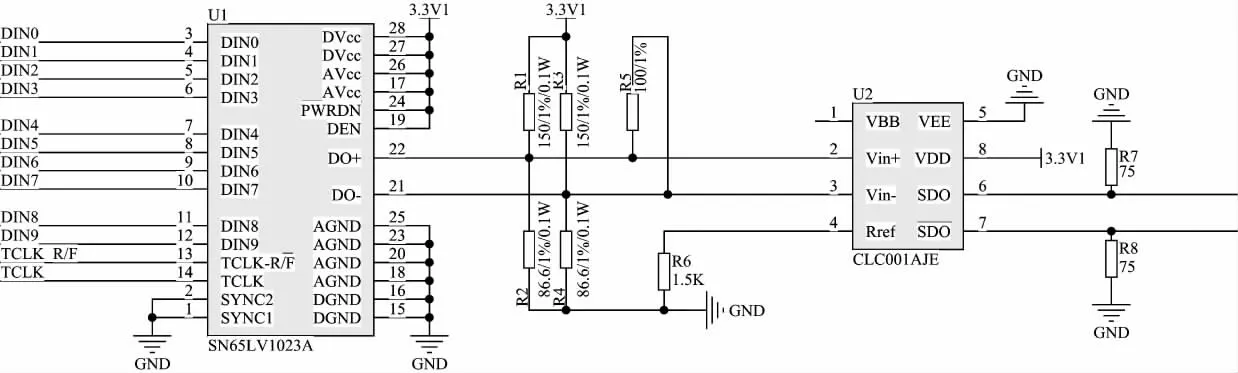

在LVDS 发送端的硬件电路设计中选用SN65 LV1023 作为发送芯片,其数据传输速率为100 Mb/s~660 Mb/s,满足设计要求。该芯片将FPGA 输出的并行10 位信号经内嵌时钟后转化为串行输出,有效降低了由于数据和时钟不同步造成的误码错误[5]。但是差分信号经SN65LV1023 输出的压差仅200 mv,芯片传输距离仅10 m,不能达到长距离传输的要求。因此,想要实现在双绞电缆中的长距离传输,就需要传输端加入驱动器来补偿因传输介质的衰减和相位延迟而导致的信号摆幅不足问题。

CLC001AJE 为一款数据传输速率可达622 Mbit/s的高速驱动器,差分输入的门限电压为100 mv,输出电压的压差为1.6 V~2 V。作为发送端的驱动器,就是将信号作预加重处理,把沿信号的幅度增强,从而达到提高信号高频分量的效果[6]。因此,在LVDS发送端增加高速驱动芯片CLC001AJE 将输出信号压差提升至2.3 V,有效增加沿信号的摆幅,达到了延长LVDS 信号传输距离的目的。具体LVDS 传输端电路如图2 所示,LVDS 输出信号的电压值可由外部电阻R6 调节,R5 取100 Ω/1 %的端接电阻用来对驱动线路进行阻抗匹配。

图2 LVDS 信号发送端电路

2.2 LVDS 信号接收端设计

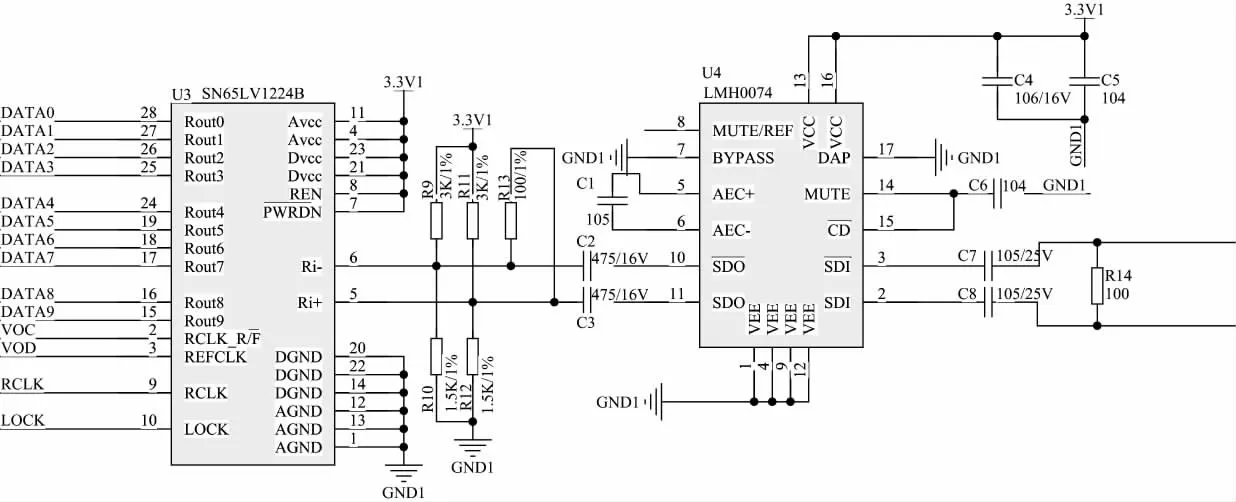

选用SN65LV1224 解串芯片作为LVDS 接收芯片,SN65LV1224 芯片可解析出串行数据中内嵌的时钟信号并将串行数据转化为并行数据传输到FPGA。LVDS 信号的传输介质为双绞屏蔽线且百米内的传输阻抗小于10 Ω,因此,输入信号在进入解串芯片前还需进行输入电平控制和100±10 Ω 的阻抗匹配。正因为传输线引起的损耗与信号传输速率成正比,所以设计中信号传输速率在百兆级的情况下,线缆200 Hz 时的信号衰减约为37 dB,属于有损传输线。

由于传输介质的传输函数具有低通特性,信号在介质中的传输速率会慢于信号的低频分量,使得接收到的信号幅度降低,脉宽变大,在传输过程中信号的高频部分会受到一定的幅值衰减以及相位时延。若在连续无变化的信号中出现一个切换脉冲,则接收端的部分信号会因摆幅不足直接影响数据信息的有效读取,造成码间干扰[7]。因此,在接收端前加入均衡电路,来补偿电缆对信号的衰减,达到降低误码率、提高传输数据可靠性的目的,具体电路设计如图3 所示。

图3 LVDS 信号接收端端电路

设计中采用的LMH0074 是一款可自动补偿传输速率为143 Mbit/s~540 Mbit/s 的自适应电缆均衡器,其内部包含一个均衡滤波器,一个判决器和自偏置直流整形电路部分。差分信号经过均衡滤波器后,将进入自偏置直流整形电路的信号分成两部分,一部分相当于缓冲器实现单位增益,作用是达到延迟匹配,另一部分实现高频加强,来补偿传输介质上的高频损耗。两部分信号最终作为判决器的输入,通过与判决器的设定幅值比较,输出符合要求的沿信号。信号在自偏置直流整形电路的前级和后级可生成一种自动均衡控制(AEC)信号,该控制信号可跨AEC+和AEC 引脚放置一个1pF 电容来外部控制均衡滤波器的增益和带宽,还可以滤除比较后输出中含有高频噪声。

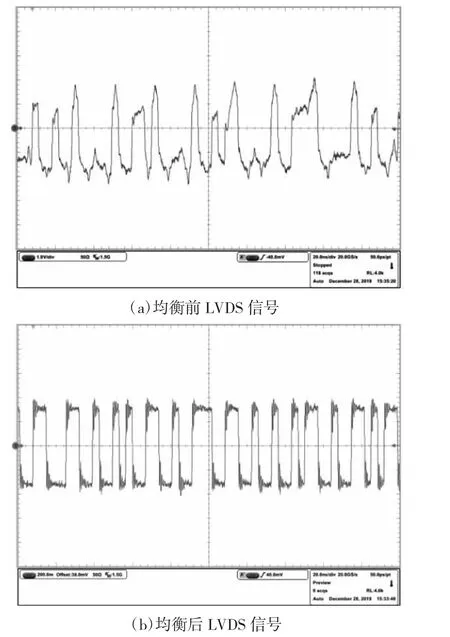

经SN65LV1224 直接对信号进行解串会导致得到的部分信号无法判断处于高电平或是低电平,使数据出现错误,如图4(a)所示。而加入LMH0074 均衡器可将解串信号恢复,将信号摆幅的高低电平基本保持一致,使接收端电位信息明显辨别,如图4(b)所示。

图4 均衡前后对比图

3 软件设计

3.1 CRC 校验逻辑实现

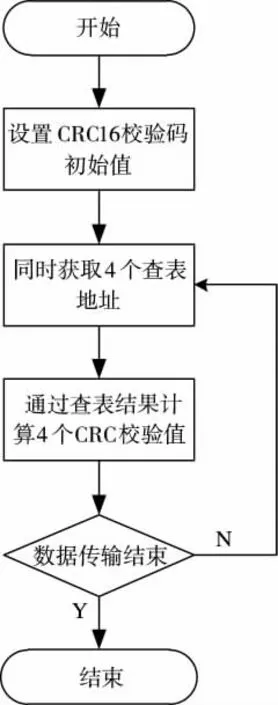

数据以1 024 B 为一包,为保持较高的检错率在逻辑设计时选用CRC16 校验方法。对于数据量较多的运算,传统的逐位串行运算校验速率较低,耗费时钟周期较长。而通过使用查表法CRC 运算可并行处理接收的数据,效率较高,适合大量数据校验[8]。CRC16 半字节查找表校验流程图如图5 所示。

图5 CRC16 半字节查找表校验流程图

在LVDS 传输过程中发送端和接收端都进行CRC 校验,若校验后两端结果不一致,则表明在数据传输过程中出现误码或丢数现象,反之,则说明LVDS 数据在传输过程中无错误。

3.2 ECC 校验逻辑实现

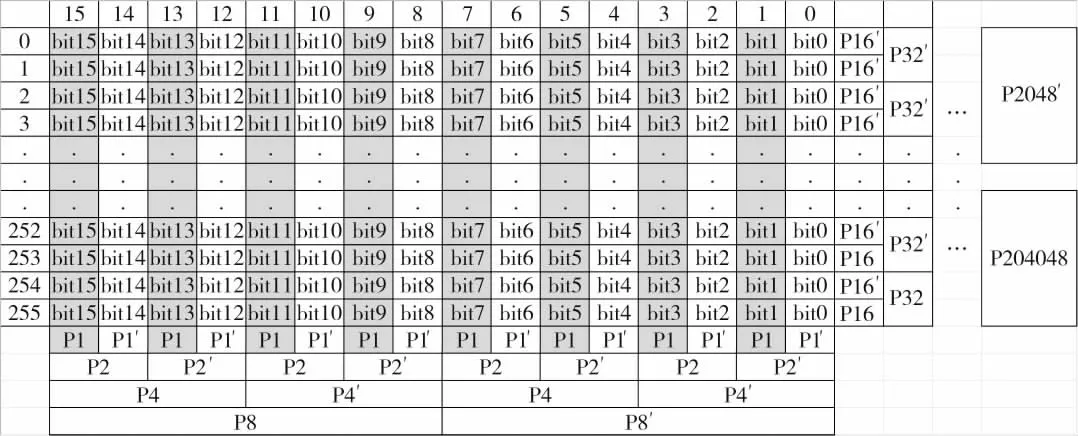

ECC 校验是通过将数据块的行、列的奇偶信息生成校验位来对数据进行检验,纠错[9]。ECC 校验方法可以对一位错误纠错,可以检验出两位错误但是无法纠正。ECC 校验示意图如图6 所示。

图6 ECC 校验示意图

ECC 校验过程为:首先将需发送的数据块中的数据字按位异或,将得到的异或结果与P1、P1'、P2、P2'等异或,得到列校验码。每次发送完成数据字后便将该字与P16、P16'、P32、P32'等异或,得到行校验码。当数据块中的数据字发送完成后,计算的结果即为该数据块的ECC 校验值。将LVDS 信号发送端和LVDS 接收端计算的ECC 校验码根据奇偶位可分为4 组12 位校验码。

其中,ECC_result 为数据的ECC 校验值。若ECC_result 的结果为“0”则表明该数据块中数据字全部正确,结果为“1”则表明数据块中存在1 位错误,结果为其他值表示数据中存在多位错误。ECC 纠错方法:ECC_addr <=ECC_tx_odd xor ECC_rx_odd,得到的结果中高8 位表示错误的字地址,低4 位表示出错的位地址。通过地址找到出错的位置取反即可纠正[10]。

3.3 双校验逻辑实现

双校验逻辑实现流程为:在收发两端,LVDS 数据的发送和接收都以1 024 B 为一包数据。当发送端将一包数据发送完成后紧接着发送这一包数据的双校验码,接收端在接收数据的同时计算该包数据的双校验码,在接收端接收完成一包数据后首先判断发送端发送的CRC 值与接收端接收的CRC 值是否一致,如果CRC 校验值一致表示数据正确,准备接收下一包数据。若CRC 校验值不一致,则通过对该数据包的ECC 校验码进行判断,并计算出该数据包中数据出错的位置,若ECC 判断错误位数较少可纠正,则对该出错数据取反纠正。若错误位数较多,不可纠正,则数据接收端向发送端请求重传本包数据。

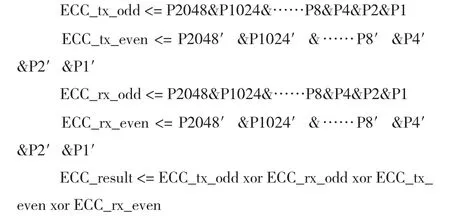

3.3.1 发送端逻辑实现

LVDS 发送端采用乒乓操作的方式进行数据发送,发送端首先发送RAM1 中的数据,当数据发送完成后紧接着发送2 个ECC 校验值和1 个CRC 校验值。当RAM1 中的数据以及双校验码发送完成后,发送端紧接着向RAM2 缓存下一包数据并等待接收端的重传请求,如果无重传请求,数据发送端将RAM2 中缓存的数据读出并发送。若发送收到重传请求,则再次将RAM1 中的数据读出并发送。为保障数据的传输效率,发送端在第2 次发送完成后,不再等待重传请求直接开始发送下一包数据,发送端工作流程图如图7 所示。

图7 发送端工作流程图

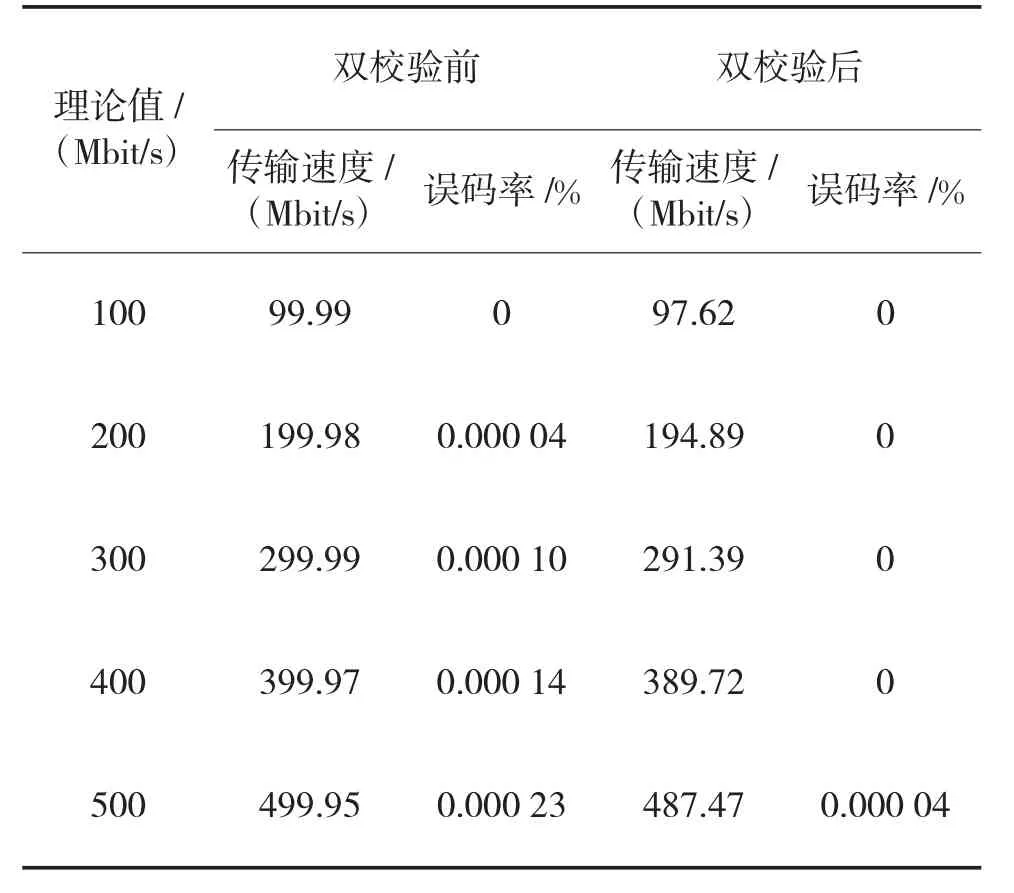

3.3.2 接收端逻辑实现

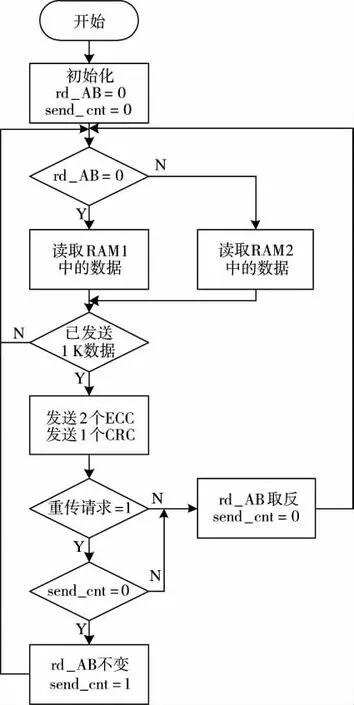

数据接收端将收到的LVDS 数据写入RAM中,并计算这一包数据的CRC 和ECC 校验值,如果CRC 校验值一致表明接收到的数据包正确,不需要纠正或重传,等待接收下一包数据。若不一致则根据ECC 校验值判断出错的位数,如果出错的位数为一位,根据ECC 校验结果计算出错的位置并进行取反纠正否则请求重传。接收端工作流程图如图8 所示。

图8 接收端工作流程图

3.4 双校验逻辑效率分析

对于校验算法无论CRC 校验、ECC 校验或双校验算法,不能过多的消耗数据传输的带宽,需保证原有数据正常传输,必须考虑数据校验、纠错以及重传对时钟的消耗[11]。

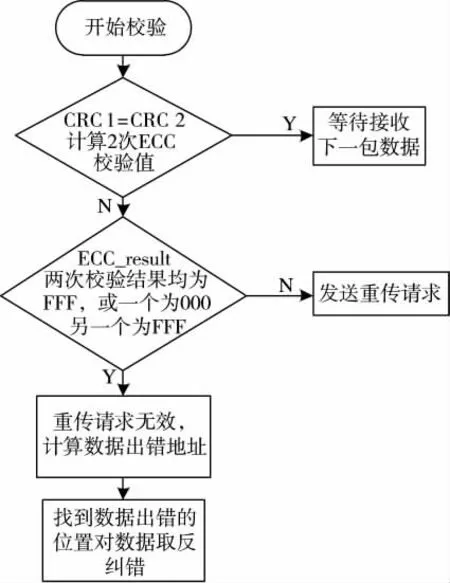

对于数据的检错和纠错必然会导致数据传输速率的降低,但是在FPGA 中进程都是并行执行的。在数据发送端和接收端,数据发送、接收以及数据校验都可同时进行,不会占用过多的时钟资源。采用双校验算法和只使用ECC 校验算法分别对1 k数据进行校验所消耗的时钟资源如表1 所示。由表中数据可知,在数据正确或数据错误的情况下双校验算法都比ECC 校验算法节省时钟资源。

表1 双校验和ECC 校验消耗时钟对比

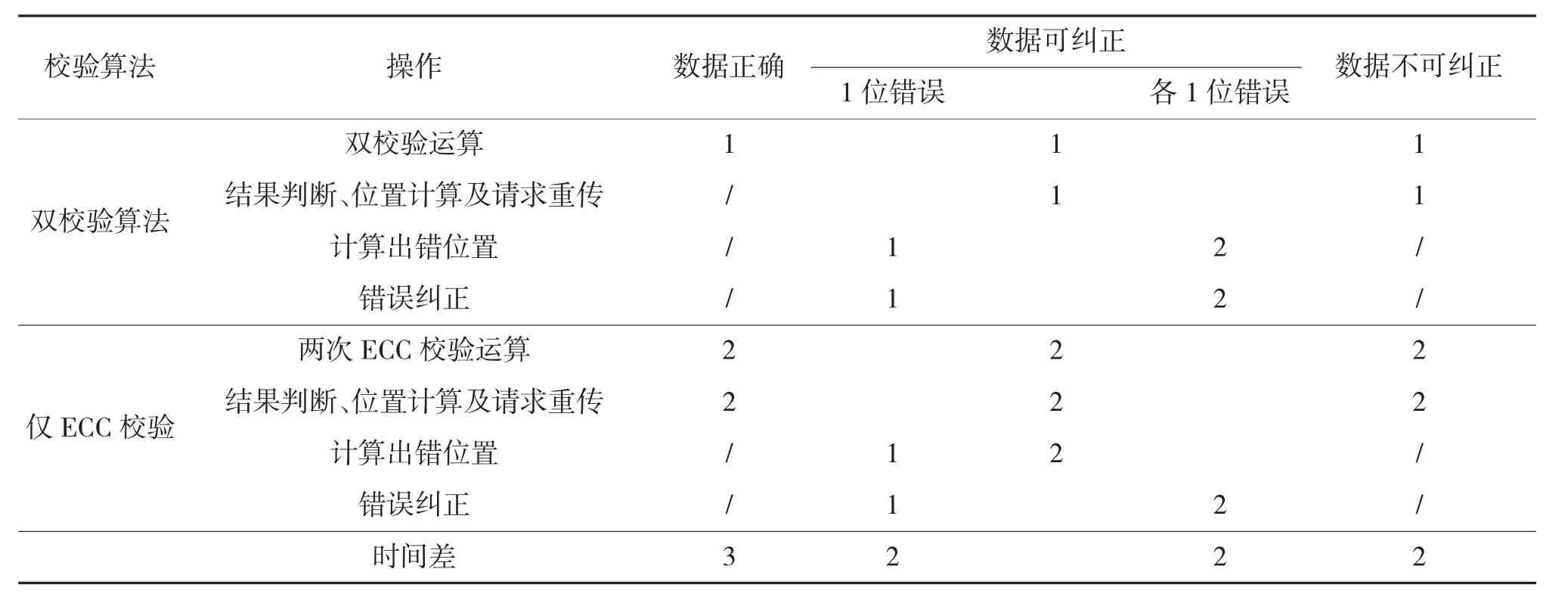

4 试验验证及分析

为验证双校验算法的可靠性,使用采编设备、地面测试台、上位机构成一个闭环测试系统。使用5段15 m 电缆串接为一条75 m 电缆,采编设备通过75 m 电缆向上位机软件发送LVDS 数据。通过修改发送端程序,分别测试在100 Mbit/s,200 Mbit/s,300 Mbit/s,400 Mbit/s,500 Mbit/s 发送速率下的误码率,测试结果如表2 所示。

表2 测试结果

由表2 中的数据分析可得在不加任何校验算法的情况下,硬件电路可以在传输速度为100 Mbit/s,传输距离为75 m 的情况下可以无误码发送,但是随着发送速率的增加,误码率也在增加。在加上双校验算法后,传输速度会明显下降,传输速度在400 Mbit/s及以下时可保证数据传输的可靠性。

5 结论

本文针对数据在高速远距离传输时存在损耗大、数据传输可靠性低的问题,设计了基于双校验算法的高速长线LVDS 传输系统。在延长LVDS 传输距离的同时,在数据链路发送端和接收端的电路设计上,使用预加重处理+均衡处理的方式保证了数据传输的可靠性。逻辑上采用CRC 与ECC 双校验结合的方式,提供了数据在高速传输时多错重传,少错纠正的技术支持,同时也降低了校验算法对数据传输时的带宽损耗。经试验验证,基于双校验算法的高速长线LVDS 传输系统在消耗少量带宽资源的情况下,可实现在75 m 双绞屏蔽线缆上的信号高速可靠传输,速率可达400 Mbit/s,同时降低了硬件、人力时间成本。