基于高速信号采集系统累加平均算法研究

2021-09-07潘冬阳南钢洋

潘冬阳,南钢洋,白 雪

(齐鲁工业大学(山东省科学院)山东省科学院激光研究所,山东济南 250353)

0 引言

随着信息数字化程度的提高,对信号采集与处理系统也有着更高的性能要求。当前,密集型数据处理能力、并行计算能力以及数据高速传输能力,成为衡量信号采集系统优劣的重要因素。在一些背景噪声复杂的环境下,如光纤传感检测[1]、电磁超声检测等[2],还需要系统具有良好的抗干扰能力。目前常见的信号降噪方法有小波变换算法和累加平均滤波算法[3-4],两种算法的实现大多依靠软件对采样数据进行处理,缺乏实时性且需要处理的数据量较大[5-6]。而FPGA(field programmable gate array)采用并行流水线架构,拥有灵活的可编程逻辑单元,适用于流式的计算密集型任务[7]。目前市面上的信号采集系统大多不能实现触发频率的自适应,一旦触发频率变化,将可能影响系统正常使用。因此本文基于FPGA设计一种触发频率自适应的累加平均滤波算法,采用两级RAM缓存数据,可以在实时并行累加过程不中断的同时,读取最终平均结果,实现重复模拟信号并行流水线高速采集与处理,进而提高了数据处理的实时性。

1 累加平均滤波算法原理

假设输入信号f(t)是由周期目标信号s(t)和随机噪声信号n(t)构成,表示为

f(t)=s(t)+n(t)

(1)

此时输入信号信噪比为

(2)

式中:S为目标信号功率;N为随机噪声信号功率。

若对输入信号经过m次累加再取平均值,则目标信号s(t)累加平均后的输出为

(3)

式中:k为当前累加次数;i为目标信号周期内某一采样点;T为采样周期。

对于随机噪声n(t)累加平均后的输出为

(4)

(5)

可见,累加次数m越大信噪比越高[8]。所以通过增加累加次数,可以有效提高信噪比,改善滤波效果。

2 算法的流水线架构设计

为提高累加平均滤波算法运行速度,在并行加法器和RAM地址计数器后插入寄存器组,构成并行流水线结构,流水线结构是将规模较大的组合逻辑分成时间上前后相连的多级处理片段,在片段之间插入寄存器组缓存中间数据,上一级的输出是下一级输入的无反馈电路,多级缓冲构成流水线。采用流水线结构处理算法,可以将原来的运算量分成多个部分,当任务通过了流水线的第一级,新任务就可以进入流水线,因此减小了每一级的操作时间,且各级操作并行执行,缩短了数据处理关键路径延时,提高数据处理速度[9-10]。

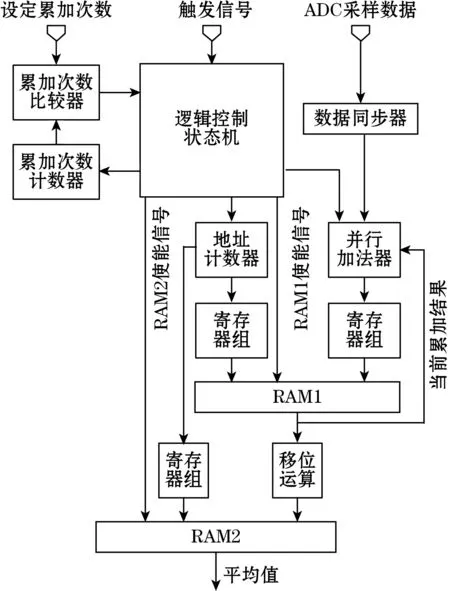

当前采样数据与当前累加结果进行对应点依次累加,在累加完成的同时,将本次累加结果经过寄存器组同步存入RAM中,然后再进行新一轮累加。算法架构图如图1所示,信号经ADC转换成实时采样数据,并将数据按全局时钟节拍经两级寄存器组进行同步处理,降低亚稳态。而后通过并行加法器作累加运算,累加结果存入一级缓存RAM1,平均后的结果存入二级缓存RAM2。整个算法的控制逻辑由状态机完成。

图1 算法架构图

3 累加平均滤波算法实现

3.1 逻辑控制状态机实现

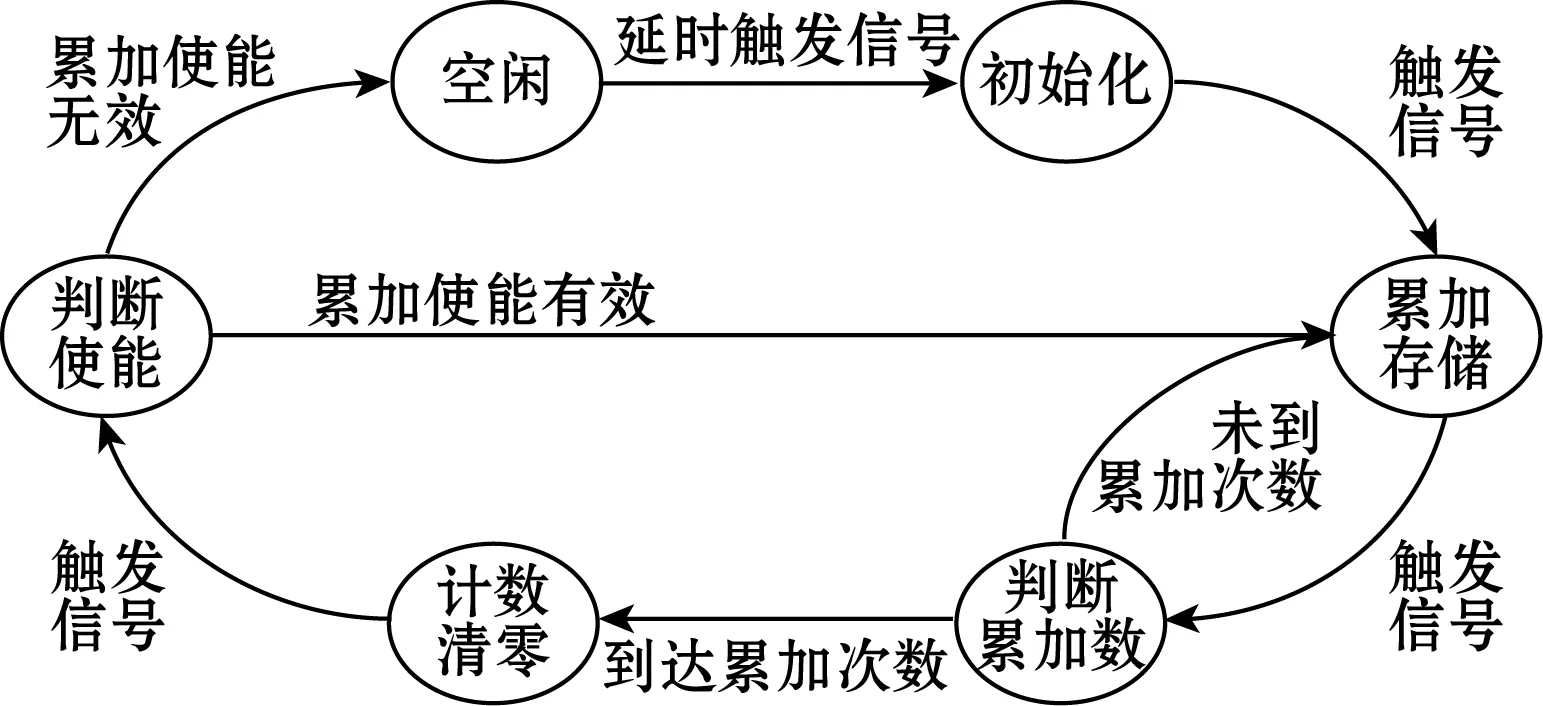

状态机由外部触发信号驱动,自适应触发频率,控制加法器的启停,RAM地址计数器使能和清零,累加次数计数器使能和清零,以及RAM读写使能等,其状态转移图如图2所示。

图2 状态转移图

在空闲状态等待延时触发信号,该信号由外部脉冲触发信号延时所得。由于从触发信号的发出到ADC输出有效数据有一定延时,所以需要对ADC作延时补偿,确保ADC有效数据和触发信号同步。延时触发信号到达后,跳转到初始化状态,初始化RAM1地址和计数器等变量,并将第1次触发后的采样数据写入RAM1,等待下一次触发;第2次触发信号到达后,跳转到累加存储状态,并进行前2次触发采样数据的累加和存储,新的累加结果写入RAM1,将之前数据覆盖。

从第2次触发信号以后,每接收到一次触发信号,状态先由累加存储状态跳转至累加数判断状态,比较设定的累加次数和当前累加次数,若未到达设定的累加次数,则跳回累加存储状态继续进行累加和存储;若到达累加次数,则跳转至计数清零状态,给出累加完成标志信号,并清零累加计数器和地址计数器,完成一轮累加过程;新一轮触发信号产生后,跳转到使能判断状态,判断累加使能信号,信号有效则直接跳转至累加状态继续循环累加工作,否则跳回初始空闲状态。系统中与状态机相关的指令见表1。

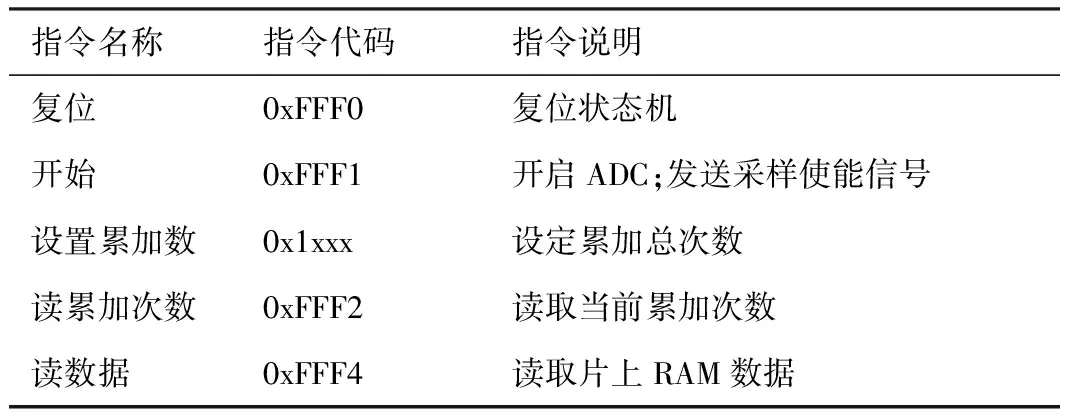

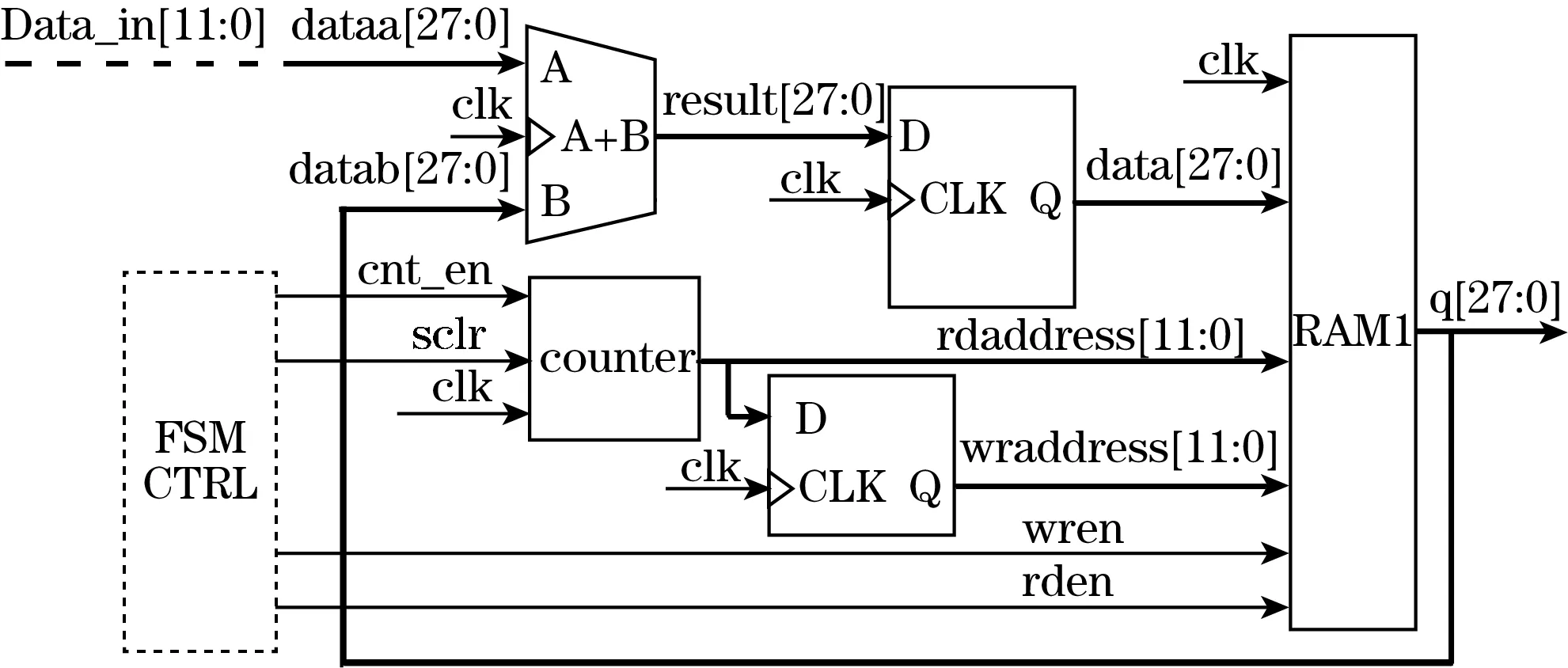

表1 状态机指令表

3.2 数据运算和存储

数据运算主要分为累加运算和平均运算部分。累加运算由一个并行加法器完成,ADC采样的数据位宽为12位,在经过最高65 536次累加后,数据位宽将达到28位,为满足计算要求,加法器输入输出端均为28位数据。当前累加结果经寄存器组同步后存入RAM1中;再次累加时,将RAM1中的当前累加数据读出,与新输入的数据进行累加,以此迭代。累加运算部分RTL(register transfer level)结构图如图3所示。

图3 累加运算部分RTL图

在做平均运算时,考虑到用FPGA硬件逻辑实现除法运算会产生复杂的冗余电路,占用过多逻辑单元,故采用移位运算代替除法运算。根据系统设计,可设定的累加次数为2N,N最大为16,即65 536次,将2N次的最终累加结果右移N位,便可实现取平均值的运算。

由于采用RAM1和RAM2两级缓存,使得数据累加和读取平均数据能够并行执行。根据算法设计要求,外部触发信号频率最小为5 kHz,当ADC采样速率为100 MSPS时,每次触发的采样点为20 000个;可以设定RAM1的最大存储深度为20 000。而12位的ADC采样数据,在经过2N次累加后,数据和值的位宽最大为12+N,因此用于存储累加结果的RAM1位宽为12+N。当N为16时,RAM1存储大小为70 KB。平均后的数据存储在RAM2中,需要存储最多20 000个12位采样点,大小为30 KB。

4 算法验证

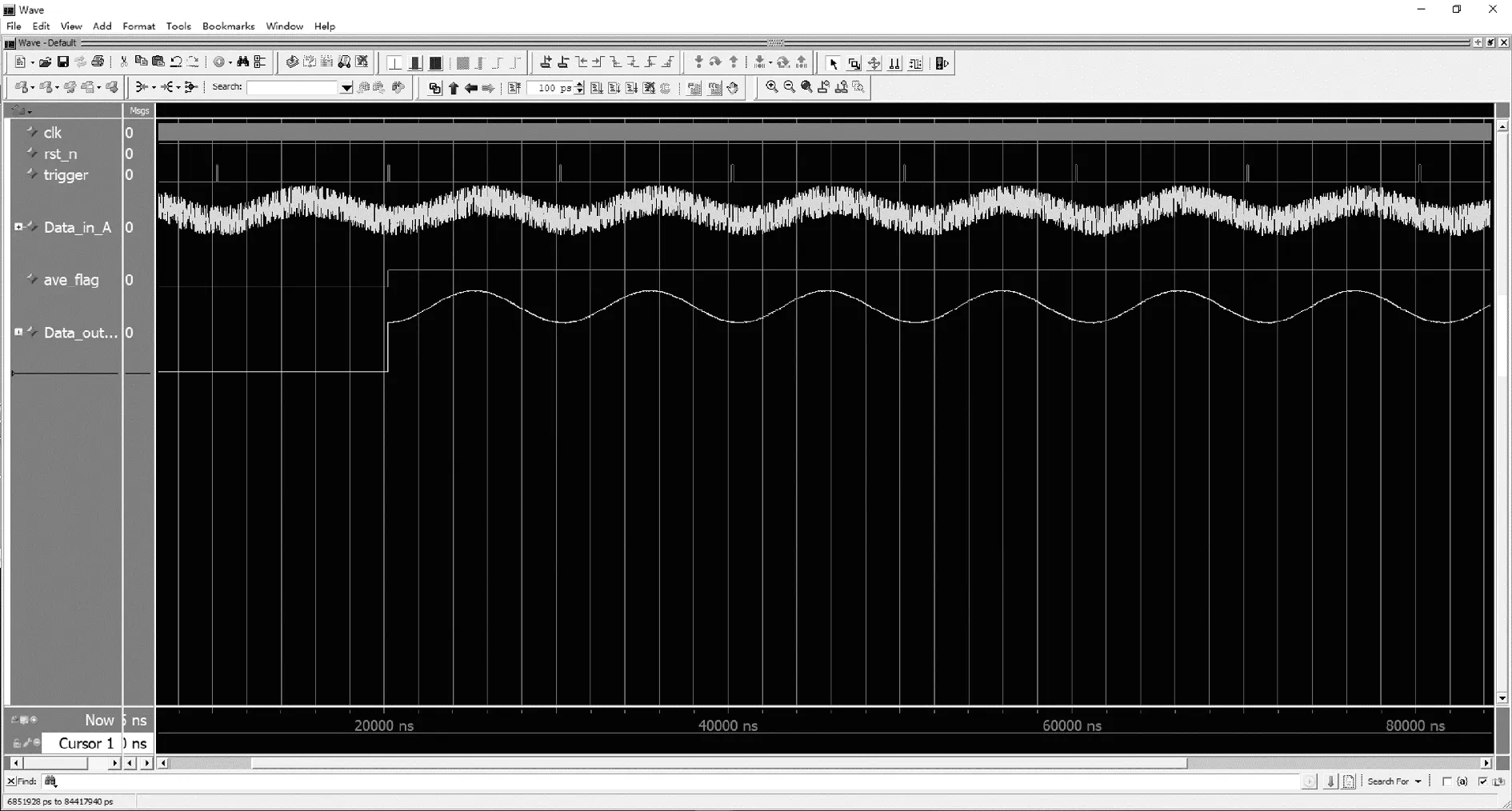

4.1 软件仿真验证

使用ModelSim对算法进行调试仿真,设定触发信号频率为100 kHz,全局时钟信号频率为100 MHz,给出算法需要的复位信号,以及叠加了随机噪声的正弦波信号作为输入。当设定累加次数为4 096次时,平均滤波后输出的正弦波形如图4所示,所得波形受噪声影响明显减小。图5为设定65 536次累加平均后的输出结果,所得波形已基本趋于平滑正弦波形。

图4 4 096次累加平均仿真结果

图5 65 536次累加平均仿真结果

仿真结果表明,上述累加平均滤波算法可有效减少噪声对重复信号的影响,且随着累加次数的增加,滤波效果越明显。

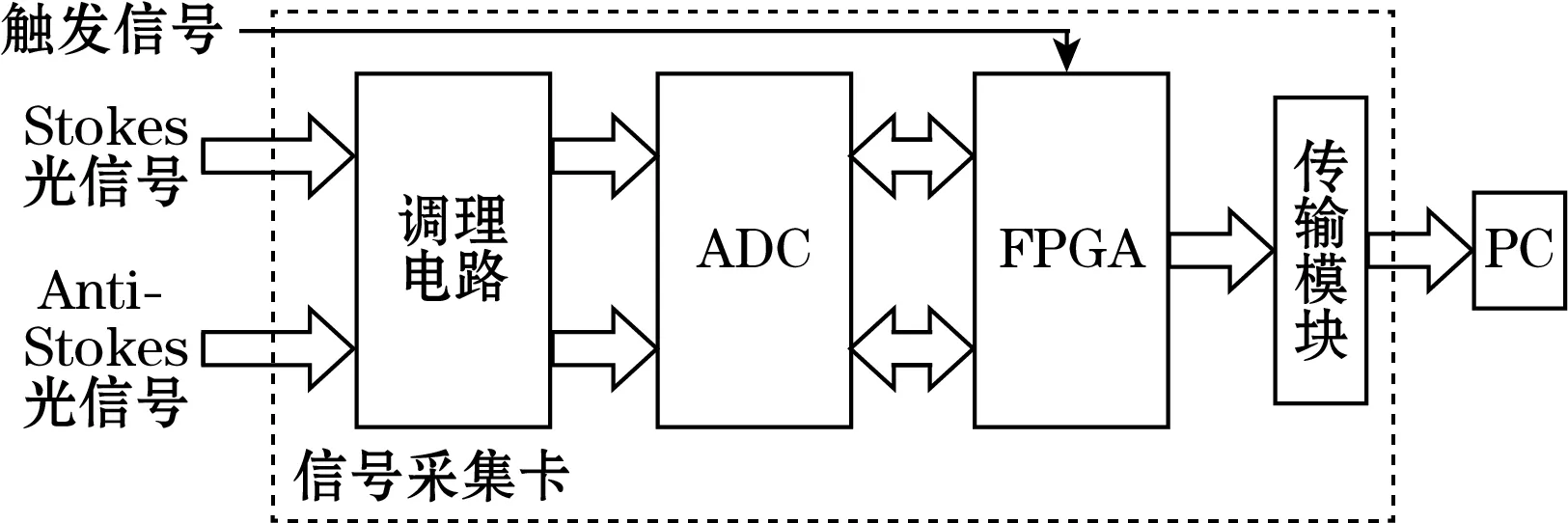

4.2 光纤信号采集系统验证

利用搭建的光纤信号采集系统,将算法在该系统中验证。系统整体结构如图6所示,光纤反射的Stokes光信号和Anti-Stokes光信号经调理电路后,由ADC高速采样并转换为12位数据,送入FPGA作累加平均滤波处理,再由传输模块发送到上位机进行进一步处理及显示。FPGA使用Intel EP4CE115系列芯片,ADC采样速率为100 MSPS,触发信号频率为10 kHz。

图6 光纤信号采集系统架构图

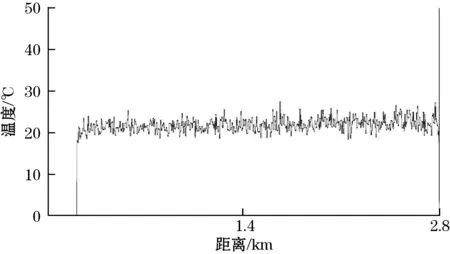

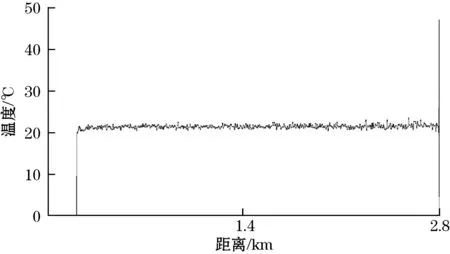

图7和图8分别为经过4 096次和65 536次累加平均滤波,并通过上位机运算处理后的光纤温度信号波形图。从图中可明显观察到累加次数越高,信噪比提高越多。经过计算,后者比前者提高了约5 dB,验证了上述累加平均滤波算法的有效性。

图7 4 096次累加平均波形图

图8 65 536次累加平均波形图

5 结束语

本文实现了基于FPGA的累加平均滤波算法。针对累加平均滤波算法的特点,采用FPGA流水线结构设计算法整体架构,通过逻辑控制状态机实现算法对触发信号自适应,利用两级RAM进行数据的高速采集和并行处理。由于采用硬件实时处理,显著压缩了数据量,有利于上位机对数据的后续分析处理。通过仿真工具对系统进行验证,并在光纤温度信号采集处理系统中做了综合测试。实验结果表明,该算法可在100 MHz的全局时钟下高速采集并处理数据,且能有效提高随机噪声背景下的重复信号信噪比,满足工业超声电磁检测、分布式光纤测温等应用领域的数据采集需求。