管式PECVD工艺对组件PID的影响研究

2021-09-03王贵梅王玉肖许志卫

李 景,王贵梅,王玉肖,刘 苗,许志卫

(晶澳太阳能有限公司,河北邢台 055550)

近几年来业内对晶硅光伏组件系统出现电势诱导衰降(potential induced degradation,PID)现象的机理进行了较多研究,P 型电池的PID 衰减,已经被证实是由于玻璃中Na 离子的迁移产生一个并联的分路,导致并联电阻降低[1]。PID 的影响因素涉及封装材料性能及电池制造技术等方面,较为宽泛,本文重点研究了多晶硅电池管式等离子增强化学气相沉积(plasma enhanced chemical vapor deposition,PECVD)工艺对组件抗PID 性能的影响。

1 实验

采用北方华创管式PECVD 对P 型156 MH 多晶硅片进行镀膜。采用北京量拓科技有限公司EMPro-PV 椭偏仪测试膜厚折射率。采用美国Sinton 的WCT120 测试镀膜后电池片少子寿命。采用上海汉测的HHW1800F 双“85”测试箱测试60版型组件PID。

1.1 实验背景

常规P 型多晶硅电池正常生产工艺流程为:链式酸制绒→管式磷扩散制备PN 结→链式湿法刻蚀去除背面及边缘PN结→臭氧氧化→正面PECVD 钝化减反射→印刷正背面金属电极→烧结形成欧姆接触→IV 测试分选。

如图1 所示,在管式PECVD 工艺步骤中,在镀膜步前通常带有预淀积步,此步骤开启功率和NH3,利用NH3电离出的等离子体轰击电池片表面,起到去除杂质的作用,本文重点研究保留和去除预淀积步骤、镀膜步骤对PID 性能的影响,镀膜步骤重点观察单层膜、双层膜以及底层膜(贴近硅片子层氮化硅膜)的膜厚和折射率对PID 性能的影响。

图1 管式PECVD工艺步骤

1.2 实验方案

实验原料硅片采用晶澳太阳能有限公司自产的P 型多晶硅片,硅片尺寸为156 mm×156 mm,厚度为180 μm,电阻率为1~3 Ω·cm。实验样片为同一铸锭硅切割硅片。原料硅片经过以下工艺流程:链式酸制绒→管式磷扩散制备PN 结→链式湿法刻蚀去除背面及边缘PN 结→臭氧氧化。在管式PECVD 不同工艺条件下镀膜,做成电池后,封装成组件,实验分为7 个条件,每个条件做10 块72 版型组件(12 片电池成一串,6 串电池串联成72 版型组件),叠膜膜厚目标值为80 nm,折射率目标值为2.10%。氮化硅结构示意图如图2 所示。

图2 膜层结构示意图

不同样品工艺处理方式如表1 所示。

表1 不同样品不同管式PECVD 工艺条件

将实验组件放置在温度85 ℃、湿度85%的测试箱内,同时给组件加-1 500 V 的电压,模拟电站运行过程中的负偏压情况,设定测试时间96 h,测试时间结束后自动停止加负偏压,即停止PID 测试。对比PID 测试前后组件的电性能变化,从而分析出组件PID 的衰减情况[2]。PID 测试前后功率损失(power loss,PL)=1-测试后功率/测试前功率。

2 结果与讨论

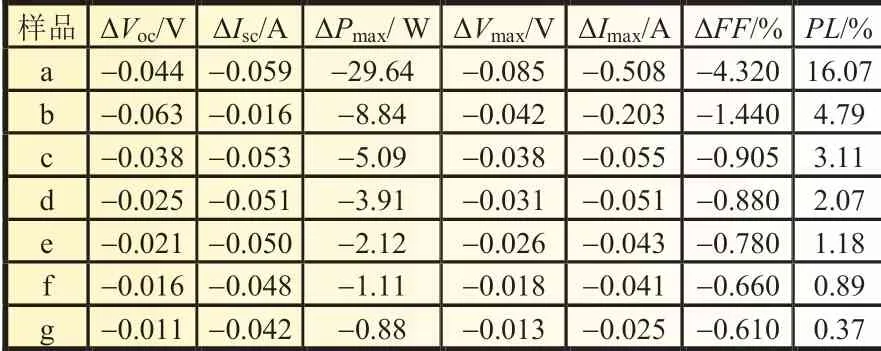

实验样品PID 测试结果如表2 所示,其中各项电性能参数以及PL值均为每组样品对应的10 块组件测试平均值。

表2 组件PID 测试前后光电转换参数变化

2.1 预淀积步骤影响

样品a 和样品b 都采用单层膜,样片b 取消预淀积步骤,数据表明,取消预淀积步骤,抗PID 性能提升。由于臭氧常温氧化,厚度较薄,椭偏仪无法测量膜厚,我们用硅片少子寿命间接表征钝化效果(每组样品分别抽取5 片测试其少子寿命值)。根据有无预淀积步测试少子寿命的结果如表3 所示,取消预淀积步骤少子寿命相对高35%。我们分析取消预淀积步骤,抗PID 性能提升的原因是由于减少了预淀积过程中等离子体对硅片表面的轰击,减少臭氧氧化层结构遭到破坏,更好地保证了氧化层对硅片表面的钝化效果。

表3 不同样品的少子寿命值

2.2 单层膜/双层膜影响

同样是去除预淀积步骤,样品b 为单层氮化硅膜,样品c为双层氮化硅膜,底层膜膜厚20 nm,折射率2.20%,上层膜膜厚64 nm,折射率2.05%。测试结果如表2 所示,样品c 比样品b 的抗PID 性能好,即双层氮化硅比单层氮化硅的抗PID 性能好。这是由于双层膜中接触硅片的底层膜折射率高,氮化硅为富硅薄膜,有利于饱和与硅接触界面的悬挂键,而且有利于在退火条件下放出氢原子进入硅片内部,表面固定电荷有所下降,场钝化效应下降,但是界面态密度也下降,化学钝化效应上升,最终呈现的钝化结果上升,减少缺陷中心对Na+的捕获,降低表面复合[3-6]。

2.3 底层膜膜厚/折射率影响

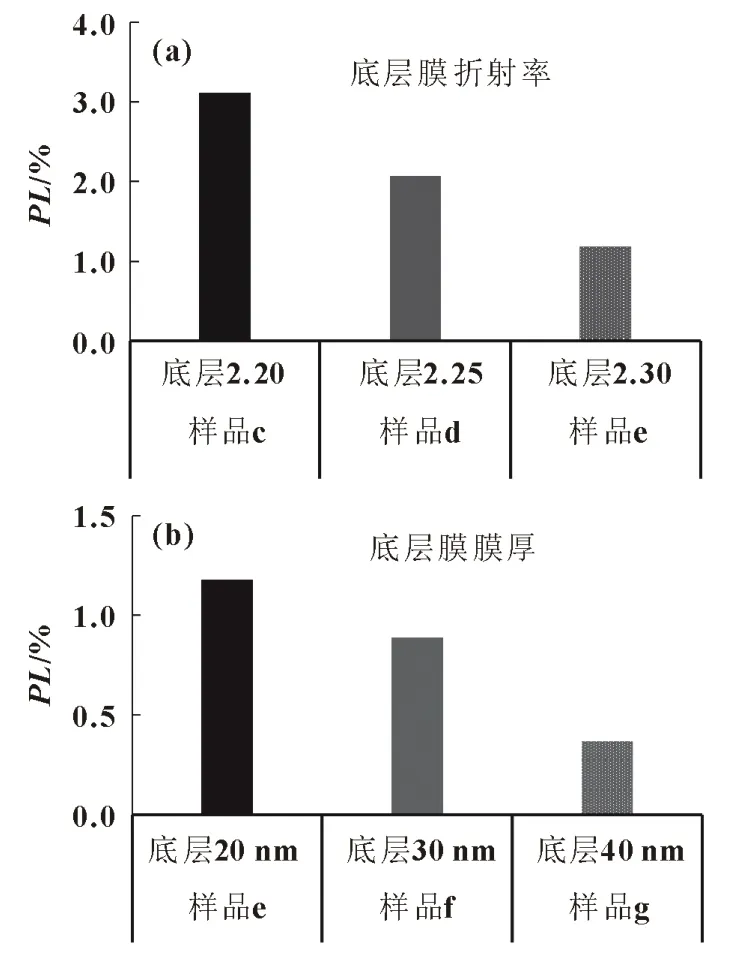

去除预淀积步骤,都是双层膜工艺,样品c、d、e 底层膜膜厚20 nm,折射率2.2-2.25-2.3 依次升高,图3(a)数据表明,底层膜膜厚一定,折射率越高,抗PID 性能越好。

去除预淀积步骤,都是双层膜工艺,样品e、f、g 底层膜折射率2.3,膜厚20 nm-30 nm-40 nm 依次递增,图3(b)数据表明,底层膜折射率一定,膜厚越高,抗PID 性能越好。

图3 不同底层膜的PL数据

有研究认为氮化硅减反射膜是发生极化效应的根源,一方面电荷离子聚集在氮化硅表面,诱导一个电场抑制钝化效果,增加表面复合速率;另一方面,Na+扩散到硅体内,发射极Na+浓度增加,从而使PN 结减弱[7]。当氮化硅减反射膜贴近硅片子层厚度变厚或者折射率升高时,氮化硅薄膜钝化性能提高,光电导效应增强,减少电池漏电通道,降低电池表面电荷富集能力,导致正电荷在电池表面诱导电场难度增加,从而减弱PID 效应[8]。

3 结论

管式PECVD 工艺步骤和参数对多晶硅光伏组件PID 存在较大影响,降低多晶硅光伏组件PID 风险的方法如下:

(1)去除预淀积步可以改善抗PID 性能。

(2)双层膜比单层膜抗PID 性能好。

(3)底层膜厚一定,提高底层折射率可以改善抗PID 性能。

(4)底层折射率一定,提高底层膜厚可以改善抗PID 性能。

(5)去除预淀积步对电池片光电转换效率影响不大,为了保证电池片光电转换效率,底层膜膜厚和折射率不能无限增加,实际生产过程中综合考虑电池转换效率和抗PID 性能,需要选取适当的底层膜工艺参数。