寄生参数对并联SiC MOSFET电流不均衡的影响

2021-08-25张永刚宁平凡王迪迪肖宁如李玉强

张永刚,宁平凡,刘 婕,王迪迪,肖宁如,李玉强

(1.天津工业大学 电气工程与自动化学院,天津 300387;2.天津工业大学 电子与信息工程学院,天津 300387;3.天津工业大学 大功率半导体照明应用系统教育部工程研究中心,天津 300387)

0 引言

随着电动汽车、新能源行业等新兴工业领域的发展,电力电子设备的应用领域也越来越广泛。作为功率开关器件的MOSFET和IGBT更引起研究人员的注意。传统的硅基器件在耐压、工作频率等方面都已经达到其物理极限,远不能满足日益提升的要求[1],而作为宽禁带半导体代表的SiC、GaAs在高温、高压、高频环境下具有较高的热导率和较低损耗等优良的物理特性[2,3]。因此,SiC MOSFET在新能源汽车,大功率变流设备中逐步替代传统半导体器件[4]。SiC MOSFET制造,封装工艺相较于传统MOSFET并不成熟,晶圆尺寸和生长速度也远小于硅。在相同电压等级下,电流耐受程度越高,其制造、使用、后期维护的成本也越高。即使是相同型号的芯片,参数也会有一定的差异性,更大的电流和更高的开关速度下使得寄生参数在开关过程中对并联电流不均衡的影响更明显。如今,对于SiC MOSFET的研究主要集中于器件封装[5],器件模型的建立[6]以及大规模应用等重要领域[7],而寄生参数对并联电流不均衡影响的研究相对较少。关于寄生参数研究的方法主要有:(1) 通过实验测量寄生参数的影响[8],(2) 通过数学公式建立模型,进行相关的理论分析[9],(3) 通过软件进行仿真,研究寄生参数对于开关和导通过程的影响[10]。并联SiC MOSFET的电流不平衡主要分为动态和静态两个方面。动态电流不均衡是指在开关过程中,漏极电流由于寄生参数,驱动回路等因素所导致的差异。静态电流不均衡是指并联SiC MOSFET在完全导通的情况下,由于导通电阻和驱动电压等因素导致的漏极电流不均衡现象。在相同电压等级下采用更高电流等级的碳化硅模块将不存在电流不均衡的问题[11],同时还能有效降低开关损耗,随着电流等级的提高,碳化硅芯片的制造技术不成熟,产能不足等原因导致的价格偏高,备货不充足等相关问题更严重,难以满足工业生产的需要。对并联芯片进行有效的均流措施可以有效缓解上述问题。因此对并联SiC MOSFET电流不均衡影响因素的研究就非常重要,为SiC MOSFET更广泛的使用提供理论支持。

本文分析影响并联SiC MOSFET电流不均衡的因素,通过仿真实验的方法验证理论分析的正确性。同时还给出了一种基于阻抗平衡联合磁芯电感的方法用以抑制并联电流不均衡,以提高并联SiC MOSFET系统的使工作效率。

1 寄生参数对并联SiC MOSFET电流不均衡的影响

本文选用CREE公司的C2M008120D型SiC MOSFET为研究对象,采用其官方网站所提供的spice模型,搭建相关仿真电路并进行了仿真实验。

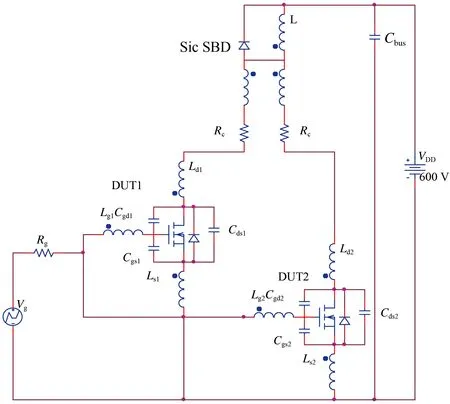

图1是考虑寄生参数的并联SiC MOSFET的仿真测试原理图。图中Vg是栅极驱动信号源,Rg是栅极驱动电阻,包括SiC MOSFET内部栅极驱动和外部驱动等两部分,DUT1,2是两个并联使用的SiC MOSFET被测芯片模型。Lg1、2分别是两个被测芯片的栅极寄生电感,Ld1、2是漏极寄生电感,Ls1、2是源极寄生电感。Cgd1、2是栅漏极寄生电容,Cgs1、2是栅源极寄生电容,Cds1、2漏源极寄生电容。Cbus是母线电容,VDD作为直流负载电压,设置为600 V。由数据手册及spice模型的库文件得C2M008120D部分参数如表1所示。

图1 考虑寄生参数的并联SiC MOSFET

表1 基于数据手册的C2M008120D静态参数

1.1 栅极寄生电感Lg对并联SiC MOSFET电流不均衡的影响

驱动回路中的栅极寄生电感Lg,来源于驱动引线长度和封装过程中引脚长度。栅极寄生电感Lg对输入电容Ciss的充放电速度和开关振荡势必有一定的影响。在仿真实验的过程中仅考虑栅极寄生电感Lg的差异,保持栅极寄生电感Lg1为1 nH不变,另一支路上栅极寄生电感Lg2分次设置为10、20、30 nH,用以模拟不同栅极寄生电感下,对并联漏极电流id的影响程度,其仿真结果如图2所示。

图2 栅极寄生电感对并联电流不均衡的影响

在并联使用的开通过程中,并联支路上的漏极电流分别为

id1=gm(Ug-Lg1ig-Vth),

(1)

id2=gm(Ug-Lg2ig-Vth),

(2)

gm表示器件的跨导,ig1,2表示栅极驱动电流。在该过程中的电流不均衡度为

(3)

由公式(3)以及仿真结果可知,栅极电感小的器件比栅极电感大的器件更早开通,而栅极电感大的,需要分担的电流也更多。栅极寄生电感Lg只有在差异较大的情况下才会对并联SiC MOSFET开关过程中的电流产生影响,当两并联SiC MOSFET完全导通后,栅极寄生电感Lg对静态电流均衡并无明显的影响。

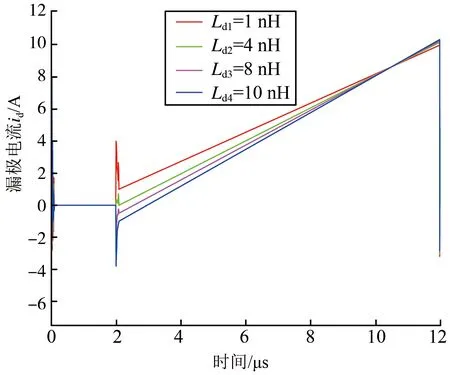

1.2 漏极寄生电感Ld对并联SiC MOSFET电流不均衡的影响

漏极寄生电感源于器件封装过程和布线结构,漏极寄生电感Ld与寄生二极管在导通后形成振荡回路,引起电流振荡,在关断过程中,漏源极电容Cgs开始充电过程,关断后与之形成振荡回路。在仿真实验的过程中仅考虑漏极寄生电感的差异,保持栅极寄生电感Ld1为6 nH保持不变,另一支路上漏极寄生电感分次设置为4、8、10 nH,用以模拟不同栅极寄生电感下,对并联漏极电流id的影响程度,开关过程的仿真结果如图3所示,完全导通的仿真结果如图4所示。

图3 漏极寄生电感对并联电流不均衡的影响

图4 漏极电感对静态电流不均衡的影响

由仿真结果可知,漏极寄生电感Ld对开关过程及导通后的电流不均衡均有较大的影响。漏极电感较大的支路,电流过冲较大,更容易引起电流振荡现象的发生,这也是导致器件损坏的重要原因之一。图4中,12 μs时并联器件由完全导通进入关断状态,电流急剧下降。在完全导通后,由戴维南定理(Thevenin's theorem)得

(4)

式(4)中的di/dt是电流变化率,Rdson是导通电阻。id是漏极电流,Udc是母线电压,当导通电阻恒定时,此时的电流差异可以表示为

(5)

漏极寄生电感的差异直接决定了漏极电流在静态过程中的差异。在开关过程中,漏极寄生电感Ld和寄生的体二极管形成谐振回路,引起电流振荡,振荡频率为

(6)

关断过程中,漏极寄生电容Ld完成对漏源极电容Cds充电,并与之形成谐振回路,振荡频率为

(7)

漏极寄生电感Ld主要影响器件在开关过程中电流上升(下降)后的波形,当Ld较大的振荡频率小、阻尼系数小,因此,在开关过程中,较大Ld支路的电流过冲大同时振荡幅度也较大。

1.3 源极寄生电感Ls对并联SiC MOSFET电流不均衡的影响

源极寄生电感Ls也是影响并联SiC MOSFET电流不均衡的重要因素。在仿真实验的过程中仅考虑源极寄生电感Ls的差异,保持源极寄生电感Ls1为1 nH不变,另一支路上漏极寄生电感Ls2分次设置为5、10、15 nH,用以模拟不同源极寄生电感下,对并联漏极电流id的影响程度,其仿真结果如图5所示。

图5 源极寄生电感对并联电流不均衡的影响

源极寄生电感对栅源极电压具有负反馈作用,同时对静态电流几乎为无影响由于在到通知后,电流变化率几乎为零,因此就不会影响电流的变化,如公式(8)所示

(8)

在导通过程中,当源极寄生电感较大时, SiC MOSFET开通较慢,同时承担的电流较小,当并联器件的Ls差异增大时,Ls较小的支路上电流过冲增大。关断过程与之类似。

1.4 栅源极寄生电容Cgs对并联SiC MOSFET电流不均衡的影响

作为电压控制型号器件,Si C MOSFET的开通关断实际上就是对栅极电容充放电的过程,由数据手册可知,器件的在输入电容Ciss由栅源极电容Cgs和栅漏极电容Cgd组成。在仿真实验的过程中仅考虑漏极寄生电感的差异,保持栅源极寄生电容Cgs1为900 pF不变,另一支路上栅源极寄生电容Cgs2分次设置为930、960、1000 pF,用以模拟不同栅极寄生电感下,对并联漏极电流id的影响程度,其仿真结果如图6所示。

图6 栅源极寄生电容对并联电流不均衡的影响

从图6可以看出,并联SiC MOSFET的漏极电流对于栅源极寄生电容非常敏感较小的支路上开关速度较快且漏极电流的波动也很小。在两器件完全导通后,漏极寄生电感Ld对静态电流均衡并无明显的影响。Cgs主要影响栅极电压的上升/下降快慢,在同样的条件下Cgs较小的器件栅压更早满足阈值,这就直接影响到器件的开关速度。减小栅源极电容与栅极驱动电阻可形成RC 缓冲电路,可以降低器件的充放电速度,降低器件的开关速度,抑制振荡现象的发生。栅源极寄生电容越大,回路的时间常数越大,充放电时间越长,器件的开关速度越慢。同样,开关速度慢会增加器件损耗,降低器件可工作的开关频率。

SiC MOSFET 的开关过程对Cgs十分敏感,首先表现在栅极电压的上升/下降速度慢,从而导致了开关过程中电流的不平衡。由于Cgs2较大,该支路开关速度较慢,Cgs2支路的数值越大,器件开通较慢,它的电流较小。在关断过程中,Cgs2数值越大的支路器件关断更慢,则承受更大的电流。由数据手册可知,SiC MOSFET的Cgd,Cds数值较小,不匹配程度也相对小。因此对并联使用的SiC MOSFET开关过程中电流不均衡影响也较小,因此文中并未针对上述两参数对并联电流不均衡的抑制进行分析。

2 并联SiC MOSFET电流不均衡的抑制

并联SiC MOEFT电流均流方法可分为降额法[12],阻抗平衡法[13,14]栅极电阻补偿法[15,16]和有源栅极控制法[17,18]。本文给出了一种基于阻抗平衡联合磁芯电感的方法用以抑制并联SiC MSOFET电路不均衡的现象的发生。

如图7所示,是一种基于阻抗平衡和磁芯电感的并联SiC MOSFET电流不平衡抑制的电路原理图。其中Rc是串联接入并联支路的均流电阻,Lm表示磁芯电感。在并联SiC MOSFET的回路中,

图7 电路原理图

U1=id1(Rc+Rdson1),

(9)

U2=id2(Rc+Rdson2)。

(10)

此时,漏极不均衡电流之比

(11)

将均流电阻Rc设置为1 Ω,远大于数据手册中80 mΩ的导通电阻。在导通状态下,电流处于平衡状态且不会造成过大的损耗。并联SiC MOSFET支路中的电流流入匝数、结构完全相同的缠绕在磁芯上的线圈。当并联回路的寄生参数,功率回路一致时,漏极流过的电流不会有任何差异。两电流在磁芯中产生的磁通量的矢量和为零,对流过的电流不会产生作用。相反的,当电流不均衡,磁芯电感就会产生相反的磁通相互抵消后的剩余磁通会在磁芯中产生感应电动势,并作用到电流上升较快的支路上进而使电流趋于平衡状态。由安培环路定理可知

(12)

式中的H表示磁场强度,R表示磁芯电感的有效半径,n表示线圈的匝数,i表示流过线圈的电流大小。两个线圈匝数相同,线圈回路中的励磁电感Lm对两并联支路中电流的不平衡可以起到抑制作用,其感应电动势Uf为

(13)

磁感应强度

ΔB=μrμ0(H1-H2),

(14)

(15)

式中的B表示磁感应强度,μr表示磁芯的相对磁导率,μ0为空气磁导率,S为磁芯的横截面积,Rmax,Rmin分别表示磁环内外径的大小。由公式(14)(15)可以得出

(16)

感应电动势Uf

(17)

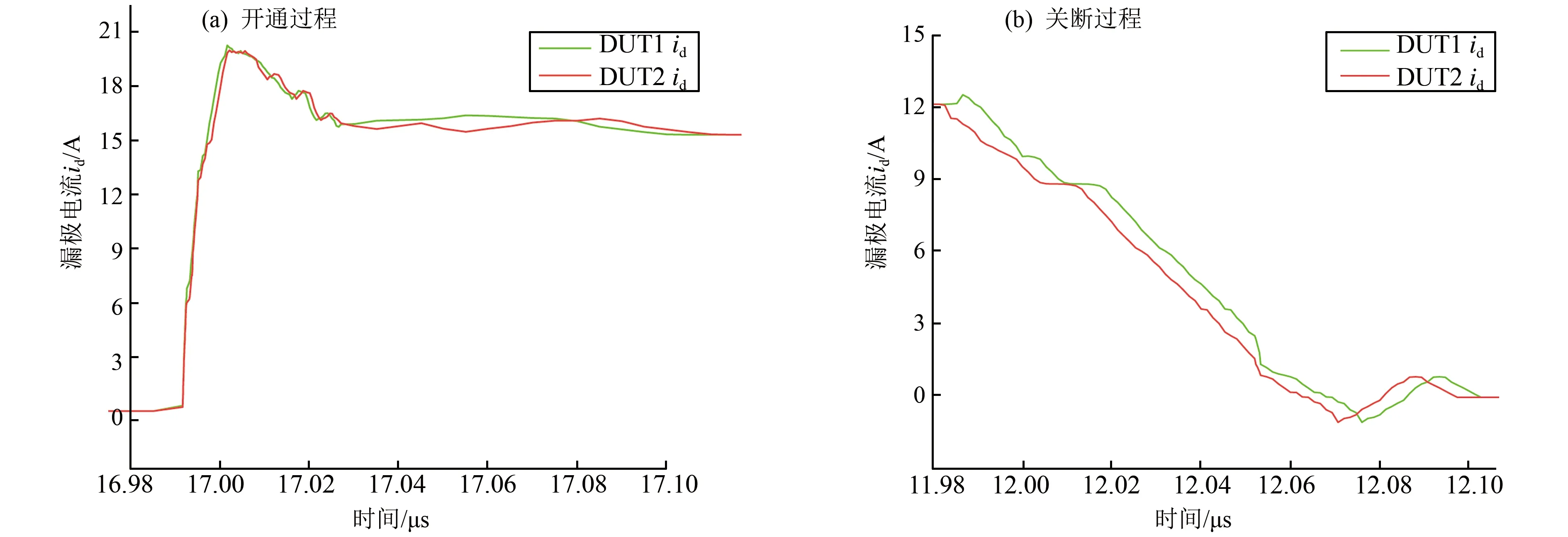

磁芯电感抑制电流不平衡的本质在于作用在不平衡电流上的电感是线圈中的励磁电感大于作用在两支路电流上的电感。该均流方案适用于所有可能导致电流不均衡因素的抑制,下文将以栅极寄生电容不匹配导致的电流不均衡为例,进行仿真实验的验证。验证结果如图8所示。

图8 采取均流措施后开关过程中的漏极电流

如图8所示,针对栅极寄生电容Cgs的不匹配所产生的电流不均衡在采用一种基于阻抗平衡和磁芯电感的均流方法后,从图中可以看出相比于原来电流在开关过程中电流不均衡有较大程度的改善。

3 结语

本文针对可能导致并联SiC MOSFET电流不均衡的因素,基于CREE官网提供的spice模型进行了相关的仿真及理论分析。还给出了一种基于阻抗平衡联合磁芯电感的均流方法,该方法能有效抑制各种因素导致的动静态电流不均衡现象的发生。

(1) 并联使用的SiC MOSFET可以有效提高系统的功率密度。寄生参数不匹配会导致的并联电流不均衡,严重威胁回路的安全工作。源极寄生电感Ls和栅源极寄生电容Cgs对开关过程中电流不均衡有较大的影响而对导通之后的电流不均衡则影响较小可以忽略。漏极寄生电感Ld则主要影响静态电流不均衡而栅极寄生电感Lg只有在数值差异较大的情况下才会对动态电流不均衡产生影响。因此,在并联使用SiC MOSFET的过程中,芯片的寄生参数不匹配会严重影响到并联电流不均衡程度,进而威胁回路安全工作。

(2) 在并联SiC MOSFET工程中,不平衡电流流过均流电阻和磁芯电感,磁芯电感会产生较大的励磁电感,抑制并联过程中的不平衡电流,从而有效改善电流不均衡现象的发生。串联接入的均流电阻和磁芯电感对动静态电流不均衡有良好的抑制效果,能有效保护电路提高工作效率。