多晶硅栅极刻蚀过程中边缘刻蚀缺陷的研究及改善

2017-10-20任昱聂钰节唐在峰

任昱++聂钰节++唐在峰

DOI:10.16661/j.cnki.1672-3791.2017.25.087

摘 要:刻蚀缺陷是半导体制程中最关键和最基本的问题,理想的等离子体刻蚀工艺过程中,刻蚀气体必须完全参与反应而形成气态生成物,最后由真空泵抽离反应室。但实际上,多晶硅栅极等离子体刻蚀过程中,生成的反应聚合物(polymer)无法由真空泵抽离反应室而附着在刻蚀腔壁上,造成反应室的污染,有些甚至附着在晶圆表面而形成元器件的微粒子污染,造成产品良率下降甚至报废。本文通过改变调整刻蚀工艺参数等方式,成功解决了多晶硅栅极刻蚀工艺制程中反应生成物转变为微粒子污染物这一问题,使得产品良率提升了3%,刻蚀反应腔体保养时数延长了一倍,晶圆报废率降低了0.03%。

关键词:多晶硅刻蚀 干法刻蚀 等离子体 栅极 刻蚀缺陷

中图分类号:TN305.7 文献标识码:A 文章编号:1672-3791(2017)09(a)-0087-05

随着微电子技术的发展,使器件的特征尺寸(Critical Dimension,简称CD)不断缩小,使得集成度不断提高,功耗降低,器件性能提高。在微电子学中,特征尺寸通常指集成电路中半导体器件的最小尺寸,如MOSE管的栅极关键尺寸,特征尺寸是衡量集成电路设计和制造工艺水平的重要参数。但是特征尺寸越小,栅极的尺寸容差要求就变得越来越严格,尤其是大尺寸的12寸晶圆硅片的应用,使得工艺控制变得更加苛刻。例如按照刻蚀容差绝对值应控制在10%之内,对于45nm工艺节点,容差绝对值要小于5nm[1]。

在先进的多晶硅栅极工艺中,刻蚀腔之间CD偏差值匹配度已经小于1nm,而高的CD精度意味着工艺步骤的可重复性需要做到完美。与此同时,由于堆叠结构越来越复杂,刻蚀过程中反应物和生成物也相应地增加,另外刻蚀反应腔体也要承担更多的工艺刻蚀内容,于是刻蚀反应腔体的匹配和工艺的可重复性,已经成为等离子体刻蚀中很大的挑战。刻蚀的一致稳定性控制要求不仅是针对同一块硅晶片上的不同区域而言,更是针对刻蚀反应腔两次维护保养间数百小时的射频工艺过程而言。

由于反应生成物影响着刻蚀腔体内壁,而刻蚀腔体内壁环境又与等离子体的成分相互作用,刻蚀过程中每一个工艺和硬件参数都影响着刻蚀的稳定性,为了实现非等向刻蚀,需要钝化层保护侧壁,而形成侧壁钝化层的聚合物,又可能成为腔室或晶圆表面的污染物[2,3]。本文就300mm硅栅极等离子体刻蚀过程中,刻蚀反应物转变为微粒子污染物这一问题,从反应腔结构分析和工艺参数改变等方面入手,通过不断尝试和调整,既消除微粒子污染又能实现持续稳定,最终确保反应腔中出来的每一片晶圆都拥有相同的性能且具有精确的可重复生产性,实现产品良率的提升。

1 多晶硅栅刻蚀过程中的刻蚀缺陷分析

在多晶硅栅极刻蚀工艺制程中,由于容差要求非常严格,为达到关键尺寸要求、理想的图形、好的刻蚀均匀性以及高的选择比,在刻蚀完硬掩膜层后,如BARC,HM(SiN/SiO2)等,才进行多晶硅栅极的刻蚀,根据缺陷(defect)扫描图像显示,所产生的defect属于典型的部分阻挡刻蚀,已经出现了清晰的栅极线条,如图1所示,经过反复比较研究发现这种典型的刻蚀缺陷是在Hard Mask(硬质掩模层,简称HM)刻蚀过程中微粒掉落产生的。

就整个defect分布情况分析发现,defect都集中在晶圆边缘位置,如图2所示,对比缺陷在刻蚀腔体位置发现都是出现在ESC(静电吸盘,简称ESC)单悬臂区域位置处,如图3所示。但defect的数量具有随机性,某一片wafer比较少,另外的wafer比较高,跟踪晶圆良率发现defect分布区域正对应良率的损失,如图4所示,这种多晶硅阻挡刻蚀缺陷明显降低了产品的良率,甚至会因为defect数量的过多引起wafer报废。

通过长期数据采集和对比,发现在刻蚀腔体维护保养后初期,没有出现单托臂区域wafer边缘的defect,而随着刻蚀腔体作业RF时间的增加到一定程度,单托臂区域wafer边缘的defect开始出现。因此设备的维护保养周期,被限制在100h内,只达到正常设备维护保养RF时数200h的一半,这种多次进行设备维护保养或全部配件更换,维护费用也急剧上升但也无法解决此issue,因此找到defect产生的真正原因,施以有效的解决方法变得极为迫切。

2 多晶硅栅刻蚀过程中的刻蚀缺陷来源的分析

2.1 特征图形分析

从多晶硅栅极刻蚀缺陷分布分析发现,每片wafer刻蚀缺陷都是集中在刻蚀反应腔的特定位置,正好对应着ESC单托臂区域位置,根据等离子体在刻蚀腔体的分布及真空泵抽气情况分析发现,在ESC单托臂处由于底部托臂的阻挡会产生较为强烈的气体回流现象,如图5所示,产生的polymer的等离子体浆也会在ESC单托臂上方处产生回流,从而在此处沉积更多的polymer。同时测试晶圓控片刻蚀速率也发现,在ESC单托臂对应区域的刻蚀速率明显较其他区域的刻蚀速率慢,如图6所示中心区域。

2.2 多晶硅刻蚀工艺分析

多晶硅刻蚀工艺包括了复杂的多步骤刻蚀,依次主要是BARC(底部抗反射涂层刻蚀),HM(无机硬质掩模层刻蚀)、BT(氧化硅刻蚀)和ME(多晶硅刻蚀)刻蚀,每一步刻蚀过程都会产生大量的刻蚀副产物[4,5],具体如表1种所示。这些副产物气体在被分子泵抽离的过程中在ESC单托臂处由于ESC托臂的阻挡,部分会回流重新淀积在托臂上方的top edge ring表面,随着RF时数增加top edge ring表面淀积的polymer也就越来越多,从而产生刻蚀缺陷的微粒子来源。

在微电子学中,多晶硅栅极大小直接影响了COMS器件的电学性能,而栅极侧壁形貌又直接关系到栅极性能的优劣,因此多晶硅栅极需要一个“陡直”的侧壁形貌。这种“陡直”的侧壁形貌主要就是由HM刻蚀传递到多晶硅栅极上的,因此HM侧壁形貌也就决定了最终多晶硅侧壁形貌。在等离子体刻蚀中,为取得“陡直”的侧壁形貌不仅需要刻蚀过程中不断地有侧壁保护层进行保护,更需要赋予高偏压来增加异向刻蚀能力。一般方法都是在HM刻蚀步骤中采用高的偏压来获得强的纵向物理轰击强,偏压越大对应的物理轰击能力越强,表现的刻蚀速率也越强,如7所示,偏压越大,刻蚀速率越大,两者呈现正向线性关系。endprint

这种强烈的物理轰击会作用在ESC边缘top edge ring上,使得沉积在top edge ring表面的polymer被溅射成微粒散落到附近的边缘晶圆表面,从而阻止后续刻蚀进行,如图8所示。

2.3 刻蚀反应腔结构分析

在刻蚀反应腔内与晶圆直接接触的是ESC,具有静电吸附作用。ESC也是wafer接受等离子体(plasma)的场所,具有很强的耐腐蚀性,能承受持续的离子轰击和具有良好的介电性质,是反应腔室的主要部件之一。在ESC的外面加装一个用于增大下电极表面积的Ring,称为top edge ring,主要是保护wafer的edge和center部位有接近相当量的离子轰击。因为在刻蚀系统中,plasma是在高真空中进行,上下极板之间有空隙,如果下电极和晶圆一样大小,那么plasma在真空系统作用下,靠近外缘的plasma就会泄露,导致wafer edge部位能量减少。因此需要把下部做大点,由于电极不能比wafer大,于是就在電极的外面再安装一个圆环,一般采用硅、石英等材质制作,是一种耗损件,如图9所示,等离子体刻蚀过程中会同样刻蚀在top edge ring上。

通过多次设备维护保养时的观察,发现在托臂上方top edge ring上的polymer淀积得比较多,而polymer淀积厚的区域正对应着defect密集区域,而多晶硅栅极刻蚀制程是polymer产生很多的工艺制程,分析可能是托臂处抽速过低,阻挡了polymer被真空泵顺利抽走而堆积在top edge ring上方,在多晶硅刻蚀过程中经过高偏压的轰击而溅射在wafer边缘的栅极线条之间,影响后续刻蚀造成部分刻蚀缺陷。

3 多晶硅刻蚀缺陷解决实验

3.1 惰性气体流量对刻蚀缺陷影响

鉴于边缘部分阻挡刻蚀缺陷的来源是由刻蚀过程中polymer过多导致的。尝试在各个主要刻蚀步骤后添加惰性气体来稀释刻蚀过程中产生的刻蚀副产物气体,弱化polymer的产生,如图10所示为添加惰性气体后惰性气体会在ESC单托臂上方稀释刻蚀副产物气体,从而减少多晶硅刻蚀的刻蚀污染颗粒源。

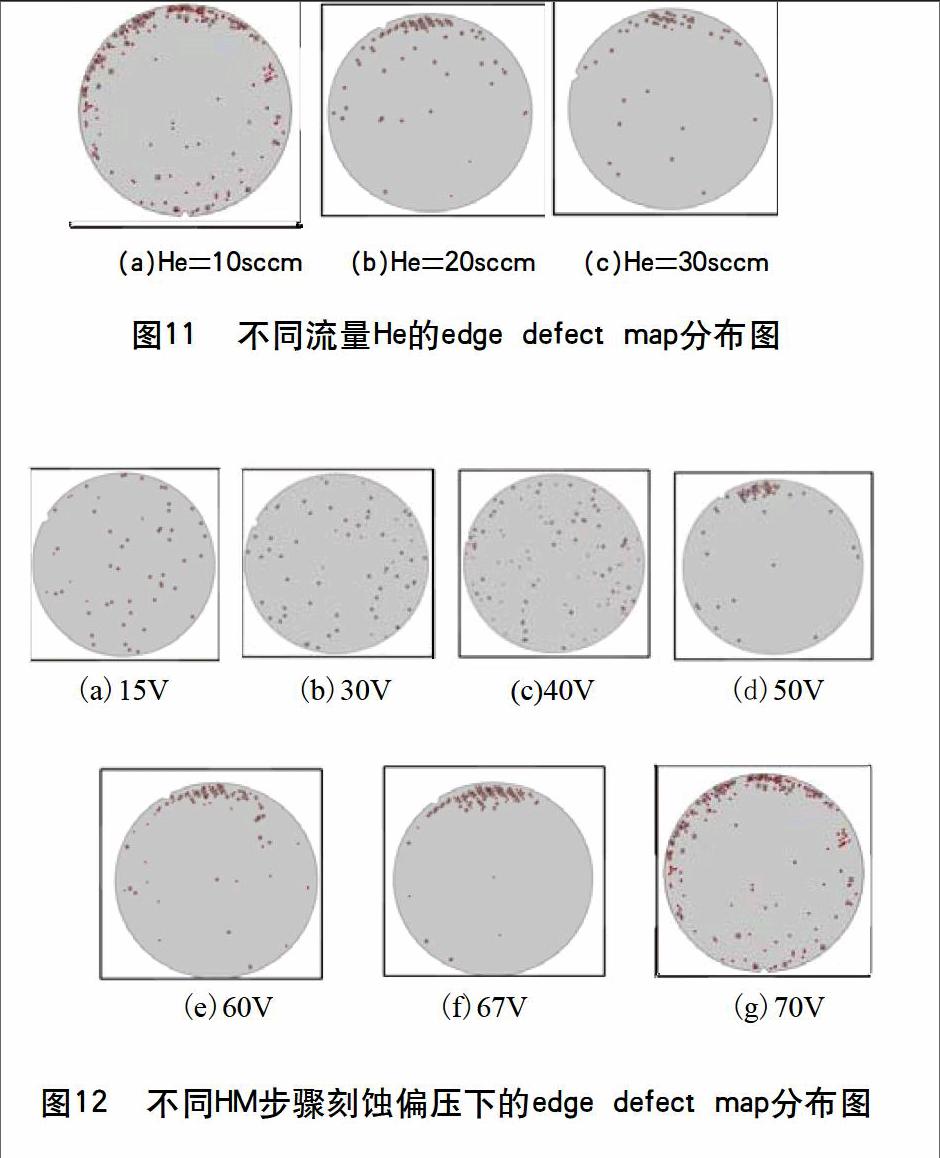

本案例中使用He作为惰性气体进行实验分析,使用10sccm、20sccm和30sccm3个分批实验分析,具体结果如图11所示。从图11可以发现,随着在多晶硅主要刻蚀步骤后增加惰性气体流量可以一定程度地改善ESC单托臂区域处的刻蚀缺陷,这是由于惰性气体的加入可以有效地稀释多晶硅主要刻蚀步骤产生的刻蚀副产物气体,减少在单托臂区域上方top edge ring表面polymer的沉积,从而降低HM刻蚀过程中polymer被离子轰击而溅射到晶圆表面的机率,但是仅靠在主要刻蚀步骤后增加稀释气体流量不能完全解决ESC单托臂区域处的刻蚀缺陷问题,这是由于在主要步骤刻蚀过程中已经有部分刻蚀副产物气体聚集成polymer沉积在单托臂区域的top edge ring表面,在主要刻蚀步骤之后加入惰性气体只能稀释剩余的副产物气体,这样虽然有减轻polymer的沉积,但是难以起到根除的作用[6-9]。

3.2 硬质掩模层(Hard Mask)刻蚀偏压对刻蚀缺陷的影响

鉴于边缘部分阻挡刻蚀缺陷的产生是由于在HM刻蚀步骤中,过强的物理轰击造成polymer溅射产生的。尝试在HM刻蚀步骤减弱物理轰击作用。物理轰击是由于等离子体的大质量离子在电场作用下加速产生动能向晶圆表面移动,在晶圆表面正离子轰击晶圆表面材料,产生刻蚀效果[10]。

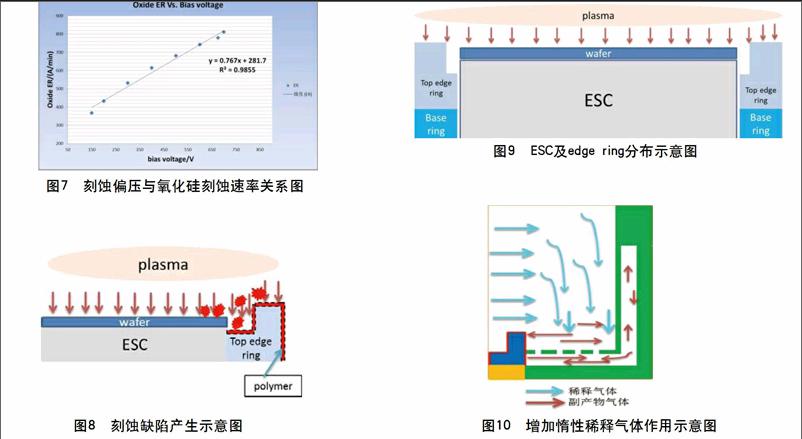

本案例中使用的偏压时67V,实验使15V、30V、40V、50V、60V、70V做实验分析,具体实验结果如图12所示。

从图12中可以看到,随着HM刻蚀偏压的增大,ESC单托臂区域处的刻蚀缺陷变得越来越严重,在HM刻蚀偏压小于40V时,ESC单托臂处没有发现多晶硅的刻蚀缺陷;在HM刻蚀偏压大于40V时,ESC单托臂处开始出现刻蚀缺陷并且随着偏压的增大刻蚀缺陷变得更加严重,这主要是由于HM刻蚀偏压小于40V时,物理轰击作用较弱不足以将top edge ring表面的polymer轰击而溅射到附近晶圆表面;当HM刻蚀偏压大于40V时,强烈的物理轰击作用可以使得top edge ring表面的polymer被轰击成微粒子而溅射到附近晶圆表面,从而产生后续的多晶硅刻蚀缺陷。

根据实验研究结果综合刻蚀速率和刻蚀侧壁形貌调整,选择HM偏压为35V作为刻蚀HM步骤的偏压,相应地通过HM trim步骤调节横向刻蚀时间来控制多晶硅栅极线宽大小。通过在工程片上进行多晶硅栅极工艺刻蚀,与基础条件多晶硅栅极刻蚀后形貌相比发现,新条件刻蚀多晶硅栅极同样可以得到“笔直”的侧壁形貌和目标线宽尺寸,整体CD大小和角度与基准条件相匹配,如图13所示。

4 结语

本文通过分析工艺参数和设备结构以及defect特点,来探讨defect产生的原因,再确定刻蚀缺陷是由HM刻蚀步骤中离子轰击聚合物溅射到晶圆表面产生的,通过调整HM刻蚀步骤偏压降低离子轰击强度,成功地消除了刻蚀制程中反应生成物转变为微粒子污染这一问题。既解决了ESC单悬臂位置处刻蚀缺陷这一问题,同时有效地将设备维护保养时间也从100h提高到200h。

参考文献

[1] 张庆钊,谢常青,刘明,等.硅栅干法刻蚀工艺腔室表面附着物研究[J].微细加工技术,2007(2):50-52.

[2] 田业冰,硅片超精密磨削表面质量和材料去除率的研究[D].大连:大连理工大学,2005.

[3] 陈乐乐,朱亮,包大勇,等.蚀刻腔条件对刻蚀工艺的影响研究[J].半导体技术,2008,33(12):1088-1090.

[4] 温梁,汪家友,刘道广,等.MEMS器件制造工艺中的高深宽比硅干法刻蚀技术[J].微电子技术,2004(6):120-123.

[5] 周宏,赖建军,赵悦,等.SF6/O2/CHF3混合气体对硅材料的反应离子刻蚀研究[J].半导体技术,2005,30(6):28-31.

[6] 敬小成,黄美浅,姚若河.携带气体对二氧化硅敢发刻蚀的影响[J].微电子学,2004,35(5):456-459.

[7] Choi CJ,Kwon OS,Seol YS,et al.Ar addition effect on mechanism of fluorocarbon ion formation in CF4/Ar inductively couple plasma[J].J Vac Sci Technol, 2000,18(2):811-819.

[8] 陈永生,汪建华.氩气对多晶硅刻蚀的影响[J].表面技术,2003,32(2):19-21.

[9] Olthoff JK,Wang Y.Studies of ion bombardment in high density plasma containing CF4[J].J Vac Sci Technol,1999,17(4):1552-1555.

[10]张庆钊,谢长春,刘明,等.90nm硅栅过刻蚀工艺中功率对等离子体性质的影响[J].半导体学报,2007,28(10):1612-1614.endprint