3D封装的故障隔离与故障分析

2021-07-04刘晓婷

刘晓婷

(中国电子科技集团公司第四十七研究所,沈阳 110000)

1 引言

随着微电子封装朝着更小、更轻、更薄的方向发展,用户对超大规模集成电路的低功率、轻型及小型封装的生产技术提出了越来越高的要求,为此,3D封装技术应运而生[1-2]。3D封装就是把IC芯片一片片叠合起来,在Z方向垂直互连,将平面组装向垂直方向发展为立体组装。这种三维技术允许基本电路元器件(比如电阻、电感、电容、二极管和三极管)在垂直方向堆叠,而不仅仅是平面上的互连,从而可以使单位面积上具有更高的集成度[3]。然而随着封装密度的提高,器件的失效模式和失效机理愈加复杂[4-6]。3D封装工艺中的故障隔离和故障分析方法,对于3D封装工艺的改进和优化就显得尤为重要。

2 3D封装技术

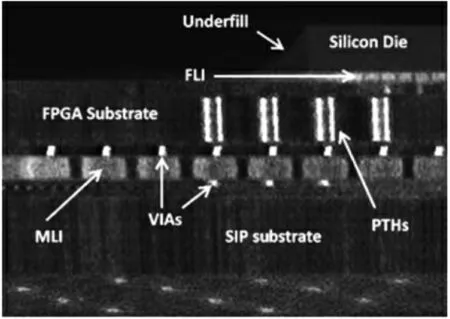

典型的系统级封装(SIP,System In a Package)示意图如图1所示。一个POP(POP,Package on Package)构造的3D封装是将以球面网格阵列(BGA,Ball Grid Array)形式封装的现场可编程门阵列(FPGA,Field Programmable Gate Array)与中央处理单元(CPU,Central Processing Unit)芯片一起安装在公共封装基板上。FPGA的封装和基板之间的焊点称为中级互连(MLI,Mid-Level Interconnect),CPU到基板和FPGA芯片到FPGA基板之间的焊点称为一级互连。由于多层焊料互连、硅芯片和封装集成在一个SIP封装中,会造成许多故障,例如焊点脱焊或在第一级互连或中级互连中出现裂纹,甚至FPGA基板或SIP基板上都会出现基板裂纹。由于较高的集成度,在这种复杂的封装架构中,对故障位置加以隔离,以及获取失效特性、进行物理失效分析,便成为必不可少的重大挑战[7-8]。

图1 POP构造的SIP封装的示意图

3 非破坏性故障隔离和故障分析

3.1 开放性和高阻故障隔离

非破坏性故障隔离技术是一种能在短时间内找到3D封装中的多种失效情况的技术。对于开放性和高阻故障,时域反射(TDR,Time Domain Reflec tometry)以及光电太赫兹脉冲反射(EOTPR,Electro Optical Terahertz Pulse Reflectometry)都是非常有效和流行的隔离技术。

TDR是一种传统的低成本非破坏性故障隔离技术,它的原理是在封装互连中注入35~40ps的上升时间的步进电脉冲,并通过收集从封装中反射的信号来分析沿电路的阻抗变化。将失效单元的反射波与良好参考单元和裸基板的反射波进行比较,可以将故障的位置隔离在芯片或封装基板中。TDR的分辨率取决于上升时间、TDR系统带宽和封装内的材料属性。时域上TDR的分辨率约为TDR上升时间的1/10~1/5。

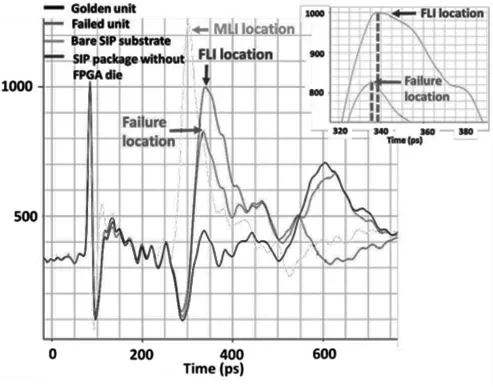

EOTPR是TDR的下一代技术,在分辨率上有进一步提升。不同的是,EOTPR采用超快激光脉冲产生一个带尖锐峰值的40GHz到4THz的电脉冲,注入到待检测的封装中。由于EOTPR采用脉冲峰值作为输入信号,封装中的开放式互连在EOTPR光谱上显示为波峰,缩短式互连在EOTPR光谱上显示为波谷。EOTPR光谱示意图如图2所示。

图2 EOTPR光谱示意图

3.2 短路故障隔离

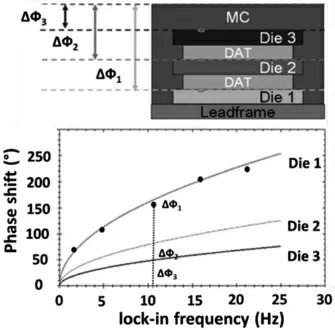

精确定位3D短路失效的关键是获取缺陷在X、Y、Z方向的位置信息。锁相热成像(LIT)是一种非常有前景的技术,它利用实时图形锁定法来定位短路故障引起的热点。锁相执成像法的检测曲线如图3所示。该方法能够辨别出3D封装中的热点,是一种检测封装中短路故障的非常有前景的非破坏性故障隔离技术。

图3 锁定频率与相移曲线图

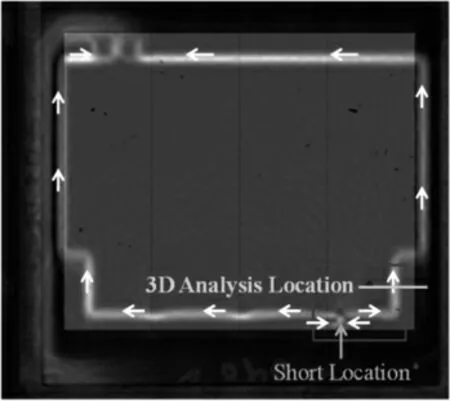

超导量子扫描干涉显微镜(SSM)被广泛应用于传统封装的短路故障无损检测中,它通过检测失效单元中由输入电流产生的磁场,并利用傅立叶变换反演技术处理磁场,可得到样品的电流密度分布图,图4给出了SSM应用的一个实例。它能够通过算法分析磁场来获取失效的Z方向位置。实际应用中的结果表明,该方法在堆叠式芯片结构的3D封装中绘制三维电流路径有很好的表现,应用前景广阔。

图4 短路故障的SSM分析

3.3 无损和高分辨率成像技术

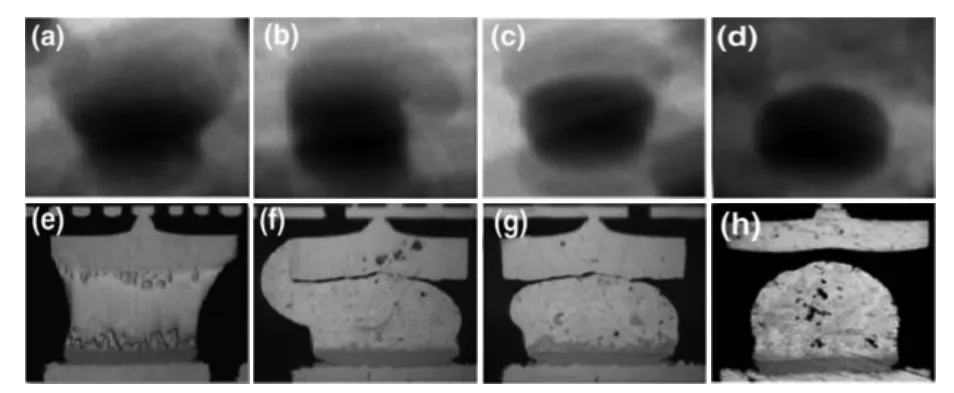

一旦故障被准确隔离,就需要使用无损和高分辨率成像技术来揭示造成失效的缺陷。二维X射线成像技术对SIP封装焊料空洞演化后多次回流检测是非常有效的一种技术。通过对比统一焊点的视觉图像,能够得到第一级互连缺陷,如图5所示。事实证明,通过二维X射线与完好的第一级互连焊点对比,有缺陷的焊点,如部分脱焊、完全脱焊、非接触式开路、焊料桥接等,可通过实时二维X射线很容易检测出来。

图5 第一级互连横截面的二维X射线成像图

此处也可用到3DCT技术,它利用一个基本的X射线源可从不同角度辐射物体的工作原理,在一个旋转的平台,以相等的角度提供角位移,并在每个角度用探测器收集二维的X射线图像。所有的二维图像通过数学叠加处理可得到的样品的三维体积。由于处理后的数据包含被测样本的容量信息,分析员可以操纵它在三维数据集的任何给定位置来显示虚拟横截面或切片视图。3DCT技术的应用实例如图6。非破坏性故障隔离技术结合高分辨率X射线成像,能够非常有效地揭示互连缺陷以及对失效展开跟踪。

图6 X射线3D CT检测到裂痕

高亮度的同步辐射X射线源具有大面积的准直光束,可以超过常规能源领域,更好地提供高分辨率的X射线成像。整体SIP封装在X射线3DCT探测下的成像如图7所示。

图7 整个SIP封装的X射线3D CT成像

实际应用的结果表明,整个16 mm×16 mm的SIP封装可以在3~20分钟内成像,有着4~8μm的分辨率。每一层的封装细节,包括硅芯片、底部填充、多个焊点、介电材料、铜通孔以及多个基板的通孔,都可以同时获得。

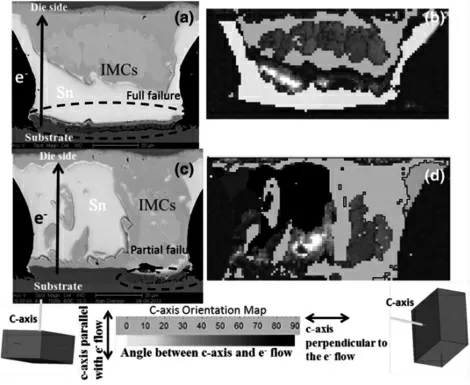

4 破坏性故障隔离和故障分析

破坏性隔离与分析包括能量色散X射线光谱分析材料分析技术(EDX)、X射线光电子光谱分析(XPS)、次级离子质谱法(SIMS)、电子背散射衍射法(EBSD)等材料分析技术,在微电子封装失效原因分析中也起着重要作用。EBSD是一种用于定义材料的晶体取向的显微结构晶体学技术。EBSD数据通常是通过SEM技术从一个横截面单元上得到的。EBSD是理解开放式互连电迁移机理的一种关键技术,在实际应用中的成像情况如图8所示。上述各方法在实用中均取得较为理想的效果。

图8 电迁移的SEM成像图。

5 结束语

针对POP或芯片堆叠式结构的3D封装,所介绍的先进故障隔离和故障分析方法,可根据不同实际情况灵活运用,视失效电特性的不同而选择非破坏性或破坏性故障隔离和故障分析法,进行失效定位,随后进行进一步深入分析,便能找到失效原因。