以双斜积分控制器为例谈EDA教学实例设计

2021-06-30陈李胜孔文浩黄文勇胡去峰

陈李胜 孔文浩 黄文勇 胡去峰 陈 卉

(电子科技大学中山学院 广东中山 528402)

一、双斜积分式ADC

双斜积分式ADC的工作原理是将输入信号转换成时间(脉冲宽度信号),输出值正比于输入信号在采样时间内的平均值,然后由计数器获得数字值。其优点是双斜式积分器对积分元件以及时钟频率的精度要求不高,具有很强的串模干扰能力。但缺点是转换精度依赖于积分时间,因此转换速率较低。双斜积分式ADC是积分式ADC的一种,图1给出了中双斜积分式ADC原理图。

图1 双斜积分式ADC原理图

当进行AD转换前,计数器未使能计数,并接通S2使电容完全放电,此时积分器的输出波形如图2的0-t1时间段。转换开始后,断开S2,此时整个转换过程分为两个阶段进行。

图2 双斜积分式ADC输出波形

(一)第一阶段,对待测电压做固定时间的积分U1

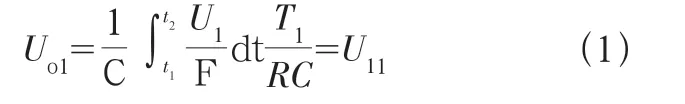

令开关S1置于待测电压V1端,积分器对待测电压V1进行固定时间T1的积分,积分器的输出波形如图2的t1-t2时间段。积分结束时积分器输出电压为:

从上式可以看出,积分器的输出Uo1与U1成正比。这个过程是转换电路对输入信号的采样过程。在采样开始的时候,CPLD控制使能计数,当计数器到达N1时,这个时间正好是固定的积分时间T1。此时CPLD状态机跳转到下一状态,令开关S1切换至-VREF端,同时计数器清零,采样阶段结束。

(二)第二阶段,对参考电压固定速率积分

采样一段结束后,因为参考电压-VREFEF的极性与U1相反,积分器反向积分,积分器的输出波形如图2的t2-t3时间段。此时CPLD使能计数器,经过T2时间,积分器输出电压为0,过零比较器输出高电平,CPLD关闭计数器,此时的计数器的计数值为N2。

同时通过CPLD的状态机控制电路使开关S1与V1相接,重复第一步。双斜式积分型ADC输出波形如图2所示。

分析双斜积分ADC的工作原理以及波形可以得到:

根据N1、N2与T1、T2的关系,最终可以得到:

双积分式ADC的输出正比于输入信号的平均值,所以它的优点是工作性能稳定且抗干扰能力强。由公式分析可以看出,积分器的积分过程的时间常数相等,计数器的计数结果与RC无关,所以,该电路对RC精度的要求不高,而且电路结构简单。

二、双积分式AD转换器的EDA实现

(一)状态机实现控制双斜积分ADC

有限状态机(Finite-State Machine,FSM)是表示有限个状态以及在这些状态之间的转移和动作等行为的数学模型。反映从系统开始到现在时刻的输入变化的状态。本实例使用VerilogHDL实现状态机来控制双斜积分ADC的不同工作状态。

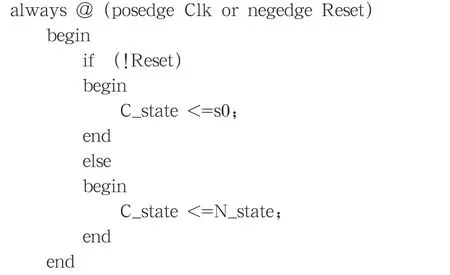

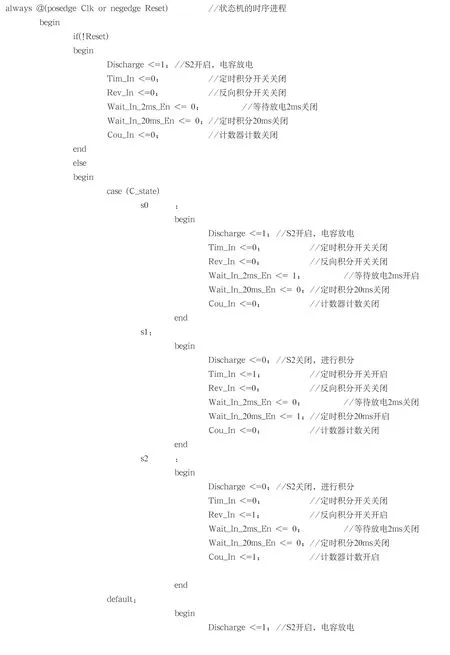

状态机采用三段式状态机来进行编写,第一段用时序逻辑描述C_state(现态)和N_state(次态),第二段用组合逻辑描述状态转移,第三段用时序逻辑描述输出。

第一段用时序逻辑描述C_state(现态)和N_state(次态):

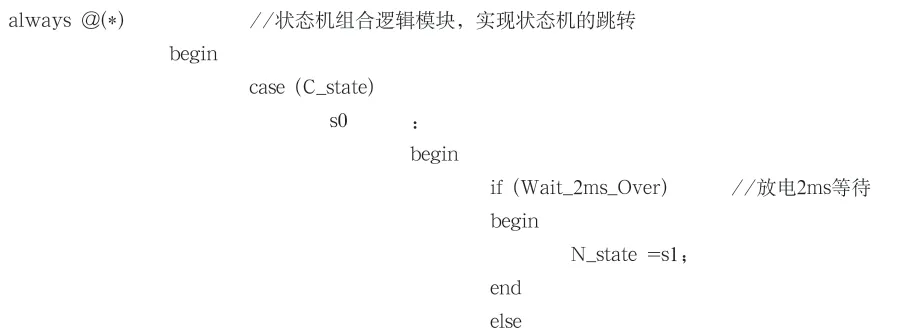

第二段用组合逻辑描述状态转移,该模块主要用来实现三个状态在什么时候实现状态转移。

第三段用时序逻辑描述输出,对应各个状态时各个控制信号组合逻辑的输出。

(二)Verilog HDL实现定时器和计数器

本实例所用的主控芯片EPM570T100C5N的工作时钟是16MHz,经过时钟分频产生1KHz的时钟用于定时器模块的工作频率。整个双斜积分式ADC的定时分为还未进行积分阶段的放电阶段以及积分阶段的定时积分,分别是2ms和20ms。这些定时值通过分频器的方式产生。

整个双斜积分式ADC的定时分为还未进行积分阶段的放电阶段以及积分阶段的定时积分,分别是2ms和20ms。为了计数得到反向积分的值,这个时候通过经过分频产生1MHz的工作频率,这个频率用于计数器模块,求出式3中的N1,N2进而计算出ADC的转换值。

在进行测试的时候,对每组电压值都进行多次测量取平均的方式来提高测量精度。

三、结论

状态机是数字逻辑设计中的重要内容,本身相对复杂。本教学实例结合积分式模数转换器的控制方法,引入三段式状态机,更利于学生理解状态机的写法和应用。本实例在加深学生理解如何使用状态机的同时,也能让学生进一步掌握积分式模数转换器的控制方法。从教学实践的结果来看,有较好的效果。如何丰富此教学实例的外围,让学生在学习状态机的同时也学习使用Verilog HDL代码实现常用外设的控制是下一步丰富教学实例的重点。让EDA的学习不仅仅是代码的练习,更是结合实际硬件的综合训练。这样才能培养出更具有工程应用能力的学生。