基于Nios II的宽频小信号等精度测频系统*

2021-06-24郑志旺李锦明

郑志旺, 李锦明, 方 帆

(1. 中北大学 仪器与电子学院, 山西 太原 030051; 2. 中国人民解放军32382部队, 北京 100072)

随着基于频率信号的测试技术的广泛应用, 对于频率计的高精确度测量需求, 尤其是小信号的频率测量[1-4]需求也逐渐增加. 目前, 国内外宽频小信号频率计的设计成本、 售价都相对较高, 并且具有体积、 重量较大, 不方便携带等特点[5-7], 为了提高宽频小信号的等精度频率频率计的精度、 稳定性、 简易性等, 本文基于FPGA和Nios II软核来设计等精度频率测量系统. 采用等精度测量频率的算法, 能够保证不同频率下测量值的相对误差是等精度的, 并且通过信号调理电路的处理, 可以测量幅值范围10 mV~3.3 V的频率信号. 本系统可以充分利用FPGA逻辑模块的高速并行计算的特性和Nios II软核人机交互的控制优势, 从而降低硬件系统的复杂性.

1 系统原理与总体设计

1.1 等精度测频原理

频率计在FPGA上实现的基本原理是在一段闸门时间T内, 对待测信号的上升沿计数计为fx_cnt, 同时对基准时钟信号的上升沿计数计为fs_cnt, 设待测信号频率为fx, 基准时钟信号频率为FS[8-9]. 由频率、 上升沿计数个数、 闸门时间的关系可以得到

(1)

(2)

由式(1)和式(2)联立可得待测信号频率为

(3)

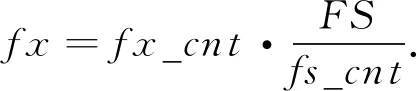

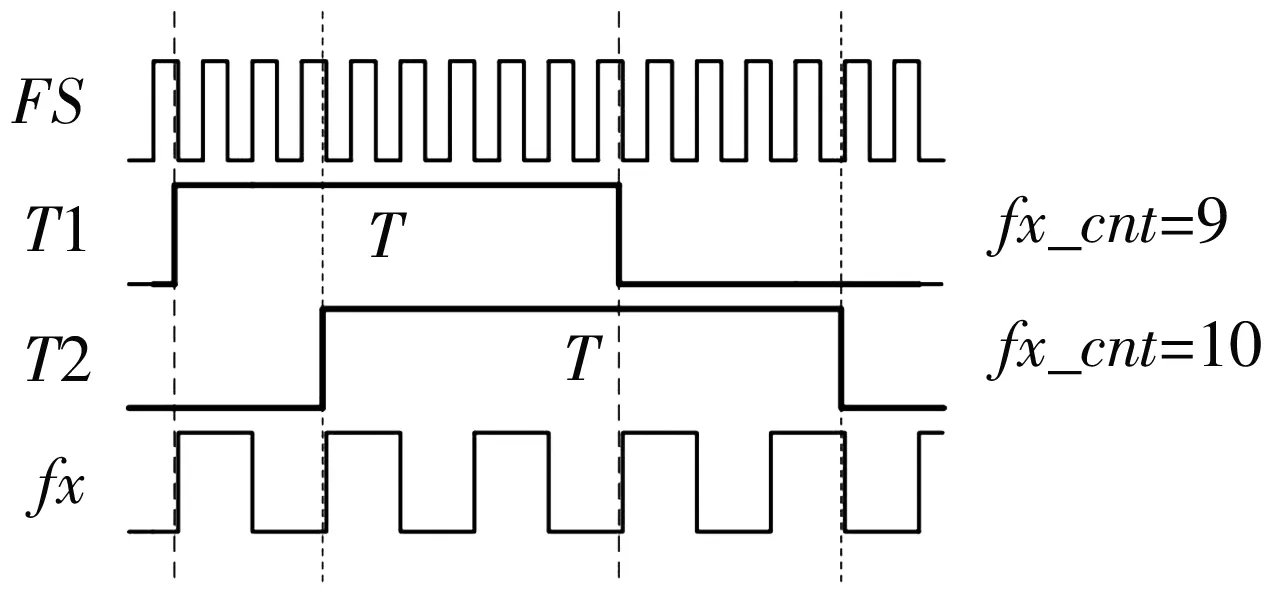

传统频率计的闸门时间T由基准时钟FS同步产生, 时间T是基准时钟周期的整数倍, 此时对基准时钟上升沿的计数值fs_cnt没有误差[10-11].但是, 门控信号的上升沿与待测信号的上升沿可能不是对齐的, 传统频率计的测量原理如图1 所示, 两次相同闸门时间内待测信号上升沿的计数结果可能不一致, 计数值fx_cnt可能存在±1的误差, 测得频率值的相对误差为

图1 传统频率计测量原理图

(4)

由式(4)可知, 测量结果的相对误差随着待测信号频率的减小而增大, 在量程范围内不能保证精度不变.

等精度频率计闸门时间T由待测信号fx同步产生, 时间T是待测信号时钟周期的整数倍[12-15], 此时对待测信号上升沿的计数值fx_cnt没有误差, 基准时钟信号脉冲的计数值存在±1的误差, 此时测量结果的相对误差为

(5)

由式(5)可知, 测量结果的相对误差不随频率的变化而改变, 能够在量程范围内保持统一的精度. 当测量的闸门时间设定为1 s时, 基准时钟信号的频率为100 MHz时, 理论的测量精度能够达到10-8, 等精度频率计的测量原理图如图2 所示.

图2 等精度频率计测量原理图

1.2 系统总体设计方案

系统硬件的主要组成部分有FPGA主控模块、 信号调理模块、 串口通信模块、 LCD显示器驱动模块等. 由于待测信号的幅值大小是不确定的, 所以首先需要对待测信号进行整形, 通过频率信号调理模块电路, 将待测信号波形整形为3.3 V的矩形波, 并保持其频率不发生改变, 从而方便FPGA对待测信号进行准确的计数.

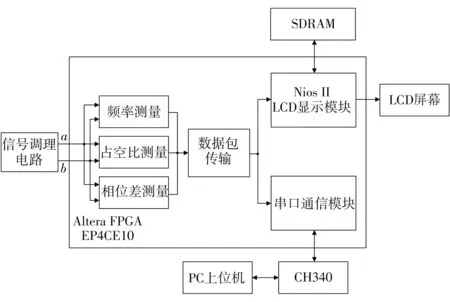

通过FPGA主控模块实现对两路整形后信号的频率、 占空比、 相位差的测量, 并在FPGA上搭建嵌入式片上系统Nios II软核来实现人机交互功能和测量结果的显示, 编写运行在Nios II软核上的C语言程序, 驱动LCD屏幕显示测量的结果, 同时FPGA通过串口通信电路将测量结果发送到PC端的上位机完成显示, 系统的总体设计框图如图3 所示.

图3 系统总体设计框图

2 系统硬件设计

2.1 信号调理电路设计

信号调理电路的主要功能是对待测信号的幅值和波形进行自动调整, 在保持待测信号频率不发生改变的情况下, 将不同幅值的正弦波、 方波信号整形为幅值是3.3 V的方波信号, 从而方便FPGA对待测信号进行检测, 信号调理电路的系统框图如图4 所示, 其中包括增益电路和比较器电路.

图4 信号调理电路系统框图

自增益电路由可控增益放大器VCA810, 宽带放大器OPA690, 单电源比较器AD8561, 通用运算放大器TL082组成, 通过调节AD8561模块电路中的电位器设定比较电压为1.65 V, 当VCA810输出电压小于1.65 V时, 通过反馈电路控制VCA810来增大放大倍数; 同理, VCA810输出电压大于1.65 V时, 减小其放大倍数, 最终将VCA810输出波形的幅值控制在1.65 V, 再经过OPA690放大输出幅值为3.3 V的波形.

整形模块的主要芯片选用TLV3501, 它是一款延迟为4.5 ns的超高速比较器, 它将自增益电路输出的波形整形为3.3 V的方波, 然后输出给FPGA进行计数等工作, 完成对测量范围内不同幅值的正弦波、 方波的频率测量.

2.2 LCD显示电路设计

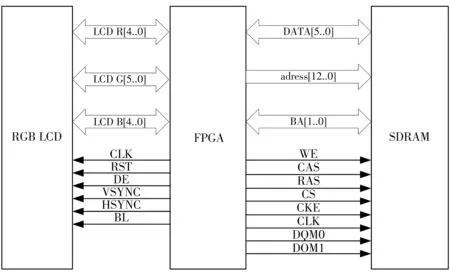

LCD显示模块采用带有RGB接口的LCD屏幕, 并使用SDRAM作为LCD的数据缓存, FPGA与LCD、 SDRAM的电路连接示意图如图5 所示.

图5 LCD显示模块示意图

2.3 串口通信电路设计

系统中设计了由FPGA控制发送的串口通信电路, 用于将测量得到的数据发送到PC端的LabVIEW上位机进行结果的计算和显示. 串口通信芯片选用CH340, 它将TTL电平转换为USB电平, 这样能够通过PC的USB端口进行数据的收发, 并且该芯片支持的通讯波特率为50 bit/s~2 Mbit/s, 能够满足显示设计的需求, 串口通信模块与FPGA的连接示意图如图6 所示.

图6 串口通信模块与FPGA的连接示意图

3 系统软件设计

Altera FPGA的程序使用Verilog语言在Quartus II开发环境上进行编写. FPGA内部模块结构图如图7 所示, 主要由频率测量、 占空比测量、 相位差测量、 数据包传输、 LCD显示、 串口通信等模块组成. 将经过信号调理电路整形的频率信号接到FPGA的计数输入管脚, 然后进入到频率测量、 占空比测量、 相位差测量等模块, 完成计数、 计算等测量工作, 再将测得的结果打包传输到串口通信模块和LCD显示模块, 然后通过串口通信模块将结果传输到上位机进行显示, 通过LCD显示模块控制LCD屏幕, 来实现LCD屏幕显示结果等功能.

图7 FPGA内部模块结构图

通常控制LCD屏幕显示FPGA测量的结果方法有两种: 一是在FPGA中通过逻辑电路直接控制LCD, 但是控制程序较为复杂; 二是FPGA将数据发送给单片机, 由单片机控制LCD显示结果, 但是所需芯片的数量增加, 导致电路板占用面积增大, 硬件设计更复杂. 本设计在FPGA内部搭建Nios II软核用于控制LCD, 避免了以上两种方法的缺点, 既能简化硬件电路, 又能降低软件程序设计的难度, 发挥了FPGA逻辑电路和Nios II软核处理器优势互补的特性, 有效缩短了开发周期.

3.1 FPGA逻辑部分模块设计

3.1.1 等精度测频模块

等精度频率测频模块的主要功能有产生门控信号、 基准时钟脉冲计数、 待测信号脉冲计数等. 基准时钟是FPGA内部的PLL所产生的100 MHz时钟. 根据等精度频率测量的原理可知闸门时间T是由待测信号同步产生的, 时间T是待测信号周期的整数倍, 在实际的FPGA计数过程中, 首先产生周期为1 s的预置闸门信号, 同时对待测信号和基准时钟信号的上升沿进行计数, 当1 s的预置闸门时间结束后, 在待测信号的下一个上升沿完成计数, 然后即可计算出测得的频率值.

3.1.2 占空比测量模块

当待测信号是方波时可以测量方波的占空比, 占空比测量模块的基本原理是在待测信号的多个连续周期内对基准时钟进行计数, 采用这种多周期测量占空比的方法能够提高测量的精度. 高电平期间的累计计数值为high_cnt, 低电平期间的累计计数值为low_cnt, 则待测信号的占空比为

(6)

3.1.3 相位差测量模块

当a、 b两个通道输入的待测信号是频率相同的方波时, 可以测量两个通道的方波的相位差. 先将两个通道的方波进行异或, 得到一个相位差信号, 同理, 使用多周期计数的方法计算出的相位差信号的高电平的时间就是两个方波的时间间隔, 即可计算出两路方波信号的相位差.

3.1.4 数据包传输模块

将频率测量模块、 占空比测量模块、 相位差测量模块测得的计数值打包成一个224位的数据, 传输给Nios II和串口通信模块, 再进行相应的计算后完成最终结果的显示. 打包后的数据格式示意图如图8 所示, 通过freq_a、 freq_b可以计算出a、 b通道的频率值, 通过high_cnt_a、 low_cnt_a、 high_cnt_b、 low_cnt_b可以计算出a、 b通道的占空比, 通过interval_ab可以计算出a、 b通道波形的相位差. 串口通信模块将数据包中的224位数据, 通过串口依次发送给上位机, 上位机接收并解析数据后显示测量结果.

图8 传输数据格式示意图

3.2 Nios II显示程序设计

3.2.1 Qsys系统上搭建Nios II处理器

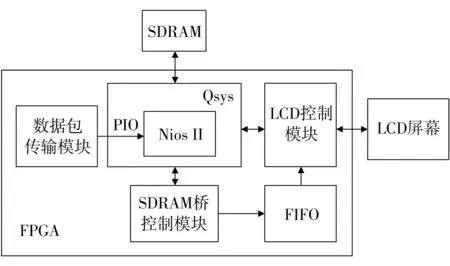

Nios II是Qsys系统集成工具上的一个软核处理器, 主要使用Nios II来接收FPGA逻辑模块发送的测量结果并驱动LCD显示测量结果. 基于Nios II软核的LCD显示模块的系统框图如图9 所示, FPGA内数据包传输模块将测量得到的结果通过PIO将数据传输到Qsys系统, Nios II处理器通过PIO读取数值并进行计算, 再把结果写入到SDRAM中, 由SDRAM桥控制模块从SDRAM中读取显示数据, 并写入到FIFO中, 最后LCD控制模块将显示数据读出并写入到LCD屏幕完成测量结果的显示.

图9 Nios II显示模块系统框图

3.2.2 Nios II上程序的编写

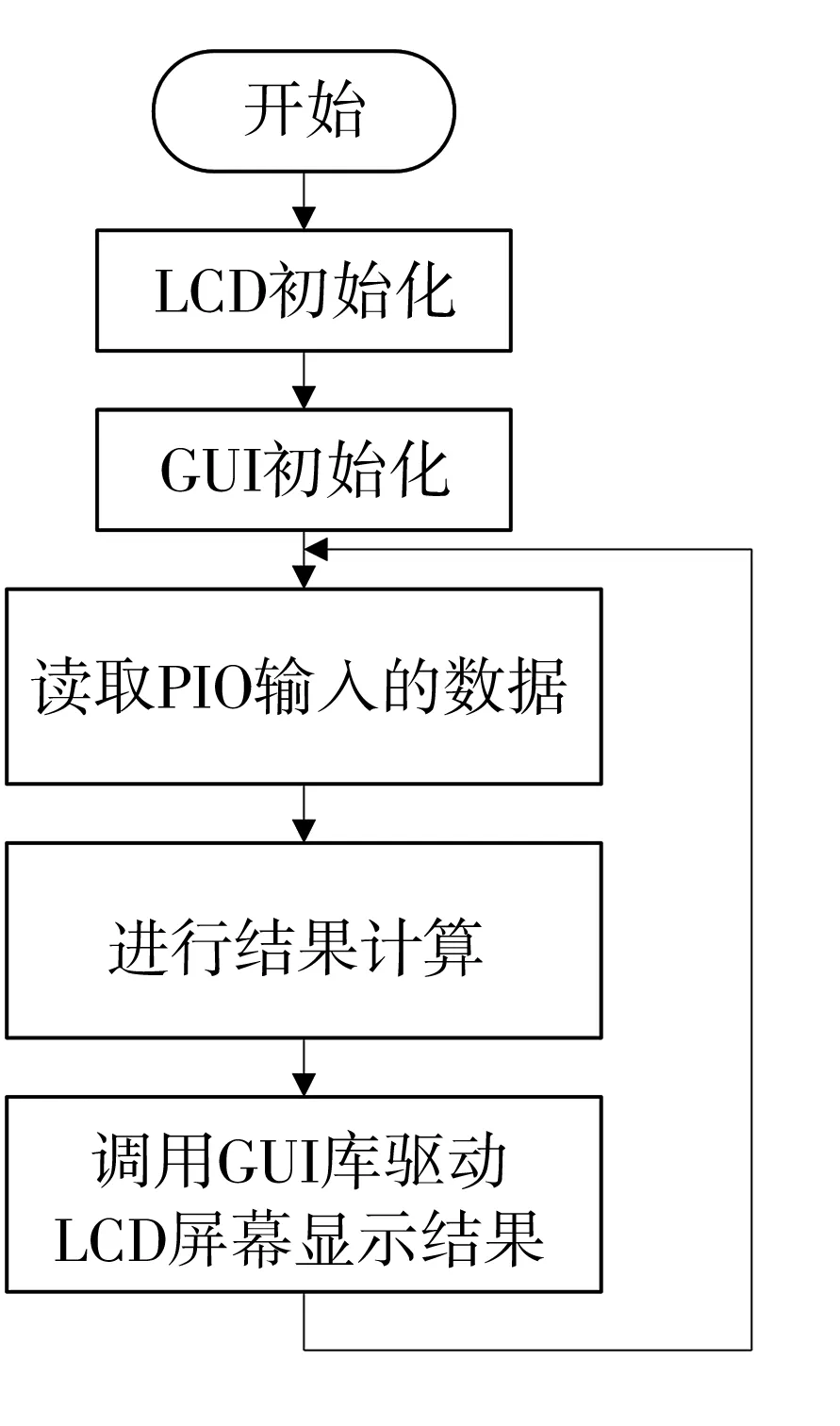

FPGA硬件平台搭建完毕后, Nios II处理器的程序使用C语言编写, 程序设计流程图如图10 所示, 首先进行LCD初始化、 GUI初始化等工作, 然后通过读avalon总线PIO的地址上的数据 来获取片内逻辑电路输出的数据, 读取最近7次闸门时间内测量得到的结果, 去除最大值和最小值, 对剩余的5个数据取平均值作为最终的测量结果, 以进一步减小测量的误差, 最后调用GUI库来完成测量结果在LCD屏幕上的显示.

图10 Nios II程序设计流程图

4 测试结果与分析

4.1 测试步骤和方法

首先进行模拟电路部分的测试, 对待测频率信号进行自增益放大, 使输出幅值可以达到比较器正常的工作要求, 整形后输出幅值为3.3 V的方波信号, 可以保证FPGA计数的准确性.

系统整体测试时, 先使用信号发生器产生不同幅值和不同频率的方波、 正弦波信号, 然后连接到测试样机的信号输入端, 使用测试样机分别进行多组数据的频率测量, 最后进行测试结果的误差分析.

4.2 方波和正弦波信号的频率测试

分别测试不同频率、 不同幅值的方波信号, 在方波信号幅值为10 mV、 200 mV、 2 V的条件下, 分别输入频率为50 Hz、 1 kHz、 100 kHz、 10 MHz、 30 MHz、 50 MHz的信号, 测试结果如表1 所示. 正弦波信号频率的测试方法同上, 在正弦信号幅值为10 mV、 200 mV、 2 V的条件下, 分别输入频率为50 Hz、 1 kHz、 500 kHz、 15 MHz、 50 MHz的信号, 测试结果如表2 所示.

表1 方波信号频率测试结果的相对误差

表2 正弦波信号频率测试结果的相对误差

4.3 测试结果分析

由表1 可知, 在方波信号频率固定不变的情况下, 幅值为10 mV、 200 mV、 2 V时, 计算得到测量结果的相对误差基本相同; 在方波信号幅值固定不变的情况下, 频率为50 Hz、 1 kHz、 100 kHz、 10 MHz、 30 MHz、 50 MHz时, 测量结果的相对误差也基本相同, 均保持在10-6范围内. 由表2 可知, 在待测信号为正弦波时, 信号强度不同、 频率不同的情况下测量频率值的相对误差仍在10-6范围内, 能够实现等精度测量频率.

5 结 论

本文对小信号频率的测量做了优化, 设计了基于FPGA和Nios II软核处理器的宽频小信号等精度测频系统. 对不同幅值、 不同频率的待测信号进行了测量, 并对测量数据进行了分析, 结果表明, 系统能够精确的测量电压幅值最小为10 mV 的小信号的频率, 测量结果的相对误差为10-6. 频率计使用FPGA作为核心主控, 由逻辑电路完成多路频率测量等并行任务, 由Nios II软核处理器完成LCD驱动显示等人机交互工作, 充分发挥了逻辑电路和软核处理器优势互补的特点, 提高了开发效率, 降低了硬件电路的复杂性, 本系统在便携式频率测量方面具有实际应用价值.