化学镀镍钯金LTCC基板工艺研究

2021-06-21陈晓勇贾少雄王颖麟

陈晓勇 贾少雄 王颖麟 李 俊

(中国电子科技集团公司第二研究所,山西 太原 030024)

0 引言

低温共烧陶瓷(LTCC)技术作为多芯片组件(MCM)技术的重要分支,能够满足组件或者模块的小型化、集成化、轻量化和高可靠性的需求,被广泛应用于电子通信、雷达探测以及电子对抗等领域。鉴于金(Au)导体的优良导电性和稳定性,LTCC基板通常采用Au作为导体材料。为进一步降低LTCC基板加工材料成本,将银(Ag)引入LTCC导体材料体系,构成金银混合体系。但是,LTCC基板通常具有复杂的腔体结构,内层金属可以采用银导体,但外层仍然需要采用金导体。与全金体系相比,金银混合体系成本优势很有限。所以,如何降低LTCC基板的材料成本一直是制约LTCC技术应用及推广的瓶颈。

为解决化学镀镍浸金(ENIG)一直存在的“黑盘”问题,化学镀镍镀钯浸金(ENEPIG)被提出并验证有效。近年来,ENEPIG技术被引入LTCC行业,具体表现为:LTCC基板内外层电路均采用金属银作为导体,共烧后在银导体表面进行ENEPIG处理。该技术方案具备以下两个优点:

(1)在银导体表面镀覆Ni/Pd/Au镀层,能够有效防止银发生氧化和硫化;

(2)Ni/Pd/Au镀层具备与金丝/金带键合、锡铅焊和金锡共晶焊的能力,是LTCC领域理想的“万能金属层”。

与金银混合体系相比,LTCC全银基板ENEPIG方案能够大幅降低LTCC材料成本[1][2];同时具备多种功能特性的Ni/Pd/Au镀层简化了LTCC浆料体系结构,避免了不同类型浆料间共烧带来的失配问题,具有明显的价格优势和工艺优点。近年来,国内关于ENEPIG的研究主要集中在化镀溶液和工艺参数上,对LTCC表层银导体烧结形貌以及LTCC基体的耐酸碱腐蚀性鲜有报道[3]-[8]。本文从LTCC银浆烧结形貌出发,结合LTCC基板的共烧特点,对LTCC全银基板ENEPIG工艺进行了全面、系统的研究。

1 实验过程

1.1 工艺流程

LTCC全银基板ENEPIG工艺流程如图1所示。

图1 LTCC全银基板ENEPIG工艺流程图

1.2 ENEPIG原理

1.2.1 化学镀镍

LTCC基板在化学镀镍前需要活化处理,即在银导体表面吸附粒子作为催化中心,以次磷酸盐[H2PO2]-作为还原剂,形成Ni-P合金,化学反应方程式见式(1)~式(4)。镍镀层较厚,一般为3 μm~5 μm。镍镀层能够有效阻挡银原子向表层迁移。

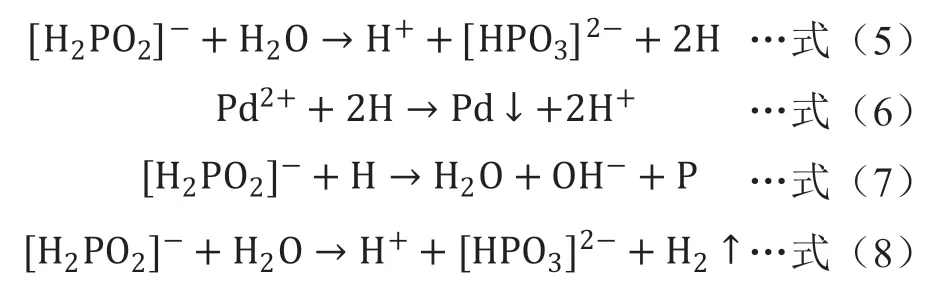

1.2.2 化学镀钯

化学镀钯过程与化学镀镍类似,仍以次磷酸盐[H2PO2]-作为还原剂,不同的是,化学镀钯是自催化氧化还原反应,化学反应方程式见式(5)~式(8)。钯层主要是阻挡镍原子向金层扩散,钯层通常较薄,厚度为0.1 μm~0.2 μm。

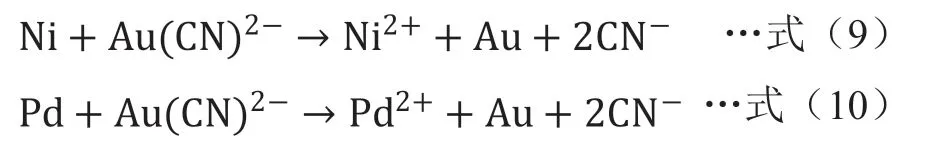

1.2.3 化学浸金

化学浸金是置换反应,化学反应方程式见式(9)~式(10)。随着底层镍原子和钯原子的消耗,被还原的Au原子覆盖在镍原子和钯原子表面,阻止置换反应的继续进行,所以金层较薄,约为0.1 μm~0.35 μm。

2 分析与讨论

2.1 表面银层形貌

LTCC基板表面银层作为ENEPIG的底层金属,其烧结形貌直接影响ENEPIG的效果。为保证银层与陶瓷基体之间具有良好的附着力,在银浆中会添加一定比例起粘接作用的无机玻璃粉,但是在烧结过程中,过量的玻璃成分会填充到银晶粒之间的晶界中,导致银层晶粒之间连续性较差,进而导致漏镀等问题。以杜邦公司的A1和A2两款银浆进行烧结对比实验。如图2所示,A1银浆共烧后表面玻璃(灰色区域)含量较多,银晶粒排列较为分散,晶粒之间被大量玻璃包裹,甚至出现玻璃体大量团聚的现象,无法形成较为连续的银层晶粒表面。A2银浆共烧后银晶粒尺寸均匀,排列紧密,观察不到明显的玻璃聚集区。A2银浆是进行ENEPIG理想的导体材料。

图2 在500x倍下烧结形貌图

另外,烧结后的银层需要注意防止氧化和硫化,不能长时间放置于空气环境中,建议将银基板放置于氮气柜中或者在真空环境下储存。

2.2 表面阻焊

通常会要求银层表面印刷阻焊图形。在ENEPIG过程中,LTCC基体和表面阻焊均要受到化镀液的腐蚀性攻击,阻焊层不能出现剥离和脱落等现象。实验中共考察了三种类型阻焊,其中Z1为Ferro生瓷阻焊,Z2和Z3分别为杜邦公司生产的低温玻璃釉和高温玻璃釉。在经过常规ENEPIG工艺后的表面形貌看,Z1阻焊由化镀前具有一定硬度的固体转变为呈酥松态粉末,失去与基板间的附着力,完全丧失阻焊能力;Z2阻焊无法抵抗化镀液的腐蚀,出现了明显的脱落;Z3化镀后阻焊图形完整,用3M胶带测试阻焊膜层附着力,未出现剥离的情况,能够满足使用要求。

2.3 内层银导体膜厚

在银浆料状态固定的情况下,采用325目、乳胶厚度15 μm常规网版,通常银导体干膜厚度可以达到20 μm以上。当基板内层同一区域出现多层印刷叠加时,共烧后表层该区域会明显高于其他无印刷图形的区域,对后道芯片粘接或者金丝键合等过程造成影响。对于LTCC一体化封装基板来说,表面围框焊接区下方印刷多层叠加也会导致围框焊接因气密性不达标而失效。从材料烧结匹配性的角度考虑,内层银导体较厚更容易导致基板烧结翘曲和内部分层等不良后果。

为对比基板层压后的效果,选择大面积网格印刷图形作为研究对象,同一印刷图形连续叠加10层,考察层压后基板表面平整度。实验表明,通过将印刷网版乳胶厚度减薄到10 μm以下,内层银浆干膜厚度可以控制在10 μm~15 μm范围内,基板表层平面度可以控制在50 μm以下,满足后道装配要求。

2.4 ENEPIG主要质量问题

2.4.1 渗镀金

LTCC基板渗镀金具体表现为基板表面非金属化区域被镀金层覆盖,导致外观不合格,甚至造成相邻焊盘或者线条之间短路,导致渗镀的主要原因包括:

(1)基板镀镍前活化过度,导致基板表面出现点状或区域性镍渗镀,进而导致渗镀金。由于活化液中Pd2+浓度过高,或者活化温度较高,导致Pd2+大量附着在银导体和陶瓷颗粒表面,形成催化中心,导致镀镍时Ni2+被次磷酸根还原为金属Ni,附着在陶瓷表面。

(2)基板镀钯时出现渗镀,导致渗镀金。钯液浓度较高,或者加热温度过高,导致镀钯反应剧烈,出现渗镀钯。

有效解决措施:

(1)降低活化液中Pd2+浓度,同时降低活化液温度,减缓Pd2+基板附着速率;

(2)活化后增加后浸处理,把附着在陶瓷表面的Pd2+去除掉;

(3)降低钯液温度和镀钯时间,减少Pd金属颗粒在陶瓷表面的沉积。

2.4.2 漏镀金

LTCC基板漏镀主要表现为焊盘表面存在局部点状漏镀和整个焊盘漏镀。对焊盘漏镀区域进行EDS(电子扩散X射线)能谱仪分析,其元素组成见表1。从表中可以看出,漏镀区域检测到少量的Si元素,推测为SiO2玻璃。说明在刻蚀环节,银导体表面玻璃成分没有被有效去除掉,导致镍层无法在玻璃表面沉积,最终焊盘表面出现漏镀。

表1 焊盘漏镀区域EDS分析组成元素

对于焊盘整体漏镀的情况,在排查原因时,发现一个有趣的现象:出现漏镀的焊盘往往呈现同一电气网络的特性。如图2(A)所示,腔体底部露出焊盘通过内层线条相互连通,图中呈现出线条两端焊盘漏镀。初步判断,漏镀焊盘表面电位较高,活化时Pd2+无法沉积在银层表面,镀镍时因缺少催化中心,Ni2+无法被还原沉积在银层表面。更深层次的原因,还有待今后进一步研究。

图2 焊盘漏镀形貌图

漏镀与渗镀是一对矛盾体,解决漏镀金的有效措施包括:(1)提高活化液中Pd2+浓度,同时升高活化液温度,提升Pd2+基板附着能力;(2)活化后减少后浸处理的时间,保证银导体表面附着有充分的催化媒介。

2.4.3 陶瓷腐蚀

在化学镀过程中,陶瓷基体势必会受到各种酸性或者碱性溶液的腐蚀。实验中选取了3种常用的LTCC熟瓷样品:Ferro A6M、Dupont 951和9K7生瓷。将烧结后的样品浸泡在氢氧化钠溶液(浓度为30 g/L)中,30 min后取出观察陶瓷表面形貌。实验结果表明,Ferro A6M陶瓷表面呈酥松粉末状,腐蚀情况严重;Dupont 951陶瓷表面颜色变化不大,未发现明显腐蚀痕迹; Dupont 9K7陶瓷腐蚀程度介于两者之间,陶瓷表面发白,在显微镜下观察到表面附着有粉末状颗粒物。

从材料组分上分析,Ferro A6M烧结体为Ca-B-Si微晶玻璃,耐酸碱腐蚀性差,不具备化学镀的基本条件。Dupont 951材料为玻璃+陶瓷复合物,主晶相为CaAl2Si2O8,能够有效抵抗酸碱溶液的腐蚀。Dupont 9K7材料为微晶玻璃+陶瓷相,耐酸碱腐蚀程度有限。所以,在化镀过程中,必须严格控制基板刻蚀时间和浸金时长。

2.4.4 镀层剥离

在测试基板镀层附着力时,常见的一类缺陷是金镀层被胶带剥离,露出底部金属镍或者银。或者在对化镀基板进行砂轮划片时,同样观察到基板边缘出现金镀层起皮剥离的现象。通过金丝键合拉力测试,键合拉力不达标,键合点金层被拉起。

导致镀层附着力差的原因是基板表面存在污染,或者镍缸被污染,导致镍层与银层之间附着力较差,包括部分镍层在内直接被胶带粘掉。对浸金后外观不合格的基板进行表面镀层清洗去除处理,进行二次镀镍,镀层出现剥离较为明显。所以,镀镍前一定要保证基板表面无污染,镍缸活性稳定,才能保证镀层拥有良好的附着力,另外,LTCC基板不建议二次镀镍,不然镍层附着力无法保证。

2.4.5 金层发白

金层发白是常见的一类缺陷。通过X射线膜厚测试仪测量镀层厚度,发现镍钯层厚度正常,但金层偏薄。这类缺陷主要出现在金槽金离子浓度偏低,导致金层沉积速率缓慢。解决这一问题的有效办法是加强对金槽离子的浓度监控,依据化镀面积推测金离子消耗情况,及时补充金盐,保证金离子浓度稳定在合理范围内。

另外,对于LCC一体化封装基板来说,表面焊接金属围框要求金镀层能够承受300 ℃以上的高温热处理,金层不发生变色,但共晶后金层发白。对共晶前后镀层厚度进行对比,共晶后金层颜色正常和发白的基板Ni/Pd/Au镀层厚度均未出现明显变化。但对比金丝键合拉力结果,发现金层发白焊盘的金丝键合拉力平均值比正常基板小3 g~4 g,金丝键合时频繁出现脱丝的情况,需提高键合超声波功率。说明金层发白对金丝键合可靠性有直接影响。

从镀层结构上进行分析,在Ni/Au镀层之间引入Pd层的目的是为了阻挡Ni原子向Au层的扩散作用。解决共晶后金层发白的有效措施是:(1)加厚Pd层厚度,推荐厚度范围为0.15 μm~0.2 μm,有效抑制Ni原子的扩散过程;(2)在Pd层厚度不变的情况下,加厚Au层厚度至0.25 μm以上,使Ni原子进入金层底层晶格,不影响表面金丝键合。通过实验验证,金层发白问题可以得到很好的解决。

2.4.6 金层色斑

当化镀后的基板在空气中长期放置时,少量基板金层边缘出现点状彩色斑纹,彩色斑纹从焊盘边缘向焊盘中心区域缓慢延伸。对色斑区域进行SEM形貌观察和EDS能谱分析,在色斑区域检测到少量Ag元素,与正常金层区域相比较,色斑区域Au元素含量明显减少,如表2所示。

表2 EDS分析组成元素

表面金层出现色斑很可能是发生了原电池反应。在化镀过程中,焊盘边缘存在侧向腐蚀,在焊盘边缘形成一定深度和宽度的沟道,镀金后用去离子水对基板进行冲洗,沟道内的残留镀液成分无法被彻底清除干净。当基板长时间暴露在空气中,在水汽媒介作用下,沟道附近的金属层与残留镀液之间发生原电池腐蚀。随着化学反应的持续进行,色斑区域从焊盘边缘向焊盘中心延伸,表层镀层被腐蚀后,底层银直接暴露在空气中,发生银的氧化或硫化,进一步加剧了焊盘色斑的进程。解决金层色斑的有效方法是:(1)减少焊盘边缘向腐蚀的程度,严格控制刻蚀和浸金时间;(2)浸金后用大量去离子水冲洗基板,然后采用热风烘干的方式,最大限度减少镀液成分在基板表面的残留;(3)化镀后的基板推荐放入氮气柜或者在真空环境下长期储存,降低基板发生原电池反应的可能性。

3 结论

通过对LTCC全银基板化学镀镍钯金工艺进行系统性研究,得到如下结论。

(1)LTCC银层烧结质量直接影响化镀镍钯金质量,银颗粒排列紧密,减少银导体表面的玻璃含量,能够得到良好的化镀效果。

(2)杜邦体系高温玻璃釉具备良好的抗镀液腐蚀性,可以作为化镀基板阻焊层来使用。

(3)通过控制网版乳胶厚度,内层银浆干膜厚度在10 μm~15 μm范围内,基板平面度优于50 μm。

(4)针对化镀镍钯金工艺存在的金层渗镀和漏镀、陶瓷腐蚀、镀层剥离、金层发白和色斑等质量问题,从机理上分析了各类问题产生的原因,提出了有针对性的解决办法,对提高化学镀镍钯金质量具有指导意义。