一种高耐压SPST 天线调谐开关设计

2021-05-19夏小辉林福江

夏小辉,林福江

(中国科学技术大学 微电子学院,安徽 合肥230026)

0 引言

随着5G 通信的迅速发展与应用,对传输数据速率的要求越来越高,目前提升数据传输速率采用的主要技术有载波聚合(Carrier Aggregation,CA)、有源天线系统(Active Antenna Systems,AAS)、多路输入/输 出(Multiple Input Multiple Output,MIMO)[1]。因为新一代智能手机中的天线数量不断增加,以及智能手机追求更大屏占比的工艺设计趋势,所以这些天线需要安装到更小的空间内,天线数量的增加、尺寸的减小导致天线效率降低,进而影响发送和接收性能、电池续航能力,甚至出现连接问题。

为了有效解决这些矛盾,智能手机中目前主要采用天线调谐[2-6]技术来提高多频段信号传输的天线效率。通过在天线不同位置与地之间连接天线调谐器(包含开关、电容与电感等),改变天线谐振频率实现多频段信号高效率传输。由于天线可能工作在失配的情况下,此时天线上的电压是正常工作时的数倍,因此天线调谐开关设计必须考虑耐压能力。一般可以通过选取GaAs 等大功率器件解决这一问题,但其成本较高,且集成度较差。因此最近几年射频开关的设计多采用SOI CMOS 工艺,相比GaAs 工艺,其兼顾成本和性能[7-8]。

由于SOI CMOS 工艺中,单个晶体管电压承受能力有限,因此该工艺下的射频开关在处理大功率信号时多采用堆叠结构[9-10]。该结构由于体端和栅端存在较大泄露电流,导致电压摆幅在堆叠结构中各级晶体管的分布不均,使得射频开关支路总的电压处理能力受到极大限制。一般可以通过体端增加偏置大电阻,提供额外的偏置电压等技术来削弱这一现象,但这需要输入独立体端控制信号且效果有限。

本文提出的高耐压天线调谐开关能在保证插损和隔离度的前提下,更好地满足大电压摆幅的工作情况:首先对传统的堆叠技术进行改进,削弱电压分布不均,显著提高支路电压处理能力;其次还使用了两级偏置电阻网络,降低电流泄露,进一步提高电压处理能力,从而更好地用于天线调谐,满足在天线失配情况下仍能正常工作。

1 天线调谐开关的整体结构与原理分析

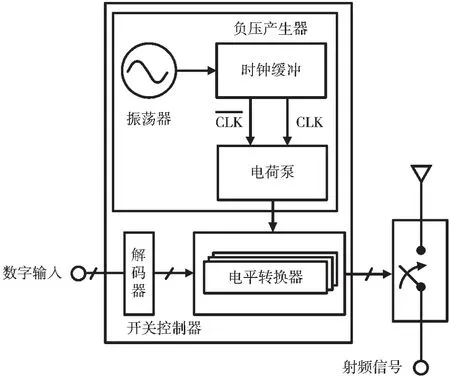

如图1 所示,本文所设计的天线调谐开关主要由开关控制器和射频开关两部分组成[11]。开关控制器由负压产生器、解码器和电平转换器构成。通过内部振荡器和时钟缓冲建立起时钟信号,从而电荷泵实现稳定的负压输出;开关控制器通过解码器和电平转换器将输入的逻辑电平0 和VDD转换成射频开关部分的控制电压VCTRL_ON和VCTRL_OFF。

如图2 所示,射频开关部分总体采用串-并联结构,两条支路的控制信号互补。当串联支路导通时,等效于小电阻,并联支路关断,等效于电容和大电阻并联,反之同理。

图1 天线调谐开关的整体框图

图2 高耐压天线调谐开关拓扑结构

2 关键电路分析与设计

2.1 体区自适应偏置

当SOI CMOS 工艺体区悬空时,体电位因为寄生电容的作用进行充放电,引起阈值电压的漂移[12]。因此每一级的晶体管采用体区自适应偏置[13],如图3所示,通过一个二极管连接体端和栅端,可以极大改善电路性能。

图3 体区自适应偏置结构

图4 为体端电势随栅极电压变化趋势:当开关关断时,将体端的电势拉低至栅端电压附近,加深开关关断程度,提高隔离度;当开关导通时,二极管等效为大电阻,体端电势保持为略高于0 V,使得SOI BC FET 器件的阈值电压降低,从而减小导通电阻,降低插入损耗。

图4 体电位随栅极控制电压变化

2.2 电压摆幅分布不均效应产生机理与技术改进

2.2.1 电压摆幅分布不均效应产生机理

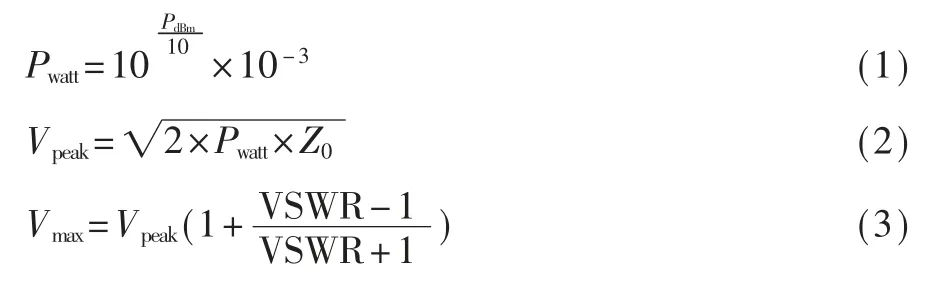

当某一支路关断时,需要承受导通支路上传输信号的交流电压。当天线工作在失配情况下,假设驻波比为VSWR,则该支路所承受的电压可由式(1)~式(3)计算得到:

对于GSM 通信所需的传输功率为35 dBm,当VSWR=6:1 时,调谐开关关断支路上承受的电压摆幅就有Vmax=31 V,可见失配情况下电压摆幅会变得特别大。整个关断支路的电压承受能力等于各级晶体管叠加,而每一级晶体管所分担的电压摆幅由各级的寄生电容[14]决定。

在所有的相关因素中,P>0.05,没有有统计学意义。结果表明:性别、年级、专业类型、每月生活费和家庭年收入这些因素均不会对大学生是否使用借贷平台产生显著影响。

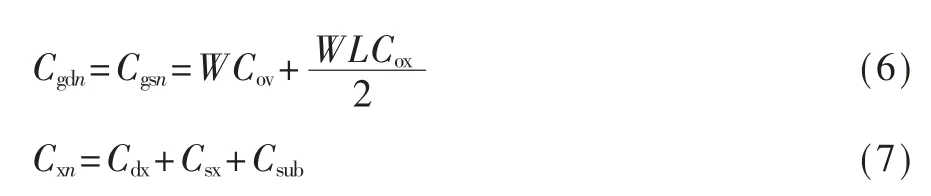

如图5 所示,当栅端控制支路关断时,等效寄生电容可计算得到:

图5 开关关断时等效电容

其中,VR为源漏极与衬底之间PN 结的反向电压,ΦB为结的内建电势,Cov为单位宽度的栅氧化层重叠电容,Cj0是下极板单位面积电容,Cox为栅-沟道单位面积电容,m一般取0.3 ~0.4,Csub为源漏极到衬底的寄生电容,Cdx和Csx分别为漏源极因其他因素产生的寄生电容。

由图3 可以看出,由于存在到衬底、体端和栅端的泄露路径,从左端流入晶体管的交流电流逐级减小,即:

由电流电压关系得:

其中:

由式(5)、(6)知:Cdbn、Csbn与VR成反比,即分别反比于Vsb、Vdb,又由式(9)可得:

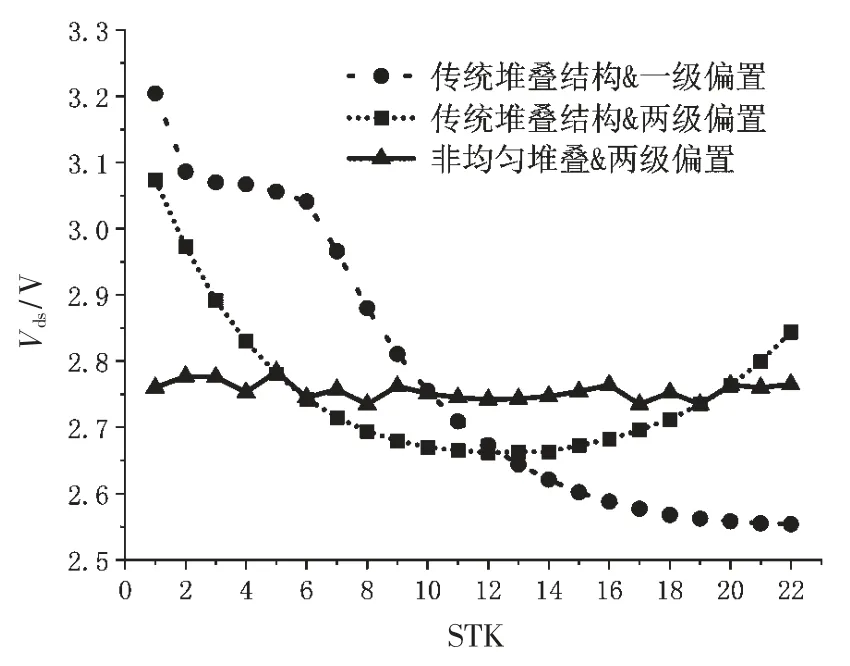

由式(10)可得,式(13)所存在的不等式会加强式(9),从而反过来作用关断电容,增大式(13)中各级电容间的差值,自此形成闭环,类似正反馈环路,从而加剧电压摆幅分布不均[14],只有第一级晶体管漏源击穿电压能够满足达到晶体管的BVDS,其他各级逐级递减,使得整个关断支路电压承受能力变小。如图6 所示,各级晶体管电压摆幅分布相差很大,从3.3 V 变化到2.5 V 不等。

2.2.2 两级偏置网络设计

图7 中,从G1点往直流偏置供压点G0看去时,由于添加了大电阻Rg2,等效输入阻抗变得很大,因此体端和栅端的泄露电流仅小部分经G1流向G0,大部分流回了管子中,使得流经各级晶体管的电流更加接近,削弱了电压分布不均的效应。

2.2.3 非均匀堆叠结构设计

设计中为确保开关的导通电阻和插入损耗满足系统要求,串联支路晶体管的尺寸往往会设置得很大,因此串联支路断开时,关断电容主要取决于栅-漏和栅-源电容,交流电压摆幅在各级晶体管上比较均匀。而并联支路为保证不影响插入损耗,晶体管尺寸较小,因此等效关断电容Coff受电压分布影响更大,并联支路分布不均现象往往更明显。

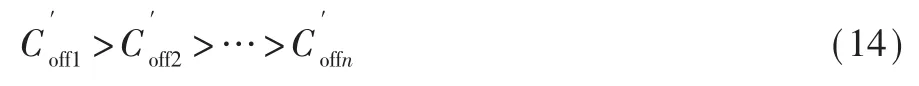

针对这种情况,本文对传统的堆叠结构进行改进,如图2 中所示,晶体管的栅宽由射频RF 端向地逐级减小,控制关断时寄生电容是逐级减小的,与流经各级晶体管的变化趋势相反,即:

图6 电压摆幅在各级晶体管上的分布

图7 改进后两级偏置网络结构

由式(10)可知,通过这种结构使得每一级晶体管上承受的电压摆幅近似相等,从而使得整个并联支路的电压处理能力达到最大。

如图8 所示,仿真设置输入功率Pin=45.563 dBm(即50 Ω 匹配情况下电压摆幅V=60 V)。对比可知,传统堆叠结构& 一级偏置网络第一级晶体管分担的电压摆幅为3.2 V,已经快达到单个FET 的BVDS;传统堆叠结构& 两级偏置电压分布不均的现象得到一定改善,电压承受能力优于前者;非均匀堆叠& 两级偏置网络通过调整各级晶体管的尺寸,使得电压摆幅实现均匀分布,此时单个晶体管分担的电压摆幅远小于BVDS,因此可以安全工作于更高功率下。

图8 三种结构的电压摆幅分布

3 整体仿真结果

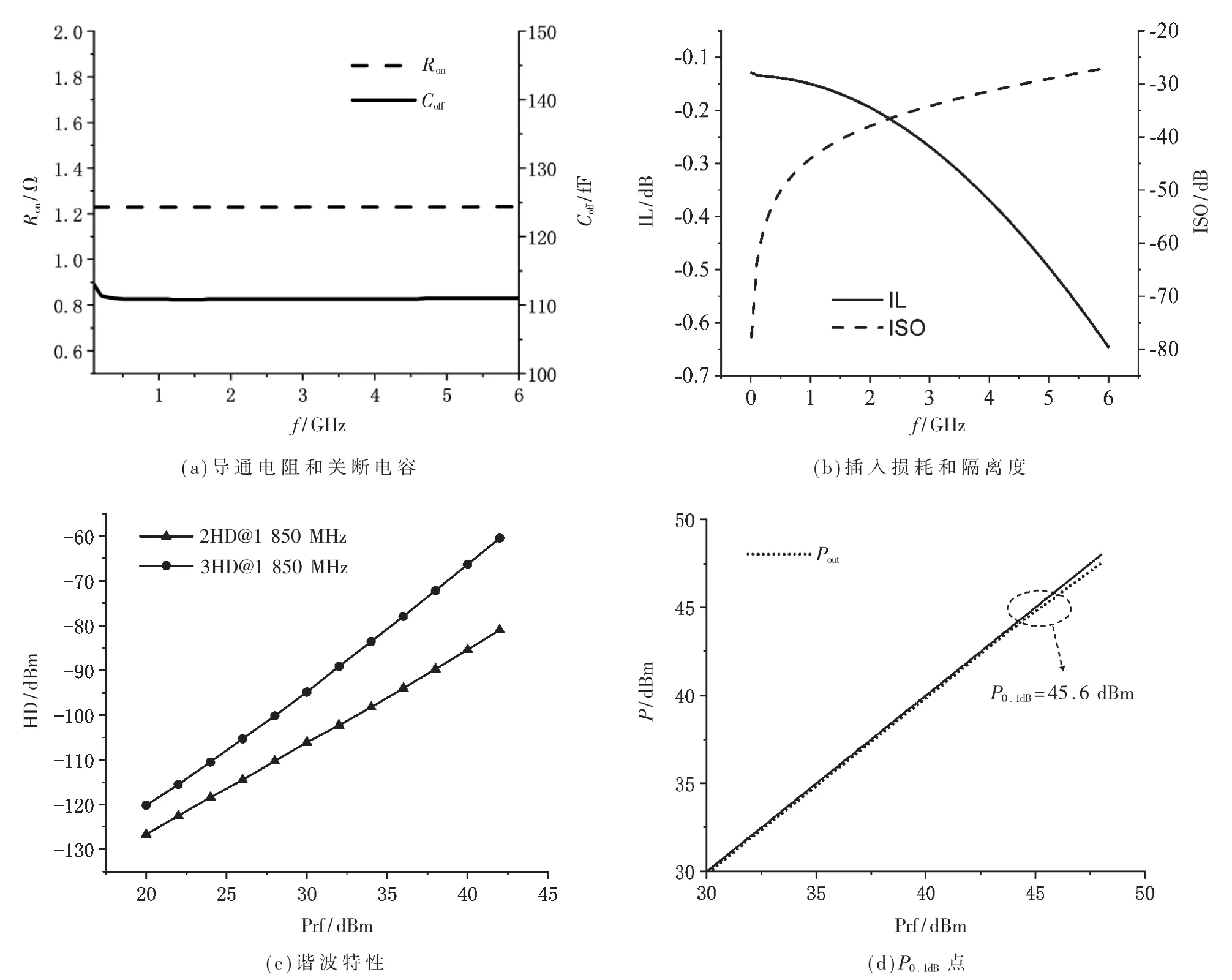

本文设计实现了一种高耐压的天线调谐开关。图9 给出了开关的小信号性能和大信号性能仿真结果,其中输出端加入电感模拟连线寄生效应。开关的导通电阻为1.24 Ω,关断电容为112 fF,带宽为0.1 GHz~5 GHz,插入损耗为0.14~0.48 dB,隔离度带内大于30 dB,P0.1dB=45.6 dBm,耐压能力大于60 V。

4 结论

基于GlobalFoundry 130 nm RF SOI CMOS 工艺,本文设计了一种高耐压的天线调谐开关,面积大约为0.7 mm×1 mm。通过非均匀设计堆叠晶体管的尺寸以及两级偏置网络,减小了体端和栅端的电流泄露,削弱了由于寄生带来的电压摆幅分布不均现象,提高了开关的电压处理能力,最终功率容量达到45.6 dBm。所设计的调谐开关在0.1 GHz~5 GHz内,实现了较小的导通电阻和关断电容,大大减小了对天线调谐的影响,并且插入损耗小于0.5 dB,隔离度大于30 dB,各项性能满足天线调谐和带通选择开关等应用的需求。本电路设计指标与近年来的参考文献对比如表1 所示。

图9 天线调谐开关的总体仿真结果

表1 本设计与其他设计性能对比