高线性度大摆幅高速PAM4光发射机驱动电路设计

2021-04-26石岱泉毛陆虹周高磊

谢 生,石岱泉,毛陆虹,周高磊

高线性度大摆幅高速PAM4光发射机驱动电路设计

谢 生1, 2,石岱泉1,毛陆虹3,周高磊3

(1. 天津大学微电子学院,天津 300072;2. 天津市成像与感知微电子技术重点实验室,天津 300072;3. 天津大学电气自动化与信息工程学院,天津 300072)

四级脉冲幅度调制;高线性度;大摆幅;SiGe BiCMOS;光发射机

随着大数据、云计算和人工智能等新技术的大幅应用,数据量呈现爆发式的增长,数据通信的带宽需求日益旺盛.目前5G已经进入到大规模商用阶段,6G通信系统的研发也在逐步推进[1-2].按照最新确立的100G/200G/400G以太网标准要求,光互连单信道的传输速率需达到50Gb/s以上.在高速光互连中,均衡技术可以对信道的非理想特性进行补偿,扩宽信道的带宽,降低码间干扰[3],然而对于50Gb/s以上的信号速率,使用均衡技术优化传统的非归零码(NRZ)调制系统显得尤为困难[4-5],为提升性能而引入更复杂的设计往往造成很大的面积和功耗浪费[6-7],所以必须寻求新的解决方法.

四级脉冲幅度调制(PAM4)采用 4个不同的信号电平来进行数据传输,每个符号周期可表示2bit的逻辑信息.因此,要实现同样比特率的信号传输能力,PAM4的信号带宽只需NRZ信号的一半[8],故而得到越来越广泛的关注.在国际高速以太网的全新调制标准中,IEEE建议在56Gb/s速率以上,所有单通道串行器/解串器(serializer/deserializer,SERDES)信道首选PAM4编码调制.因此,PAM4调制方式的发展成为未来6G通信系统以及100G/200G/400G以太网成功实现的关键[9].

近年来,PAM4发射机的理论研究已取得很多成果,但高速PAM4发射机的应用仍存在两个重要的问题:一是目前设计中的三眼线性度不高,即电平失配率(ratio of level mismatch,RLM)不够高[10-13];二是目前设计中PAM4驱动电路的输出摆幅较小[13-15],如Choudhary等[13]虽然实现了12.5Gb/s抗电磁干扰(electromagnetic interference,EMI)的PAM4发射机设计,但其RLM只有85.7%,摆幅只有0.326V.由于PAM4信号为4个电平传输数据,RLM太小可能导致接收端解调时出现误判,且摆幅较小也会降低符号间电位差值,容易引起误码,不利于后续信号的接收.目前,虽然文献[10]尝试通过源串联终端(source-series terminated,SST)设计实现摆幅和线性度的提升,然而其设计思路只适合于低压工作的CMOS工艺,对于工作电压较高的BiCMOS工艺,SST设计不易实现.

针对上述问题,本文采用带低压共源共栅电流镜的电流模式逻辑(current mode logic,CML)加法器进行信号叠加调制,保证了精准的2∶1信号叠加,实现了高线性度的PAM4信号调制.同时,设计了有源电感负载的t倍频器结构,增大带宽的同时提升了电路的输出摆幅.基于IHP 0.13μm SiGe BiCMOS工艺对所设计电路进行版图绘制和优化,设计出了一款高线性度、大摆幅的高速PAM4光发射机驱动电路.

1 电路整体结构

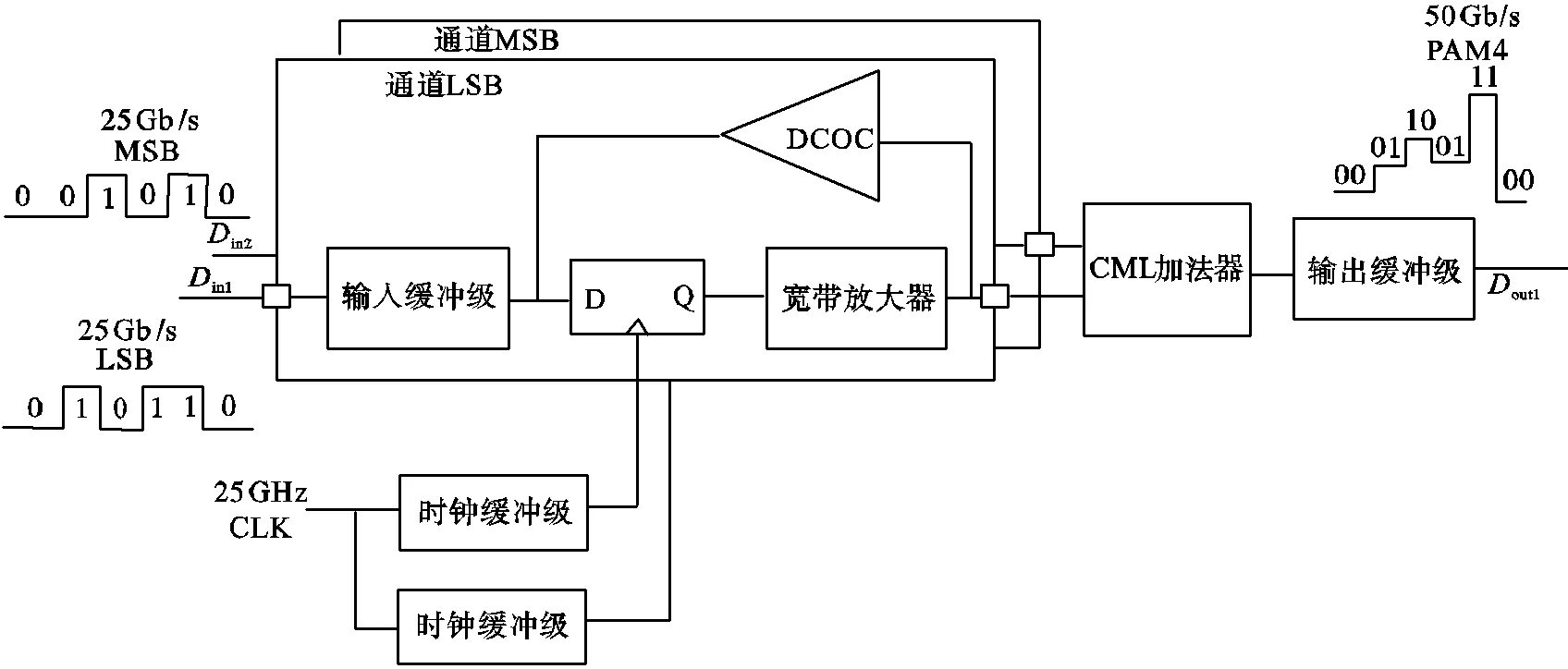

本文所设计的PAM4光发射机驱动电路整体架构如图1所示,主要包括最高有效位(most significant bit,MSB)通道和最低有效位(least significant bit,LSB)通道、时钟缓冲级、CML加法器和输出缓冲级.其中,MSB通道和LSB通道主要由输入缓冲级、D触发器、宽带放大器和直流偏移消除电路(DC offset cancellation,DCOC)构成.整体结构为两输入一输出的三端网络结构.

两路NRZ通道主要实现对输入信号的处理,输入缓冲级提供50Ω阻抗匹配以避免反射的影响.为保证输入信号的相位对齐,设计了由D触发器实现的采样电路,通过由同一时钟控制的两个D触发器对两路输入进行采样再定时,消除可能存在的相位差.宽带放大器负责对采样后的信号进行放大整形.同时引入DCOC电路稳定直流工作电平.经过NRZ通道有效处理后,输入信号方能满足叠加调制的条件.

图1 驱动电路整体结构

为实现叠加调制,本文设计了适用于高速电路的CML加法器接收两通道输出的NRZ信号,以电流模式逻辑实现两路信号的叠加调制,加法器中采用了带低压共源共栅电流镜的CML设计,保证精准的2∶1信号叠加,实现高线性度PAM4信号调制.最后经t倍频器结构的输出缓冲级,实现大摆幅PAM4信号输出.

图1展示了电路实现的PAM4调制功能,假设LSB通道数据信号输入为25Gb/s的010110NRZ信号,MSB通道数据信号输入为25Gb/s的001010NRZ信号时,输出可实现一路50Gb/s的000110011100 PAM4信号.

2 电路设计及分析

2.1 输入缓冲级

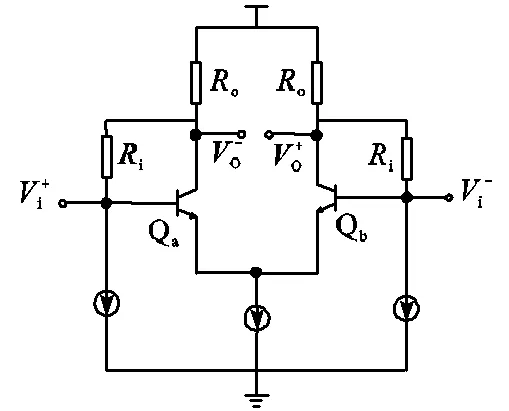

为避免高频信号反射,实现50Ω阻抗匹配,本文设计如图2所示含有自偏置的输入缓冲级.由于在输入和输出之间引入了反馈电阻i,可实现50Ω的阻抗转化.其输入阻抗in为

为避免产生较大的寄生电容,输入管Qa、Qb的结面积需设为较小的值,为提供适当增益和足够摆幅以供后续处理,o需设置足够大;由式(1)可知,在o和m受限的条件下,i需选择合理值以完成50Ω阻抗转化.

2.2 时钟缓冲级

为避免反射,本文设计的时钟缓冲级采用图2所示结构.

图2 输入缓冲级、时钟缓冲级电路

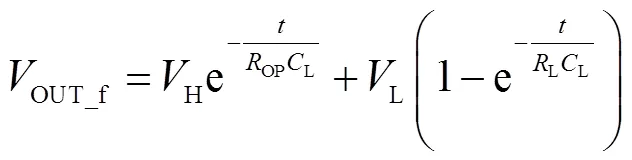

然而,对于外加高速时钟,保证时钟信号的完整性是非常重要的设计考虑因素.将时钟缓冲级电路用差分电路的等效模型进行分析,如图3所示.其中,L表示负载电阻,L表示负载电容,ON和OP分别代表差分两路的输出阻抗.由图3可知,差分输出OUT可表示为OUT=ON-OP,其上升沿OUT_r和下降沿OUT_f的电压函数可分别表示为

式中H和L分别代表OUT的高、低电平.若以逻辑电平值由10%~90%的范围定义上升时间r及下降时间f,并假定LONOP则r和f可表示为

由式(4)可知,其上升和下降时间在高低电平确定时,主要由负载电阻和电容决定.本文中25GHz的时钟周期只有40ps,对时钟信号的上升和下降时间的容限更小.如果时钟信号的上升和下降时间过大,将很大影响信号的占空比,导致时钟信号失效.

考虑到同一时钟需同时给两个主从D触发器提供时钟信号,为避免时钟同时受4个输入管电容的影响而导致时钟沿变缓,时钟缓冲级采用图1所示的并行缓冲设计,保证时钟上升和下降沿的响应速度和逻辑电平的稳定性,这是实现输入数据高精度采样的关键.图4对比了并行缓冲和单极缓冲后的时钟信号.由图4可见,采用并行缓冲后,时钟信号的质量得到明显提升,上升/下降沿响应更快,高低电平更稳定.

图4 经过时钟缓冲级的时钟信号

2.3 主从D触发器

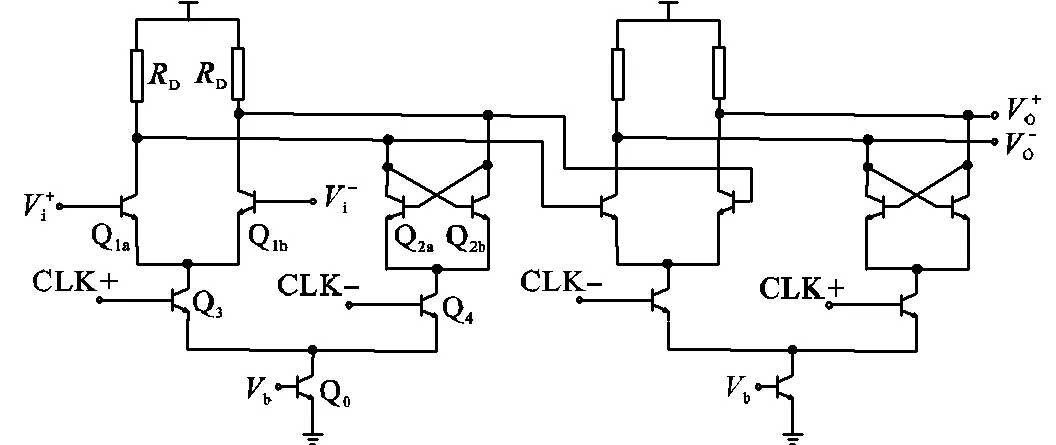

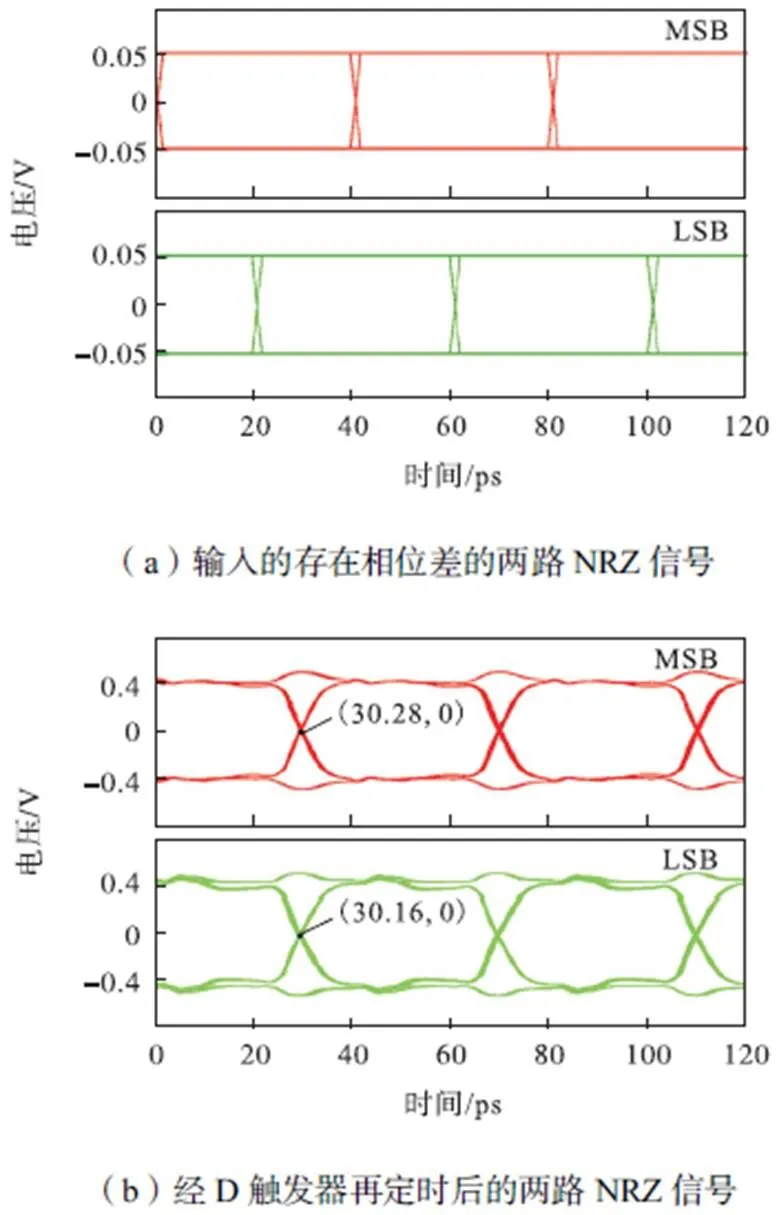

为实现PAM4调制,NRZ信号在合成前必须具有完全相同的频率、相位和幅值.由于两通道的输入为两路不同的NRZ信号,所以两路信号可能存在一定的相位差,且频率和幅值也存在细微的差异,因此必须对两路信号进行再定时.本文的再定时模块采用主从D触发器结构,如图5所示.

图5 主从D触发器电路

当存在90°相位差的两路NRZ信号(图6(a))分别输入到两个如图5所示的主从D触发器,并由相同时钟信号进行采样时,D触发器工作如下:CLK+为高电平时,Q3导通Q4截止,D触发器为采样模式工作,Q1a、Q1b开启并采样;CLK-为高电平时,Q3截止Q4导通,D触发器为保持模式工作,Q2a、Q2b开启并对信号锁存.两路NRZ信号的输出如图6(b)所示,经采样锁存后,两信号实现了与时钟信号相位同步,延时差只有约0.12ps,相当于0.54°的相位差,其对叠加调制的影响可以忽略.

图6 D触发器的再定时

2.4 宽带放大器

经D触发器采样后的信号波形引入了较大波动,且信号沿响应变慢,需引入宽带放大器对信号进行整形.本文设计的宽带放大器采用电容简并型时间连续性均衡(continuous time linear equalizer,CTLE)电路实现,如图7所示.通过引入零点,实现零极点对消,提升带宽,加快信号沿的响应速度.

图7 CTLE电路

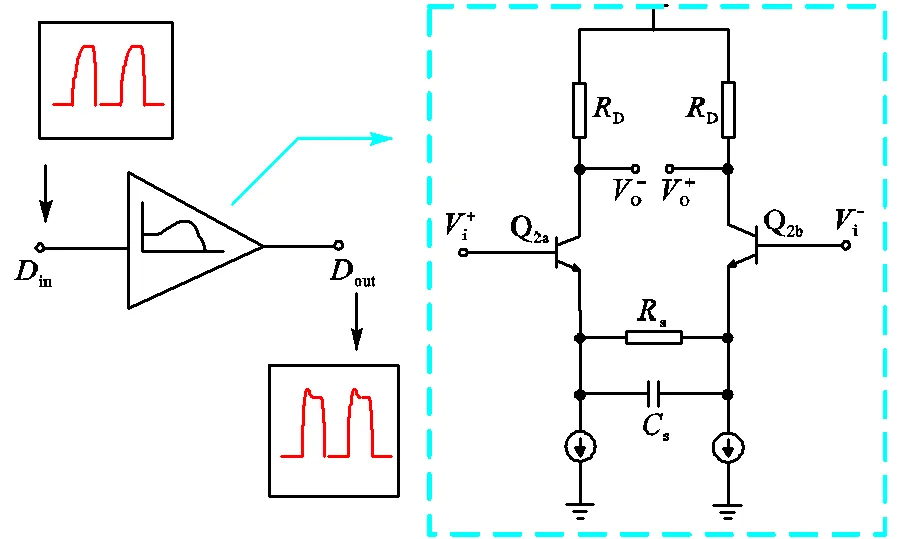

2.5 电流模式逻辑加法器

CML电路由于高速性能好、噪声影响小、电流叠加等特性,非常适用于数十Gb/s系统的设计.故本文使用CML加法器实现PAM4信号叠加调制,如图8所示.MSB和LSB电压信号通过两抽头转化为电流比2∶1的电流信号,并在输出节点直接相加,叠加的电流信号由电阻负载转化为电压信号输出.

CML加法器设计的关键在于保证输出PAM4信号的线性度.电平失配率(RLM)是评估PAM4信号线性度的标准之一.设PAM4信号的三眼的张开度分别为、、,则RLM可表示为

RLM越高,则表示眼张开度越接近平均张开度,PAM4信号的线性度越好.为保证PAM4信号的RLM,需精确保证尾电流2∶1的比例.因此本文在CML加法器中设计了如图8所示的低压共源共栅电流镜,避免了MOS管沟道长度调制效应的影响,提高了镜像精度.这一特点对需要精确2∶1电流比例的PAM4叠加调制起到十分关键的作用.

另外,由于电流信号可实现在输出节点处的直接相加,而其转化为电压信号时却不能避免阻抗变化的影响.由图8可知

式中O为两抽头的总输出阻抗,其随着加法逻辑的变化而变化.表1给出了OUT隨加法逻辑的变化.由表1可见,不同工作状态下OUT存在很大差异,这种差异影响电流-电压转换的精度.为此,本文采用共源共栅结构设计电流镜,利用其高输出阻抗(cas)的特性极大地提高了O,使之有

因此避免了由OUT变动引起的PAM4信号非线性 变化.

表1OUT随加法逻辑的变化

Tab.1 Variation of ROUT with the addition logic

综上所述,本文设计的CML加法器从提升电流镜像精度和稳定输出阻抗两方面考虑,避免出现非线性因素,优化了PAM4信号线性度.图9展示了经CML加法器叠加后的PAM4信号眼图,实现了RLM为99.7%的PAM4输出.

图9 CML加法器实现的高线性度眼图

2.6 输出缓冲级

经CML叠加后的PAM4信号并不能直接输出,需输出缓冲级进行阻抗匹配,以免输出反射劣化信号.输出级的设计需兼顾大带宽和大摆幅.

本文设计了如图10所示的输出缓冲级,其基础结构为t倍频器.由于引入额外的偏置管对,使输入电容降为π/2,倍增了由前级负载电阻和输入管电容形成的低频极点,从而提升了电路带宽.另外,电路负载采用有源电感,进一步提升带宽.

由于传统输出缓冲级中50Ω的匹配电阻和较小的尾电流,其输出摆幅受限.图10所示的结构引入的额外偏置管对Q6抽取负载电流,拉低了输出节点的电位,故可实现更大的摆幅.

3 仿真结果

图13展示了两路100mV的25Gb/s NRZ信号输入时,两个NRZ通道的输出眼图和调制后的PAM4信号输出眼图.由图13(a)和(b)可见,两路NRZ通道的输出眼图清晰,眼图上升和下降时间小于0.25个单位时间,抖动影响很小,实现了很好的眼宽;交叉点几乎位于0V处,说明直流偏移消除电路的作用明显;眼图摆幅约为0.8V,张开度很大,实现了较大的噪声容限;眼图显示有部分过冲,这是因为两通道设计时存在部分带宽余量,以保证后接加法器仍保持足够带宽.由图13(c)可见,PAM4信号输出眼图可清晰分辨3个眼,整体摆幅接近1.5V.虽然寄生参数对眼皮厚度略有影响,整体而言三眼的线性度仍十分优异,三眼从上到下开合程度分别为376mV、366mV、371mV,RLM达98.6%.

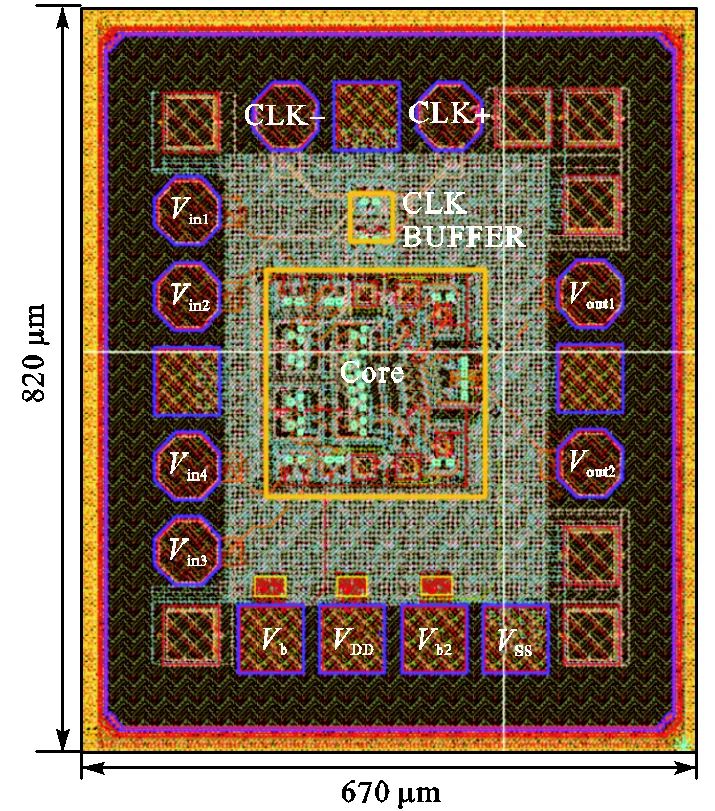

图11 电路结构版图

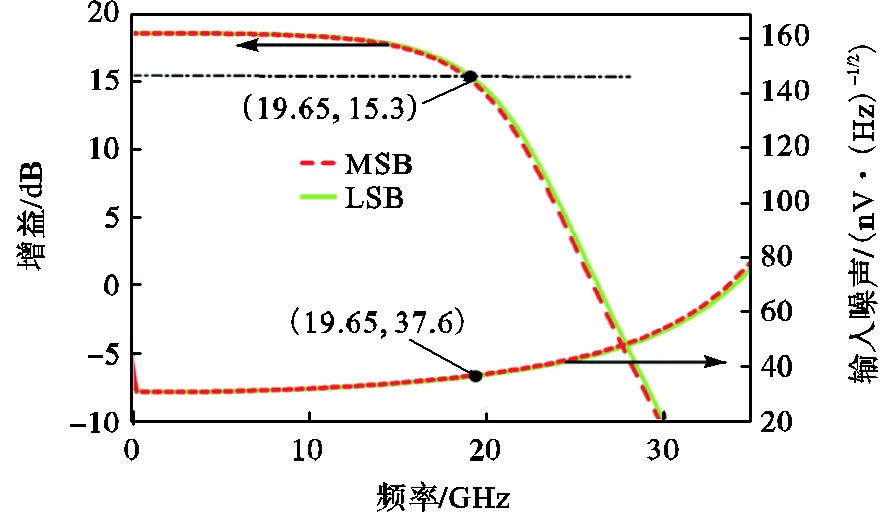

图12 通道MSB和LSB的幅频特性和等效输入噪声电压

图13 眼图

表2给出了本文设计电路的性能参数,并与已报道的其他BiCMOS PAM4光发射机驱动电路[13]进行了比较.由表2可见,本文设计的PAM4光发射机驱动电路在摆幅和线性度方面具有很大优势.

表2 BiCMOSPAM4光发射机的性能对比

Tab.2 Performance comparison of the BiCMOS PAM4 optical transmitter

4 结 语

[1] Liu D,Hong W,Rappaport T S,et al. What will 5G antennas and propagation be? [J]. IEEE Transactions on Antennas and Propagation,2017,65(12):6205-6212.

[2] Keogh B,Zhu A. Wideband self-interference cancellation for 5G full-duplex radio using a near-field sensor array[C]// 2018 IEEE MTT-S International Microwave Workshop Series on 5G Hardware and System Technologies(IMWS-5G). Dublin,Ireland,2018:1-3.

[3] Belfiore G,Szilagyi L,Henker R,et al. 25 Gbit/s adaptive 3-tap FFE VCSEL driver in 28-nm CMOS for data center communications[C]//2017 19th International Conference on Transparent Optical Networks(ICTON). Girona,Spain,2017:1-4.

[4] Kerrebrouck J V,Keulenaer T D,Pierco R,et al. High-speed electrical interconnects:NRZ,duobinary or PAM4? [J]. IEEE Microwave Magazine,2019,20(7):24-35.

[5] Sakamoto T,Mori T,Wada M,et al. Strongly-coupled multi-core fiber and its optical characteristics for MIMO transmission systems[J]. Optical Fiber Technology,2016,35(2):8-18.

[6] Belfiore G,Khafaji M,Henker R,et al. A 50 Gb/s 190 mW asymmetric 3-tap FFE VCSEL driver[J]. IEEE Journal of Solid State Circuits,2017,52(9):2422-2429.

[7] Peng P,Lai S,Wang W,et al. A 100Gb/s NRZ transmitter with 8-Tap FFE using a 7b DAC in 40nm CMOS[C]//2020 IEEE International Solid-State Circuits Conference(ISSCC). San Francisco,CA,USA,2020:130-132.

[8] Qi N,Kang Y,Lin Q,et al. A 51Gb/s,320mW,PAM4 CDR with baud-rate sampling for high-speed optical interconnects[C]//2017 IEEE Asian Solid-State Circuits Conference(A-SSCC). Seoul,South Korea,2017:89-92.

[9] IEEE.P802.3bs/D3.5 IEEE Draft Standard for Ethernet Amendment 10:Media Access Control Parameters,Physical Layers and Management Parameters for 200 Gb/s and 400 Gb/s Operation[S]. New York,USA:IEEE,2017.

[10] Wang D,Chen H,Luan W,et al. A 4—40 Gb/s PAM-4 transmitter with a hybrid driver in 65 nm CMOS technology[C]//2019 IEEE 62nd International Midwest Symposium on Circuits and Systems(MWSCAS). Dallas,USA,2019:251-254.

[11] Liao Q,Qi N,Li M,et al. A 50-Gb/s PAM4 Si-photonic transmitter with digital-assisted distributed driver and integrated CDR in 40-nm CMOS[J]. IEEE Journal of Solid-State Circuits,2020,55(5):1282-1296.

[12] Verbist J,Lambrecht J,Verplaetse M,et al. Real-time and DSP-free 128 Gb/s PAM-4 link using a binary driven silicon photonic transmitter[J]. Journal of Lightwave Technology,2019,37(2):274-280.

[13] Choudhary M S,Pudi N S A K,Redoute J M,et al. An EMI immune PAM4 transmitter in 130 nm BiCMOS technology[C]//2019 IEEE MTT-S International Microwave and RF Conference(IMARC). Mumbai,India,2019:1-4.

[14] Lim B,Kim D,Yoo C. Voltage-mode PAM4 driver with differential ternary R-2R DAC architecture[J]. Electronics Letters,2020,56(9):431-432.

[15] Hyun C,Ko H,Chae J H,et al. A 20Gb/s dual-mode PAM4/NRZ single-ended transmitter with RLM compensation[C]// 2019 IEEE International Symposium on Circuits and Systems(ISCAS). Sapporo,Japan,2019:1-4.

Design of High-Speed Four-Level Pulse Amplitude Modulation Optical Transmitter Driving Circuit with High Linearity and Large Swing

Xie Sheng1, 2,Shi Daiquan1,Mao Luhong3,Zhou Gaolei3

(1. School of Microelectronics,Tianjin University,Tianjin 300072,China;2. Tianjin Key Laboratory of Imaging and Sensing Microelectronic Technology,Tianjin 300072,China;3. School of Electrical and Information Engineering,Tianjin University,Tianjin 300072,China)

four-level pulse amplitude modulation;high linearity;large swing;SiGe BiCMOS;optical transmitter

TN433

A

0493-2137(2021)08-0861-07

10.11784/tdxbz202009069

2020-09-24;

2020-11-03.

谢 生(1978— ),男,博士,副教授,xie_sheng06@tju.edu.cn.

石岱泉,shidaiquan.qingxie@foxmail.com.

国家重点研发计划资助项目(2018YFE0202500).

Supported by the National Key Research and Development Program of China(No. 2018YFE0202500).

(责任编辑:孙立华)