基于异构忆阻器的1T2M多值存储交叉阵列设计

2021-04-11孙晶茹李梦圆康可欣邾少鹏SunYichuang

孙晶茹 李梦圆 康可欣 邾少鹏 SunYichuang

①(湖南大学信息科学与工程学院 长沙 410082)

②(北京邮电大学电子工程学院 北京 100089)

③(英国赫特福德大学物理工程与计算机科学学院 哈特菲尔德 英国 AL10 9AB)

1 引言

随着5G、人工智能、大数据、物联网等技术的迅猛发展,传统的存储技术已无法满足数据指数级增长的存储要求,人们希望可以获得尺寸更小、读写速度更快、稳定性更好的存储技术来满足海量数据存储要求[1]。

忆阻器于1971年由蔡少棠教授提出,直到2008年HP实验室才发现了首个纳米级忆阻器器件,忆阻器具有尺寸小、读写速度快、功耗低和易于与CMOS技术兼容等特性,一经诞生就引起广泛关注,围绕忆阻器的研究从器件实现[2—4]、忆阻器电路模型[5]和忆阻器数学模型[6]等多方面展开,另外忆阻器在逻辑电路[7—10]、混沌电路[11—14]、神经形态网络[15—17]等领域得到广泛应用[18],特别在存储器的设计中,忆阻器的小尺寸和非易失性,使其成为最具前景的非易失性存储器技术。

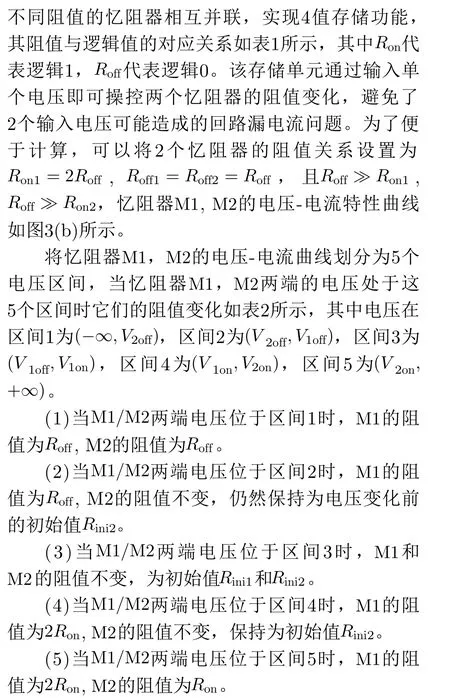

最初基于忆阻器的存储交叉阵列研究试图利用忆阻器的阻变特性,实现多值存储[19—21],但是忆阻器阻值变化速度快,准确地设定忆阻器阻值较为困难,并且阻值极易受到读写电流及外界因素影响,产生阻值漂移,影响存储器的稳定性。研究表明,忆阻器具有电压阈值特性,即当外加电压超过忆阻器阈值电压时,忆阻器会发生 Ron和Roff之间的阻值突变,而当外加电压小于阈值电压时,忆阻器阻值基本保持不变[22,23]。忆阻器的这一特性,使其更适用于需要稳定状态的逻辑电路及存储器电路设计,如文献[24]提出了一种具有稳定特性的存储单元,但该单元结构由6T1M构成,结构复杂,存储密度较低。忆阻器的双向性,造成阵列结构中存在严重的漏电流问题,如图1(a)所示,其中T表示控制忆阻器开关的MOS管,B为位线,W为字线。文献[20,25]提出了1T1M存储单元结构,用MOS管作为开关使存储单元单向化,1T1M结构由于其稳定性和较高的存储密度得到广泛应用。为增加存储密度,文献[26]提出了1T2M 4值存储阵列,但是该结构需要精确地控制脉冲电压宽带来设定忆阻器的4个阻态,增加了电路复杂度,另外串行的读取方式导致读速度较慢。文献[27]对1T2M结构进行了改进,每个忆阻器具有2个阻态,降低了对电压精度的要求,并行的读取方式提高了读速度,但该结构需要2个WL电压信号分别控制2个忆阻器的读写操作,这不仅增加了交叉阵列结构的复杂度,还会形成新的漏电流问题,如图1(b)所示,与选择单元在同一行的非选择单元,会在2个忆阻器之间形成通路,导致新的漏电流产生。

图1 交叉阵列中的漏电流问题

基于以上分析,本文提出一种新型1T2M存储结构,该结构由2个具有不同阈值电压及Ron阻值的忆阻器和1个MOS管构成,1个WL电压信号即可完成2个忆阻器的读写操作,不仅简化了交叉阵列结构,也避免了新通过的漏电流问题的产生,具有较高的读写速度及存储密度。本文结构安排如下:第2节介绍忆阻器模型。第3节介绍所设计的1T2M存储器单元电路及交叉阵列结构,并进行读写电路原理分析。第4节采用PSpice对所提出的1T2M交叉阵列存储结构进行电路仿真,并与其他的忆阻存储器进行比较分析。第5节总结全文。

2 忆阻器模型

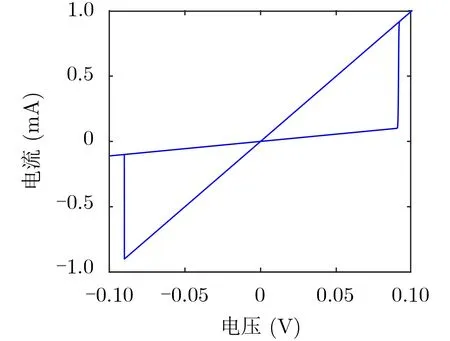

在惠普忆阻器模型之后,研究人员采用不同材料实现了多种具有不同特性的忆阻器件,为了更好地拟合不同忆阻器件,也产生了多种不同的忆阻器模型,如线性离子漂移模型[28]、非线性离子漂移模型[29]、阈值自适应忆阻模型[22]和通用电压控制忆阻器模型(Voltage ThrEshold Adaptive Memristor,VTEAM)[23]等。其中,文献[23]提出的VTEAM模型利用阈值电压控制忆阻器在高阻态和低阻态之间的转换,较好地体现了忆阻器二值特性。相较于其他模型,VTEAM结构简单、通用性强,能够更好地拟合不同忆阻器件,在忆阻存储和逻辑电路的设计中得到广泛应用。VTEAM模型的电流电压特性可定义为

图2 忆阻器模型迟滞回线

3 1T2M交叉阵列多值存储器

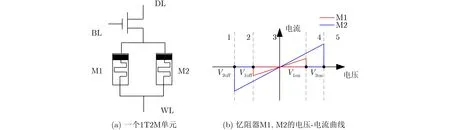

3.1 1T2M单元电路结构

在这5个电压区间下,可以实现对两个忆阻器阻值状态的同时改变。

将本文所设计的1T2M单元放置在交叉阵列中,所设计的多值存储交叉阵列如图4所示。

3.2 写操作

RonRoff1T2M中的每个忆阻器可被编程为和2个阻态,1个存储单元可表示4组不同的逻辑值,如表1所示。

图3 1T2M存储单元

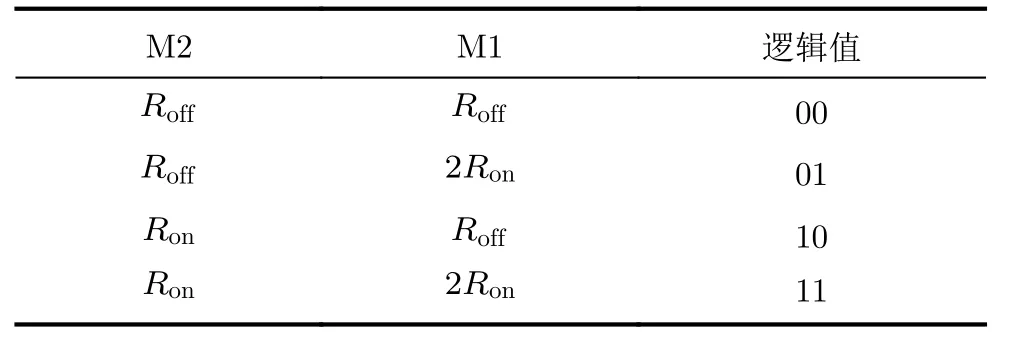

表1 忆阻器M1, M2的电阻值和逻辑值的关系

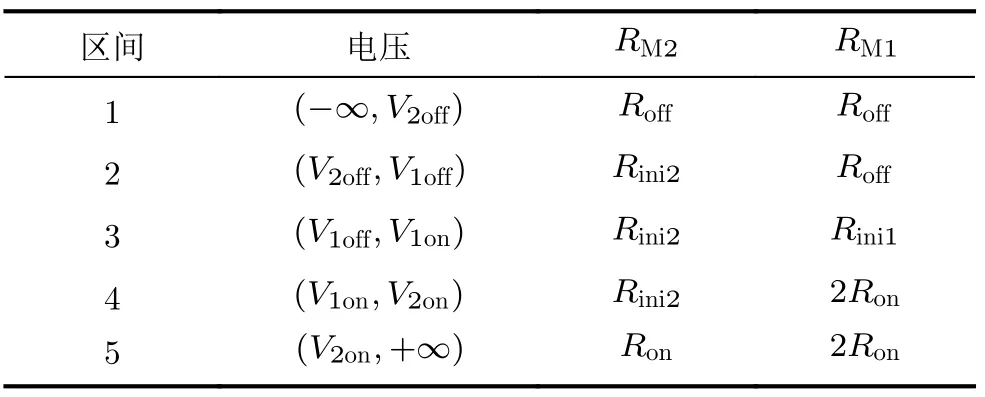

表2 忆阻器M1, M2的电阻值与电压区间的关系

为将数据正确地写入1T2M单元,应向相应的行线和列线施加不同区间的电压,读取线接地。根据表2,具体步骤如下:

(1)写入逻辑值“00”:输入位于区间1的写入电压(—1 V),此时,2个忆阻器均呈现Roff状态,写入了逻辑值“00”。

(2)写入逻辑值“11”:输入位于区间5的写入电压(1 V),此时,2个忆阻器均呈现Ron状态,写入逻辑值“11”。

与“00”和“11”的一步写入不同,“01”与“10”的写入均需两步才能完成。

(3)写入逻辑值“01”:首先,输入位于区间1的写入电压(—1 V),使2个忆阻器均呈现Roff状态;然后,输入位于区间4的写入电压(0.7 V),此时, M1转换为Ron状态。同时,由于输入未达到M2的阈值电压, M2仍维持Roff状态,完成逻辑值“01”的写入。

(4)写入逻辑值“10”:首先,输入位于区间5的写入电压(1 V),使2个忆阻器均呈现 Ron状态;然后,输入位于区间2的写入电压(—0.7 V),此时, M1转换为Roff状态。同时,由于输入电压未达到 M2的阈值电压, M2仍维持Ron状态,完成逻辑值“10”的写入。

通过步骤(1)—步骤(4)的操作,可以实现4个状态的写入。

3.3 读操作

在读数据时,为保证存储信息不被改变,应将读取电压设置在区间3,此时读取电压小于2个忆阻器的阈值电压,可保证忆阻器的阻值不被改变。

读操作开始时,通过BL和WL选择指定单元,施加BL电压打开相应列的MOS管开关,施加WL读取电压选择行。通过DL获得输出电流。通过测量输出电流,获得1T2M存储单元的存储数据。

图4 本文所提1T2M多值存储交叉阵列

至此,通过施加读取电压并测量读取电流,实现2 bit数据的读取。

在本文所提出的交叉阵列中,同列单元可以同时写入,同行单元可以进行并行读取。

4 仿真与比较

本节采用PSpice对所提出的存储器进行电路仿真。

4.1 存储单元仿真

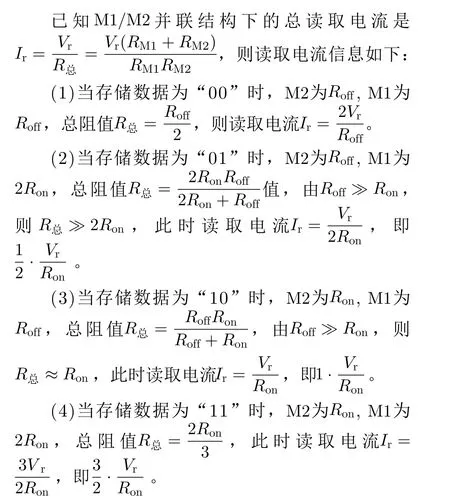

本文所使用的忆阻器采用了VTEAM模型,模型参数如表3所示。

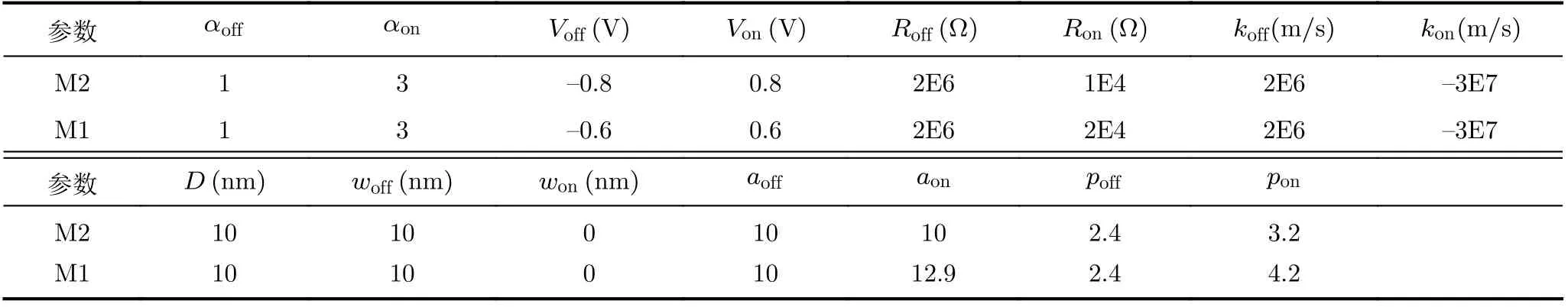

通过对单个忆阻器及存储单元进行仿真,其电压电流特性曲线如图5所示,图5(a)为忆阻器电压电流曲线,图5(b)为存储单元电压电流曲线。

表3 忆阻器参数设置

图5 存储单元仿真

4.2 写仿真

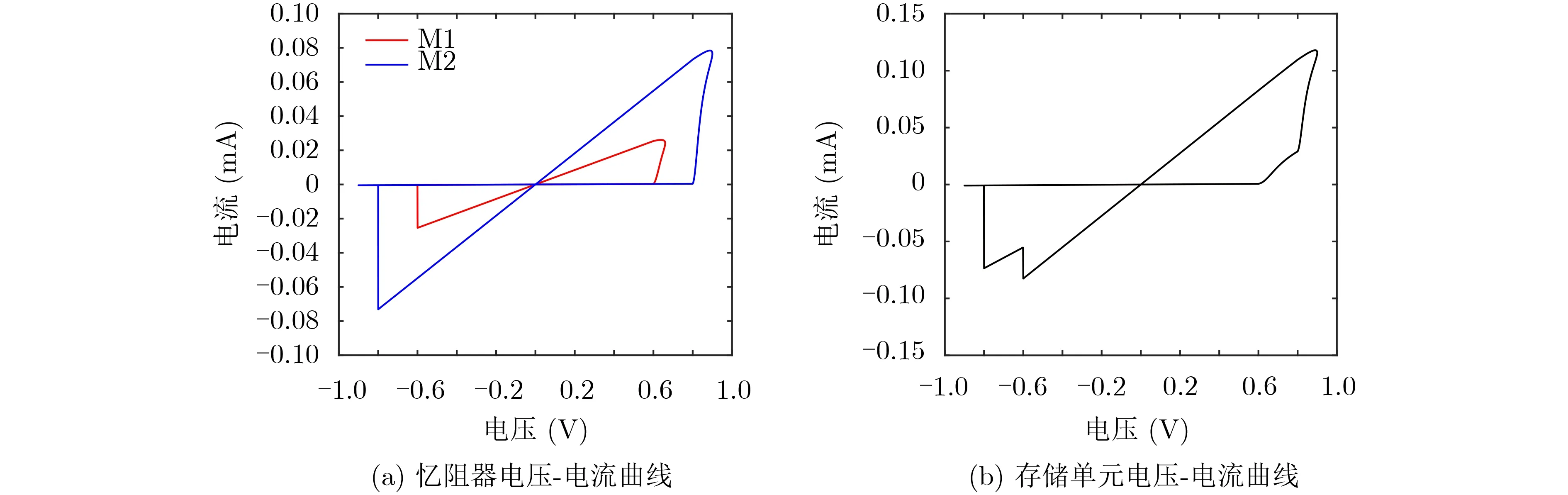

(1)11-00写仿真

为实现11-00的写入,输入位于区间1的写入电压,则可观察到 M1与 M2均由Ron转换到Roff状态,如图6(a)、图6(b)所示。

(2)00-10写仿真

为实现00-10的写入,先后输入位于区间5(1 V)和区间2(—0.7 V)的写入电压,如图6(c),输入第1个写入电压后, M1和 M2均由Roff转换为Ron状态,在第2个写入电压输入后, M2转换到Roff状态,如图6(d),完成10的写入。

(3)与之类似,4个状态的连续写入仿真结果如图6(e)和图6(f)。

图6 写操作仿真结果

4.3 读仿真

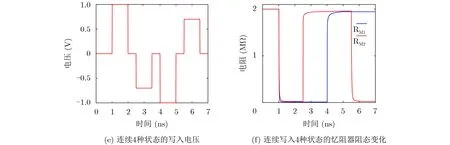

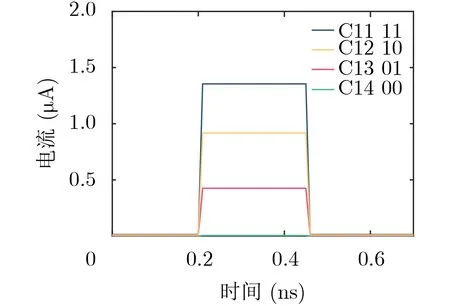

在构建的4×4阵列中,鉴于可以实现同一行存储单元的同时读取,对单元C11, C22, C33, C44分别写入4种状态值,进行了并行读取。得出了成比例的输出电流如图7所示,读操作的时间延迟由图8可知,当读电压为0.01 V时,读操作的延迟约为0.01 ns。

图7 不同单元的读电流

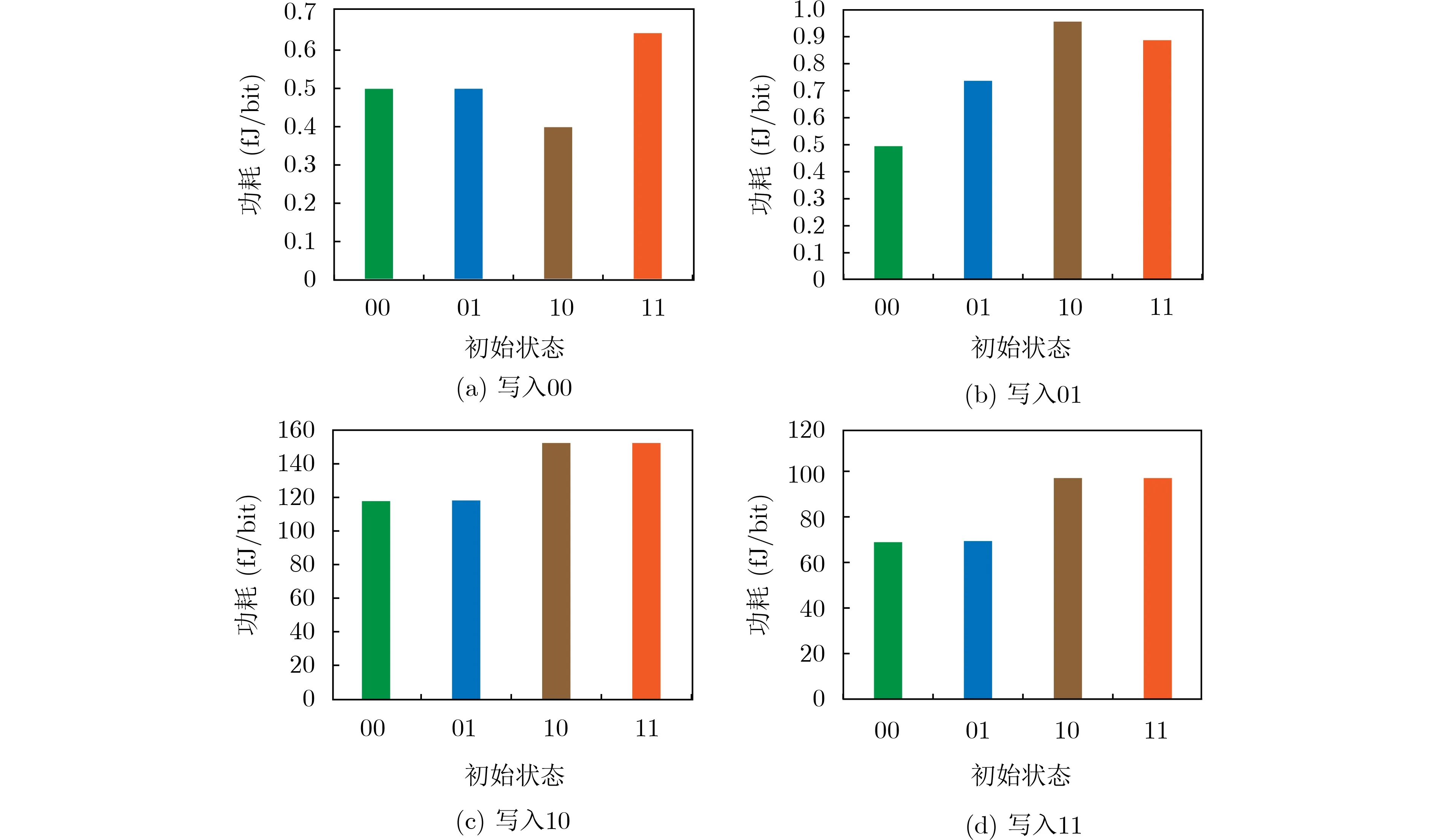

4.4 功耗

通过对4种不同的初始状态分别写入00, 01, 10,11 4种逻辑,对共16种写入情况的动态功耗进行仿真,得到仿真结果如图9所示,由于不同的初始状态的写入步骤和写入电压不同,会对功耗造成影响。同理,写入不同逻辑时,功耗也会有很大的差异。

图8 读电流时间延迟

图9 不同初始状态下写操作功耗

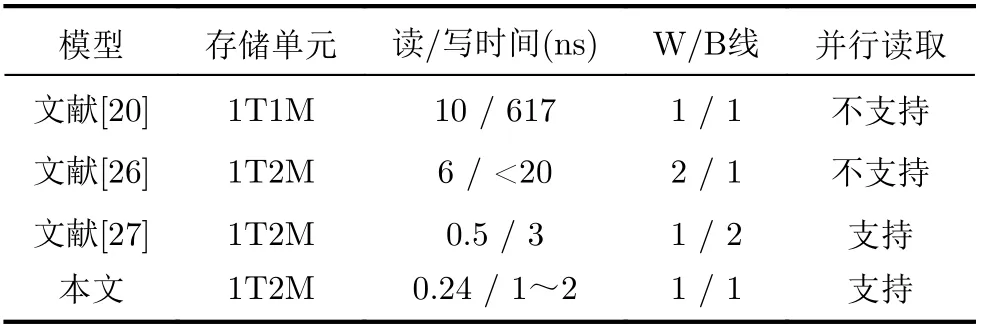

4.5 比较

本文与已有工作进行了比较,如表4所示,本文所提出的4值存储交叉阵列,可实现同行的并行读取,结构更简单,读写速度更快,并通过单W/B线阵列,有效避免了新的漏电流问题。

表4 不同存储模型的比较

5 结束语

本文分析了已有多值存储交叉阵列,特别是1T2M结构存在的问题,提出了一种基于异构忆阻器的1T2M多值存储阵列结构。该结构采用具有不同阈值电压和 Ron阻值的两个异构忆阻器并联实现4值存储功能,并通过一条字线WL和一条位线BL完成读写操作。PSpice仿真验证表明,与已有忆阻存储交叉阵列结构相比所提出的阵列有效降低了漏电流、结构更简单、读写速度更快。

在未来的研究中,我们将进一步利用异构忆阻器实现多值存储的特性,设计实现具有更高存储密度的存储阵列,并探索基于多值存储的存算一体架构实现方法。