一种基于查找表的移位寄存器链的设计

2021-03-29王德龙张艳飞

刘 彤,王德龙,张艳飞,蒋 婷

(无锡中微亿芯有限公司,江苏无锡 214072)

1 引言

现场可编程门阵列(FPGA)是一种半定制电路,具有开发周期短、成本低、风险小、集成度高、灵活性强,且便于电子系统维护和升级的特点,因此成为了数字芯片的主流,被广泛应用在通信、控制、视频、信息处理、消费电子、互联网、汽车以及航空航天等诸多领域[1-2]。

可编程逻辑单元是FPGA 最基本和最核心的模块,基于查找表的可编程逻辑单元是实现时序电路和组合电路的主要逻辑资源,其中移位寄存器是查找表逻辑应用中最重要的功能之一,通过移位寄存器产生需要的延时或延时补偿,用来平衡数据流水线的时序,同样移位寄存器可用于同步先进先出(FIFO)以及内容可寻址存储器的实现[3],同时还可以用于数的加、减、乘、除运算,用于数字匹配滤波器的实现[4],以及串并数据转换,构成可变分频器和高效随机数发生器的实现[5-6]等。可编程逻辑单元的移位寄存器链的应用非常广泛,因此研究一款灵活的移位寄存器架构具有重要意义,本文提出了一种基于查找表的移位寄存器链的架构设计。

2 原理

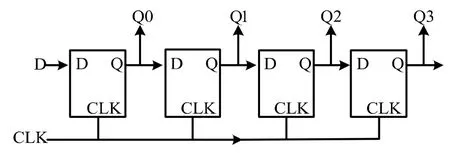

目前市场主流的移位寄存器链由触发器(DFF)级联实现,如图1 所示,由4 级DFF 首尾级联,完成4 个时钟周期的移位操作。由于触发器数量有限,面积较大,位数满足不了用户的设计要求,因此需要设计宽位数有效的移位寄存器链。

本文的目的是研究可编程逻辑单元移位功能架构的实现方式和电路设计,提出了一种基于查找表的移位寄存器链架构,通过电路设计、布局、仿真和优化,并进行了流片和测试,从而验证该架构在28 nm 工艺下的功能和性能可行性,市场主流芯片对比参考频率为450 MHz,电路设计目标频率为500 MHz,从而实现一款灵活的可编程逻辑单元的设计,打通28 nm 工艺下FPGA 的设计流程。该架构以查找表的配置存储单元作为移位基本模块,通过对时钟和写使能的控制,两个存储单元作为一个周期移位基本单元,对查找表的存储资源进行重复利用,有效地实现了宽时钟周期的移位功能。

图1 DFF 级联移位寄存器

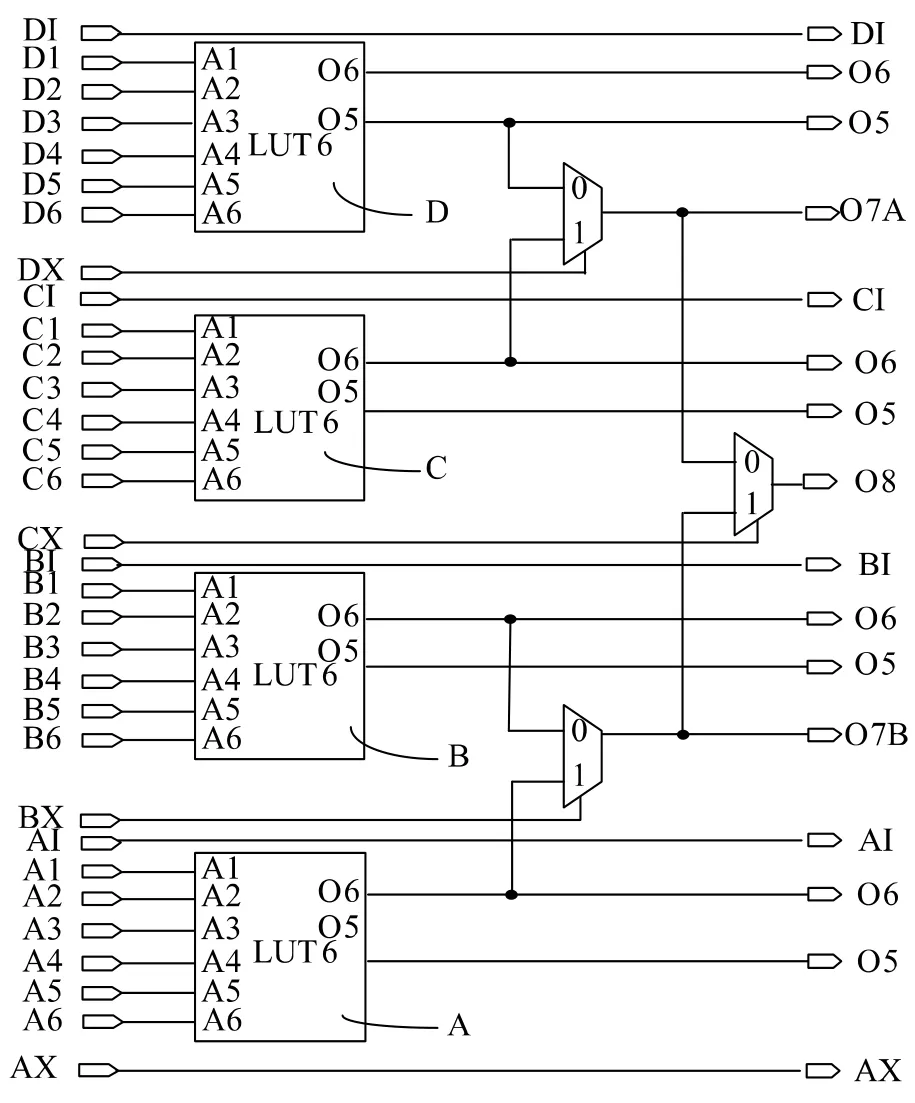

查找表的基本原理是采用二选一的复用器组成的一种树形结构,查找表树形结构的最后一级是单个二选一的复用器,前面每一级复用器的数量依次递增,都是后一级的两倍,第一级选择器(MUX)用于接收静态存储单元(SRAM)中的值,实现1 个n 输入的查找表需要2n 个SRAM 存储单元[7-8]。1 个可编程逻辑模块,包含4 个六输入的查找表逻辑单元,如图2 所示,包含 A、B、C、D 4 个查找表区域,每个查找表实现方式为64 个配置存储单元和6 个输入地址信号,通过对存储单元的配置,实现6 信号输入任意函数表达式的功能。

图2 查找表逻辑单元

基于查找表移位寄存器链的基本结构如图3 所示,包括一个移位时钟使能模块(1),一个时钟使能区域控制模块(2),存储单元(3)和一个输入控制模块二输入选择器(4)。基于可编程存储单元的移位寄存器结构包含(A)、(B)、(C)、(D)4 个存储单元区域,存储区域(D)的初始输入信号为SI_D,第1 个存储单元的使能控制信号为WEN_D,第1 个存储单元的输出端口接入到第2 个存储单元的输入端,第2 个存储单元的使能控制信号为WE_D,在进行移位操作时,WEN_D 与 WE_D 始终保持不重叠逻辑 1,即当WEN_D=1,第1 个存储单元写入信号SI_D,此时WE_D=0,第 2 个存储单元处于保持状态;当WEN_D=0,第1 个存储单元处于保持状态,不能写入数据,此时WE_D=1,第2 个存储单元把第1 个存储单元的值写入至第2 个存储单元。当CLK=0 时,WEN_D=1,当 CLK=1 时,WE_D=1,因此 2 个存储单元作为1 组,可以完成1 个时钟周期的移位操作。1 个存储区域共包含64 个存储单元,以此类推第1 个、第3 个、第5 个、……、第63 个存储单元的移位使能信号为 WEN_D,第 2 个、第 4 个、第 6 个、……、第 64 个存储单元的移位使能信号为WE_D。

图3 移位寄存器结构

一个存储区域最大可以构成1 个32 个时钟周期的移位操作,同理存储区域(C)、(B)和(A)均可以构成1 个32 个时钟周期的移位操作。存储区域(C)、(B)和(A)的初始输入信号由二输入选择器(4)进行控制。当选择器(MUX)(4)选择输入端口1 信号输入时,则存储区域(D)、(C)、(B)和(A)的输入初始值分别为SI_D、SI_C、SI_B 和 SI_A,4 个存储区域构成了 4 个独立的最大能实现32 个时钟周期的移位操作。当(D)和(C)存储区域之间的MUX(4)选择输入端口2 信号输入时,则存储区域(C)的初始值为 D<64>,(D)和(C)存储区域级联成一个最大能实现64 位时钟周期的移位操作,同理(D)、(C)、(B)和(A)的输入初始值分别选择 D<64>、C<64> 和 B<64>,4 个存储区域构成了首尾级联,最大实现一个128 个时钟周期的移位操作,输入初始值为SI_D,因此所述基于可编程存储单元的移位寄存器结构的存储单元能实现0~128 位时钟周期内任意整数个时钟周期的移位操作。MUX(4)的选择控制信号为静态SRAM 值,由用户进行配置。当存储区域(D)的MUX(4)选择级联进位信号DIN 输入时,级联成更大时钟周期的移位操作。

移位时钟使能模块(2)如图4 所示,其输入信号为时钟信号CLK,移位使能信号GWE,移位使能控制信号Q_SHIFT,输出信号为Y 和YN。Q_SHIFT 为静态存储单元控制,Q_SHIFT=1,代表选通模块的移位功能操作。GWE 为写使能信号,高电平时执行写信号操作。CLK 为时钟,2 个二输入或非门和5 个反相器用于产生不交叠高电平使能信号Y 和YN,用于完成移位寄存器链的移位操作[9]。

图4 移位时钟使能模块结构

每个时钟使能区域控制模块的Q_SHIFT 相互独立,分别为 Q_SHIFT_D、Q_SHIFT_C、Q_SHIFT_B、Q_SHIFT_A,用于单独控制该区域是否执行移位操作,因此对应的使能输出信号分别为WE_D、WEN_D、WE_C、WEN_C、WE_B、WEN_B、WE_A、WEN_A。

移位寄存器结构的存储单元(3)的具体结构如图5 所示,包含1 个六管静态存储单元结构,存储单元的写信号为SI,EN 为写使能信号,静态存储单元具有双稳态结构,具有写0 容易写1 难的特点,因此当SI 为0 时,通过一个NMOS 管从Z 端直接写入,当SI 为1时,通过 3 个 NMOS 管从 Z 和 ZN 双端写入,并存储在SRAM 中,存储单元的输出端口为ZO。

图5 移位单元结构

移位寄存器的输出如图6 所示,移位输出端口SR1~32,输出端口通过查找表的输入信号A1、A2、A3、A4、A5、A6 作为移位选择输出,选择输出 1~32 任意周期的移位操作。

3 仿真验证

对图3 中的结构进行仿真,选择28 nm UMCHPC+工艺,电源电压为1 V,选择典型工艺角,温度25 ℃,对电路进行配置,配置成4 个独立的32 位移位寄存器,输入信号分别为 DI、CI、BI、AI,输入时钟CLK 为500 MHz,令4 个输入信号频率或相位不同,输出分别为 D、C、B、A,Hspice 仿真结果如图 7 所示,表明输出之间相互独立,输出与输入均相差32 个时钟周期。

图6 移位输出结构

图7 配置成4 个独立32 位移位寄存器的仿真波形

选择典型工艺角,温度25 ℃,对电路进行配置,进行 D、C、B、A 首尾级联,配置成 1 个 128 位移位寄存器,输入信号为DI,输入时钟CLK 为500 MHz,输出分别为 D、C、B、A,Hspice 仿真结果如图 8 所示,其中D 输出与 DI 相差 32 个时钟周期,C 输出与 DI 相差64 个时钟周期,B 输出与DI 相差96 个时钟周期,A输出与DI 相差128 个时钟周期,完成了128 个周期移位操作。

4 测试结果

图8 配置成128 位移位寄存器的仿真波形

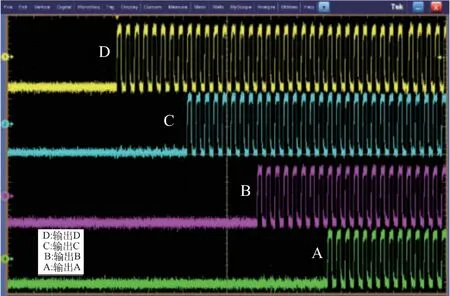

采用28 nm UMC HPC+ 工艺进行多项目晶圆(MPW)流片,对电路进行配置,进行 D、C、B、A 首尾级联,配置成1 个128 位移位寄存器,增加输入信号为DI,输入时钟CLK 为500 MHz,示波器测试输出结果如图9 所示,其中输出分别为D、C、B、A,结果表明D、C、B、A 输出与输入分别相差 32 个时钟周期、64 个时钟周期、96 个时钟周期和128 个时钟周期,与仿真匹配良好,且实现了最高频率500 MHz 的目标,相较于市场主流芯片参考频率450 MHz,性能提高10%。

图9 配置成128 位移位寄存器的示波器波形

5 结论

本文对一种基于查找表的移位寄存器链架构进行设计、布局、仿真和优化,并在28 nm 工艺下进行流片和测试,测试结果表明功能和性能达到预期目标。所设计的基于查找表的移位寄存器可实现1~128 任意周期的移位操作,且最高工作频率可达到500 MHz,相比于市场主流28 nm 芯片的参考频率450 MHz,性能提高了10%。