基于FPGA 的多路并行混合数据存储系统*

2021-03-23沈学静张会新

刘 胜,沈学静,王 艳,陈 航,张会新*

(1.中北大学电子测试技术国家重点实验室,山西 太原030051;2.中北大学仪器科学与动态测试教育部重点实验室,山西 太原030051;3.首都航天机械有限公司,北京100076)

在新型导弹技术研发过程中,弹载存储测试系统起到的作用越来越大,地位越来越重要。 在大量的重复性试验过程中,获取的试验数据有着重要的意义,存储测试系统可以记录原始数据,用于研发人员分析设计是否合理以及是否满足最初的设计构想和技术指标。 弹载存储测试系统用于记录导弹在试验时全弹道过程的各种参数,比如发射膛压、飞行速度、飞行姿态、加速度信号等[1]。 大量试验结束后,通过上位机读取数据,分析、处理数据,可以不断改进设计问题,优化设计理念,用来确保导弹在存储、飞行过程中的安全性,以及对目标打击的准确性[2]。 为了减少数据丢失,实时存储接收到的数据尤为重要[3]。

文中设计的多路并行数据存储系统的存储电路体积减小,其存储器外部结构减小,质量减小,而存储容量增大,存储数据的种类增加。

1 系统总体方案设计

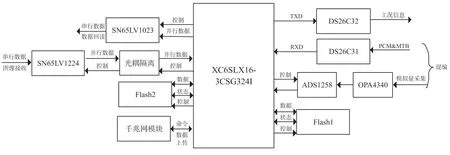

在多路并行数据存储系统中,各模块软件设计均由主控芯片XC6SLX16_3CSG324I 完成,以满足时钟频率需求。 数据缓冲是基于FPGA 内部丰富的RAM 资源[4],FPGA 强大的逻辑处理能力,使其成为最佳的主控芯片[5],根据实际情况分析,数据记录器实际工作环境为飞行器上,根据其实际工作环境性设计了两种工作模式,命令控制模式与上电即存模式。 命令接收模式为与地面测试系统匹配的工作模式,上电即存为实际工作模式。 上电后,返回工况信息,据工况信息,接收各种数据源,将并行数据与混编数据存储,并进行数据监测,且循环记录。 该系统总体设计框图如图1 所示。

图1 系统总体结构框图

2 硬件电路设计

2.1 数据接收模块设计

DYT 数据接收模块受AD 采样速率和发送系统带宽的影响,本系统数据传输速率25 Mbyte/s,传输速率相对较快,它使用LVDS 线缆进行数据传输。LVDS 接口芯片采用SN65LV1224,其为解串芯片,可以将大量高速数据实时快速地传输到存储设备中,并利用光耦合器隔离。 本系统中,接收时钟与发送时钟为同步信号;REFCLK 与RCLK 相同,均为25 MHz,FPGA 所配置时钟为80 MHz。

模拟量数据采用ADS1258 模数转换芯片进行数据采集,并且完成对16 路循环采集数据的实时记录。该模数转换芯片为24 位转换精度,采用自动通道采集模式,配置为16 路单端输入[6]。 使用选通开关ADG706 作为通道选择芯片,其最大开关频率为25 MHz;ADS1258 芯片的时钟选择使用内部时钟,所以不需要再接外接晶振,将管脚CLKSEL 拉高[7],由FPGA 产生的时钟信号由管脚CLKIO 输入,为ADS1258 提供了工作时钟[8]。 FPGA 与ADSl258 的接口、复位、控制、状态指示等引脚相连,完成模数转换的控制及寄存器的配置。 其硬件电路如图2 所示。

2.2 数据存储模块设计

图2 数据采集模块原理示意图

该模块使用的芯片是NAND FLASH MEMORY MT29F128G08AJAAA,它具有开放式NAND 闪存接口、单级单元技术、读写周期长、电压需求低、体积小、存储容量大等优点,该芯片是由Micron 公司生产的[9]。 芯片容量可达16GB,有2 个LUC,有2 个Plane,每个Plane 有2 048 个block,一个block 有256 页,每一页的存储容量为8 KB,芯片每一页内部有专门用于存储标记的信息或原始出厂信息以及自定义配置等信息的空间为448 byte,并通过共享R/B 信号的存储方式在逻辑上控制每一个逻辑单元号[10],进而实现数据的高速存储。 该芯片的工作电压范围为2.7 V ~3.6 V,本系统中其工作电压为3.3 V,上电后,首先发送复位命令将目标置于已知条件并中止正在进行的命令序列,然后检测R/B 信号,将tRSTA时间拉低后开始进行参数配置[11]。 该芯片的存储模式分为同步模式和异步模式,配置参数时,主要是配置Timing Mode[12]。 同步访问模式时钟要求更为严格,因为时序逻辑的稳定实现至少需要80 MHz 的时钟频率才能确保该模式正常运行;异步模式时钟要求相对宽松,对时钟频率的特殊要求只有在读写操作期间。

FLASH 芯片的典型写操作速度是可以通过计算得到的,芯片的编写操作的单位为页,每一页有8KB 的存储容量,典型页编程写的时间为350 μs,因此,根据上述三个条件就可以计算得到芯片的典型写操作速度理论值为:平均写入速度=8 KB×350 μs+8 KB×时钟速率。 本设计经过综合考虑后,采用异步模式,将异步操作中的读写操作的时钟频率代入公式中,得到对应的写速度为14.4 MHz。

3 FPGA 逻辑优化设计

该模块充分利用FPGA 可重构的优势,并合理利用了内部空间[13]。 文中充分利用FPGA 内部大量的专用乘法器和专用块非易失性存储块,以确保内部时序对内部fifo 和移位寄存器进行合理分配。根据各种数据写入速度分配fifo,PCM 数据写入速度为4.915 2 Mbyte/s,根据存储芯片的页编程时间,将fifo 容量设定为8K;模拟量采集速度为60 Mbyte/s,fifo 容量设定为85K,图像数据接收速度为25 Mbyte/s,fifo 容量设定为45K。

PCM 数据与采集数据混编存储,与DYT 数据并行接收存储。 在混编存储时,PCM 数据与采集数据有各自的帧标志,在数据回读过程中,利用帧标志来区分PCM 数据与采集数据。 为确保数据回读时数据完整性与准确性,添加FPGA 内部数据交换的握手原则,即在接收到命令后,进行数据上传,当数据上传达到32K 后,等待下一个命令。 逻辑模块图示意图如图3 所示。

图3 FPGA 逻辑模块图

4 系统测试结果

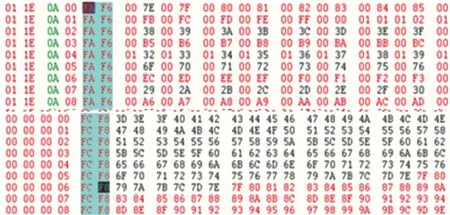

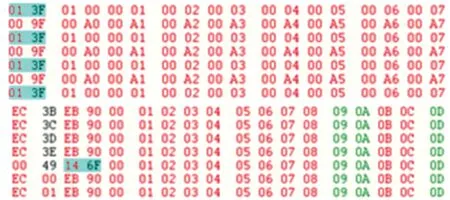

对于采集存储系统整体而言,其数据的准确性以及稳定性非常重要[14]。 为了检测所设计系统实用性,搭建一个测试平台并使用上位机进行测试。 设计DYT 数据源为0000-103F 及无效数据,得到的数据如图4 所示。 PCM 数据源为00-EC 的自加数,以主帧计数EB90 及副帧计数146F 为标志,经过测量得到的数据如图5 所示。 数据分析结果如图6 所示。

图4 DYT 数据测试结果

图5 PCM 数据测试结果

图6 数据分析结果

采集数据第2 通道输入4 V 的直流电压模拟信号,原始数据存储如图7 所示。 数据格式中的有效数据为4 个字节,通过帧计数可以判断数据是由哪个通道进行采集转换。

图7 采集数据存储

5 结语

本设计中,利用FPGA 可重构的优势,对内部资源合理利用,充分合理分配内部RAM 资源,设计了一种存储电路体积小,结构小,容量大,存数据种类多的存储系统。 该系统可混编并行存储多种数据,并返回记录器工作状态监测数据,系统存储速率最高可达25 Mbyte/s。 测试结果表明,测试结果正确,分析数据显示正确,该系统工作状态稳定,无丢帧现象。