基于FPGA和DDR3 SDRAM的高精度脉冲发生器设计与实现

2021-03-15施赛烽叶润川徐南阳

施赛烽, 叶润川, 林 雪, 徐南阳

(合肥工业大学 电子科学与应用物理学院,安徽 合肥 230601)

脉冲发生器在量子信息领域有着极其重要的作用,在量子实验中,各个仪器的控制与同步都离不开脉冲发生器。例如,在基于固态自旋量子调控实验[1-4]中,会对金刚石中的氮-空位(nitrogen-vacancy,NV) 色心进行一些操作,所用的仪器都是由脉冲发生器进行控制,如用脉冲信号控制声光调制器(acousto-optic modulator,AOM)来控制激光的通断、通过控制微波开关来调节发送微波脉冲的时间长度进而调控量子自旋状态等。

文献[5]分析了基于专用集成电路(application-specific integrated circuit,ASIC)芯片设计的脉冲发生器[6-7]和基于现场可编程门阵列(field-programmable gate array,FPGA)芯片设计的脉冲发生器[8]的优缺点;对于本文项目中的实验,基于FPGA的脉冲发生器更能满足实验的需求。本文项目组基于Xilinx Spartan-3E 系列 FPGA芯片和同步动态随机存储器(synchronous dynamic random-access memory, SDRAM)实现了最小精度为2 ns的多通道可编程脉冲发生器[5]。该脉冲发生器指令存储空间为32 MiB,通过USB2.0进行PC端与硬件端的通信,为实验带来了很大便利。然而对于演化时间非常短的物理现象,脉冲信号的精度和准确度都非常重要,符合实验要求的脉冲序列往往非常复杂,采用2ns精度脉冲发生器虽然也能完成实验,实验数据的准确度却会受到影响。因此,需要进一步提升精度、指令存储空间等性能,以便更精确地控制实验仪器,从而提升整个实验数据的准确度。

本文在文献[5]研究基础上,采用Xilinx Artix-7系列 FPGA芯片结合第三代双倍速率同步动态随机存储器(third generation of double-data-rate synchronous dynamic random-access memory, DDR3 SDRAM)芯片的方式来实现精度为1ns的24通道可编程脉冲发生器。对于本文实验,FPGA芯片等级的提升能使本文设计在更高频率的时钟下工作,同时将USB2.0传输提升至USB3.0以达到更高的数据传输速度。而DDR3 SDRAM能在时钟上升沿和下降沿同时传输数据[9-10],在频率不变的情况下,能完成的数据吞吐量是SDRAM的2倍;同时, DDR3 SDRAM相比于前2代,能够进行8位预读取[9],其每次读写操作位宽可达256位,大大提高了读写效率。

1 设计实现

1.1 系统架构

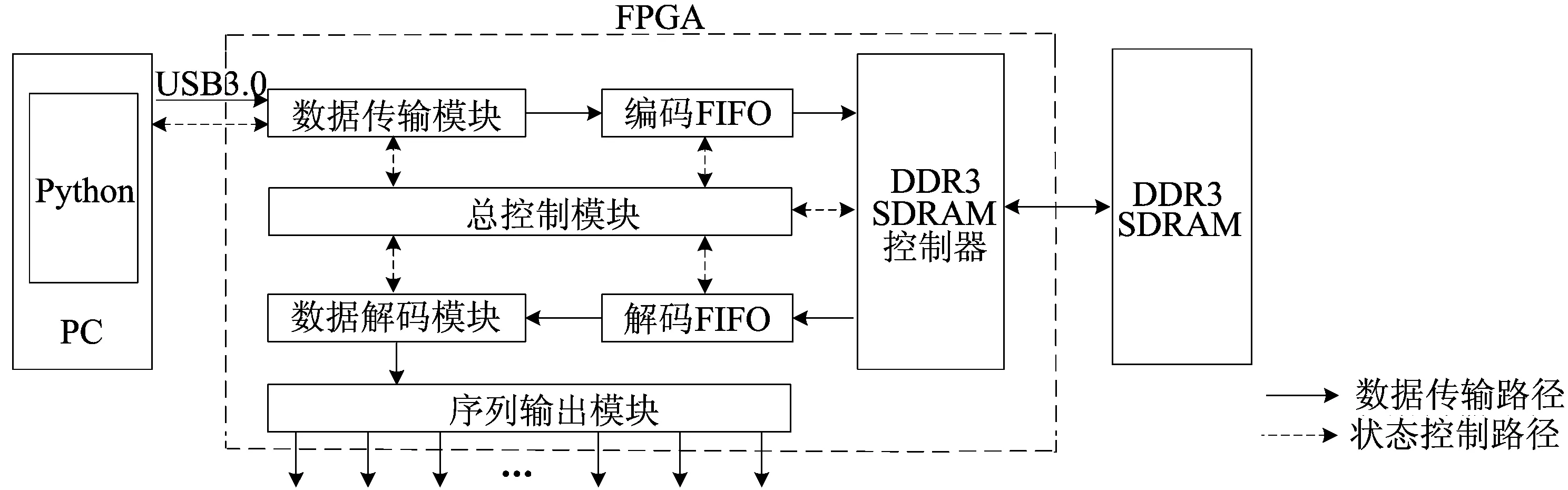

本文高精度数字脉冲发生器系统结构框图如图1所示,该系统由3部分组成:① 上位机系统,实现数字脉冲序列编码,向FPGA处理模块发送指令并接收状态反馈信息;② FPGA处理模块,主要包括数据传输模块、编码和解码先进先出(First-in First-out,FIFO)缓冲模块、DDR3 SDRAM 控制模块、数据解码模块、序列输出模块及总控制模块;③ DDR3 SDRAM 芯片,用来存储上位机发来的脉冲序列数据。

图1 数字脉冲发生器系统结构

1.2 软件设计

本设计的上位机采用 Python语言作为控制和编程环境,大大简化了控制和编译难度;同时,用数字0和1将电平的高低直接表现出来,这种方式最大的优点是可以将脉冲信号时间顺序通过数据直观地表现出来[11],但是,采用这种方式也会产生大量的存储数据,使得最终输出的脉冲信号时间长度完全受限于存储空间的大小,也大大增加了操作难度。因此,本设计对这些二进制数进行了编码,在发送指令时只需给定参数而不用指定每个时间片的高、低电平,最终通过编码数据在硬件端的处理算出所有的脉冲信息,从而有效降低了数据的复杂性和实验人员的操作难度。

编码后的脉冲数据为128 bit,其数据格式如图2所示。

图2中:停止位stop为最高位,控制脉冲数据传输的结束;计数位count为96~126位,该31位数据控制当前脉冲数据循环的次数;序列信息位sequence为低96位,表示24个通道的脉冲序列信息,每个通道占4位。

图2 编码后的数据格式

编码完成后的数据通过USB3.0发送给FPGA的数据传输模块;同时上位机发送控制命令控制FPGA的状态,并通过数据传输模块接收FPGA的状态反馈信息[12-13]。

1.3 FPGA硬件实现

FPGA的数字逻辑模块如图1虚线框内所示。

总控制模块用于接收上位机发来的控制指令,从而控制存储器、FIFO的复位,存储控制器的读写以及将当前状态反馈给上位机;数据传输模块用于接收上位机发来的指令并传送给总控制模块,以及将上位机发送的编码数据传输给编码FIFO,实现上位机与FPGA之间的通信;编码FIFO模块和解码FIFO模块则是起到了优化电路时序和改变数据位宽的作用[14]。

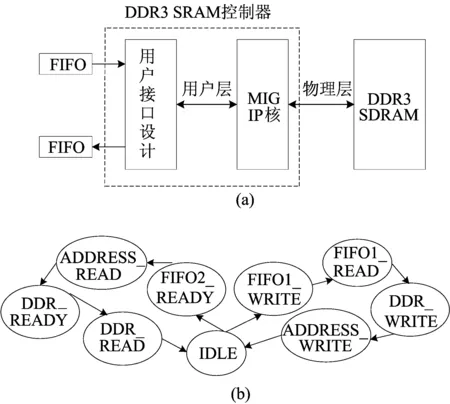

本设计通过调用MIG IP核以及对用户接口进行相应的设计来实现对DDR3 SDRAM的控制。外部输入时钟为200 MHz,位宽为32位。DDR3 SDRAM工作时钟为400 MHz,而DDR3 SDRAM双边沿读写数据的特点能使读写速率达到800 MHz。DDR3 SDRAM控制器如图3所示。

图3 DDR3 SDRAM控制器

写状态包含:① IDLE,初始化完成后,等待写指令;② FIFO1-WRITE,判断编码FIFO中的数据是否有效;③ FIFO1-READ,判断DDR3 SDRAM中的存储空间是否足够完成一次突发写入,若可以,则将数据从编码FIFO模块中读出;④ DDR-WRITE,存储控制器向DDR3 SDRAM中写入数据;⑤ ADDRESS-WRITE,判断存储控制器向DDR3 SDRAM中写入的数据是否完成,若完成,则将写地址加8。读状态包含:① IDLE,初始化完成后,等待读指令;② FIFO2-READY,判断FIFO中的存储空间是否能够完成一次突发写入;③ ADDRESS-READ,判断读写地址是否相同,若相同,则读地址置0。若不相同,则读地址加8;④ DDR-READY,判断DDR3 SDRAM中的数据是否有效;⑤ DDR-READ,将数据从存储器中读出写入编码FIFO。

数据解码模块的功能是将软件端编码的数据进行相应的解码。低96位通道信息数据传输给序列输出模块产生高精度脉冲;31位count值设计为一个减法计数器,在count=0之前,循环地将当前96位的通道信息数据传输给序列输出模块;stop用来控制单次脉冲的结束,stop=1时,停止脉冲数据更新;stop=0时,继续从解码FIFO中更新脉冲数据。

序列输出模块的功能是将解码模块产生的96位通道信息数据进行序列化输出。数据以24×4的形式并行输入,通过高速并串转换产生脉冲序列。并串转换的过程如图4所示。

图4 解码与高速序列化输出过程

整个并串转换过程分为2段,第1段以250 MHz的工作时钟完成2位数据的并转串,第2段再以500 MHz的工作时钟进行并串转换,并通过专用数据输出寄存器(dedicated dual data rate output register,ODDR)完成数据的输出。ODDR能实现数据在上升沿和下降沿同时输出数据,因此在500 MHz的工作时钟下,最终实现了24个通道精度为1 ns的脉冲序列信号,其电平标准为LVCOMS33。

2 测试与验证

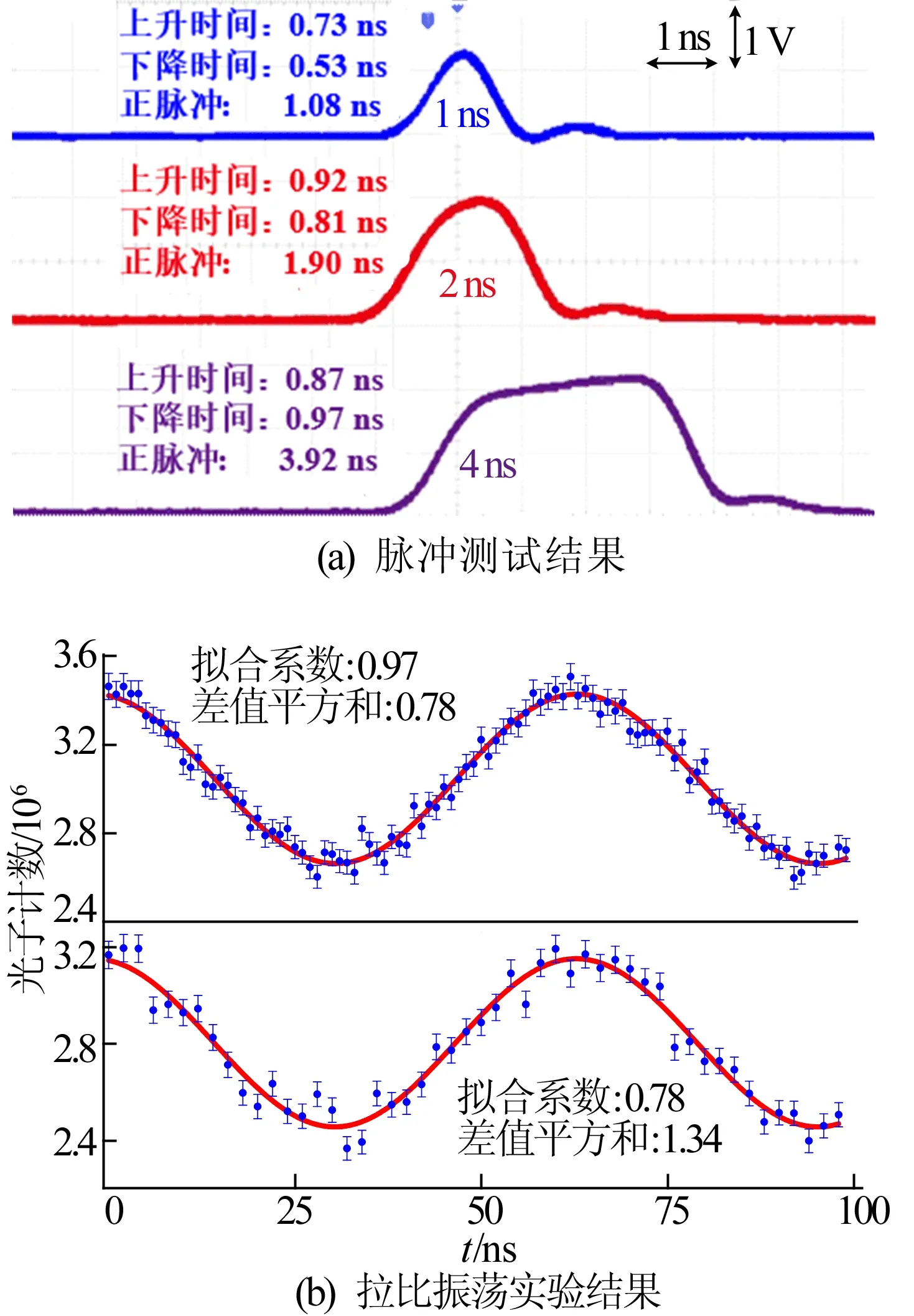

本设计的软件环境采用Python2.7,硬件综合工具为Vivado2016.3。硬件部分选用Xilinx公司Artix-7系列的XC7A200T-1FGG484芯片和2片Micron公司MT41K256M16TW型号DDR3 SDRAM芯片。2片DDR3 SDRAM的位宽为32位,存储空间高达1 GiB。本文对脉冲发生器进行测试的设备是普源公司的DS4054型号示波器,其带宽为500 MHz,最高实时采样率为4 GSa/s。最终的测试与实验结果如图5所示。

图5 脉冲测试和拉比振荡实验结果

图5a所示为同一时间脉冲发生器3个通道的输出脉冲信号,其宽度的设置分别为1、2、4 ns。由图5a可知,其输出实际值与设定值基本吻合。因此,可以得出以下结论:① 可以产生最小脉冲宽度和精度为1 ns的信号;② 上升沿和下降沿时间均小于1 ns;③ 各个通道可独立稳定工作。

本文还通过拉比振荡实验分别对2种精度的脉冲发生器进行了验证。首先,通过一段532 nm激光将电子自旋态以较高保真度初始化到ms=0基态上,然后施加微波脉冲序列实现电子自旋态翻转[15],最后利用激光读出NV电子自旋荧光信息。

由图5b可知,2种精度下拟合系数分别为0.97、0.78,这表明用1 ns精度产生的数据拟合度更高;2种精度下差值平方和分别为0.78、1.34,这表明1 ns精度拟合图形上的点与真实实验数据差值更小。由此可见,本文设计的1 ns精度脉冲发生器大大提高了实验数据的准确性。

3 结 论

本文实现了基于FPGA和DDR3 SDRAM的1 ns精度多通道可编程脉冲发生器。本设计在提高精度和提升指令存储空间的同时,仍保持了2 ns精度脉冲发生器多通道、可编程、可与外部时钟同步等特点。对系统产生的脉冲信号进行测试,结果表明,输出脉冲达到1 ns精度且各通道工作稳定、互不影响。采用NV量子实验平台通过拉比振荡实验对本设计加以验证,并与2 ns精度的脉冲信号对比,结果表明其不仅能够产生符合量子调控实验需求的脉冲信号,而且能使实验数据更加准确。由于本设计的最小精度主要受限于FPGA芯片的工作频率,随着FPGA性能不断进步,本设计可达到的最小精度仍会有很大的提升空间。