基于LVDS的速度自适应数据回读系统设计与实现

2021-02-25毕彦峰胡陈君高诗尧

毕彦峰,李 杰,胡陈君,高 宁,高诗尧

(1.中北大学 电子测试技术重点实验室,山西 太原 030051;2.苏州中盛纳米科技有限公司,江苏 苏州 215123)

0 引 言

常规导弹弹药在研制试验阶段,为进行测试反馈,数据的采集回读是一种最重要的手段[1-2].在导弹射前进行靶场测试时,数据回读也是监测弹药状态的一种十分重要的方式.由于导弹型号的差异,离线式采集存储设备的安装位置并不完全相同,数据传输的线缆长度不统一,以及弹药所提供的接口数量有限,都会导致数据回读设备达不到最大带宽,而数据回读系统往往都有一个预设的传输频率,从而导致离线式数据存储系统与数据回读系统的传输速度不匹配.

为解决以上问题,提出一种接口速度兼容的通用数据回读设备.数据回读设备与采集存储设备之间的接口采用LVDS传输协议,LVDS接口为串行总线,能够有效地减少接口线缆的数量,并且具有很强的抗干扰能力[3-4].控制和传输部分采用FPGA搭配USB2.0芯片,能够自适应不同的LVDS时钟和数据,实现对LVDS数据的串并转换、总线的命令解析发送和数据的传输控制,并将数据通过USB接口发送至上位机.

1 系统总体设计

通用数据回读系统由串并转换单元、FPGA控制单元、USB传输单元和上位机4个部分组成,系统框图如图1所示.

图1 系统总体设计Fig.1 Overall system design

通用数据回读系统的主要工作流程为:FPGA接收前端LVDS总线数据,通过串并转换单元使用FPGA内部串行收发器将数据反序列化,经由片内RAM缓存通过USB2.0芯片发送至上位机.FPGA采用Xilinx公司Spartan6系列XCS6LX9-144I型号芯片,此款芯片自身支持LVDS接口和SERDES,通过内部IBUFDS模块可以将差分信号转换成单端信号使用,通过SERDES简化了电路串行化和反序列化的设计[5-6],并根据内部相位检测电路设计模块,动态地调整数据和时钟的相位关系,使数据的中心和时钟的上升沿始终保持对齐,有效地减少了数据传输的误码率.USB传输单元采用FTDI公司的FT232H芯片,具有时序简单、传输速度快等优点.上位机采用Qt框架编写,数据的传输架构采用多线程读写,很大程度上提高了USB传输的速度.

1.1 自适应时钟频率

为了实现自动适应不同频率的传输总线,对差分时钟的处理尤为关键.传统的时钟直接连接在FPGA的普通引脚上,无法使用FPGA内部的全局缓冲时钟资源,导致时钟到达每个触发器的路径延迟不一致,如图2所示,利用普通布线资源会导致T1和T2不相等,从而产生时钟偏斜.

图2 时钟偏斜Fig.2 Clock skew

当系统的时钟频率较低时,内部逻辑可以正常运行,当时钟频率达到一定速度后,就无法满足触发器的静态时序要求,尤其在FPGA芯片工艺较低时延迟较大,会导致时序无法收敛,可以通过两种方式解决:使用FPGA内部硬核锁相环或专用时钟网络BUFIO2.

通过锁相环可以将输入时钟进行分频,但锁相环的使用需要设置输入输出的时钟频率,其虽然可以满足时序收敛但是无法自适应外部的不同时钟频率,所以锁相环无法满足需求.为了自动适应外部差分时钟并使时序收敛,可以使用FPGA的内部专用时钟网络BUFIO2.BUFIO2的连接如图3所示,首先将LVDS数据的随路时钟通过IBUFDS转化为和LVDS数据同步的单端时钟,然后通过BUFIO2将单端时钟按照模块例化时预设的分频系数生成时钟.将LVDS数据的差分随路时钟经过IBUFDS产生的单端时钟连接到BUFIO2,分频系数设置为8,即产生差分时钟的8分频时钟,此分频时钟可以通过BUFG连入到全局缓冲,从而消除时钟偏斜,并且连入到全局缓冲BUFG输出的信号与恢复的并行数据同步,从而解决了对LVDS任意时钟的固定分频问题,并提供了一个优质的全局时钟.BUFIO2生成的IO时钟以及选通脉冲可以结合SERDES对数据进行串并转换.

图3 时钟兼容Fig.3 Clock compatible

1.2 串行数据转并行数据

PC中数据的最小存储单元为1个字节,所以一般设置总线位宽为8位,而单个Spartan-6系列FPGA内部的串行收发器SERDES最高支持4∶1的数据反序列化[7-8].

FPGA提供了一种机制,将两个SERDES级联即可实现8∶1以及更高比例的数据反序列化.每个LVDS接口恰好含有两个SERDES,通过如图4所示的方式进行级联可以实现8∶1的数据反序列化.

图4 ISERDES级联Fig.4 ISERDES cascade

1.3 动态调整相位

当LVDS接口线速率比较高时(>1 Gbit/s),PCB走线以及线缆的不等长和温度等因素会导致时钟与数据发生错位,不能满足数字电路的建立保持时间等时序要求,这会极大地提高数据传输的误码率,并且随着工作环境的改变,温度等因素对误码的影响也会发生变化.当速度不高时,数据和时钟的相位对数据的传输影响不大,当时钟频率达到一定程度时,这种错位就无法忽视[9],可以通过在数据通路上添加延迟来解决数据和时钟的相位问题.

如图5所示,理想的数据信号的建立保持时间符合要求,可以正确地传输数据,但由于线路不等长或温度等因素,实际数据信号相对于时钟信号发生了相位偏移,导致建立保持时间难以得到满足,此时在数据通路上添加延迟可以使得建立保持时间重新得到满足.这种手动添加延迟的方法虽然有效,却不能兼容所有的数据路径错位问题.解决办法就是在数据通路上加入IODELAY模块,此模块不仅能加入延迟,还支持动态地调整延迟值.

图5 接口时序Fig.5 Interface timing

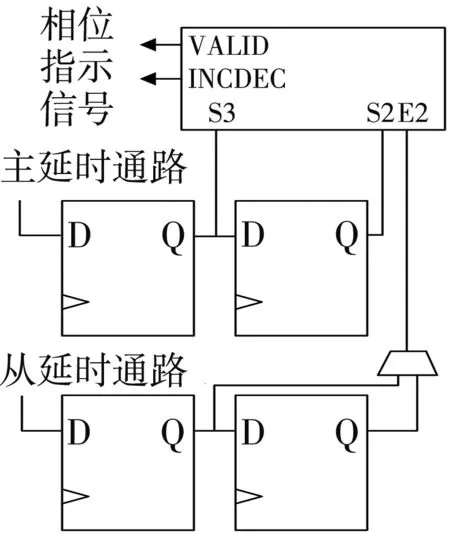

进行动态调节延迟的前提是了解数据和时钟的相位关系,相位检测电路如图6所示,其中INCDEC信号用来指示当前数据和时钟的相位关系,VALID信号表示当前的INCDEC是否有效.当E2=S2时,表示数据中心相位超前于时钟上升沿,INCDEC输出为1;当E2=S3时,表示数据中心相位落后于时钟上升沿,INCDEC输出为0.根据鉴相器的输出逻辑设计模块,当检测到INCDEC为1时,则驱动IODELAY减小延迟;当检测到INCDEC为0时,则驱动IODEALY增大延迟.

图6 相位检测电路Fig.6 Phase detection circuit

串并转换模块的具体连接如图7所示,相位检测状态机检测到有效的相位信息后,置位从IODELAY2的CE,并根据相位信息驱动从IODELAY的INC信号,此时从IODELAY2的BUSY信号会被拉高,表示从IODELAY2接收到相位信息.当BUSY信号被拉低时,相位检测状态机即可使能CAL信号控制主从IODELAY2进行延迟的调整.

图7 串并转换模块Fig.7 Serial-to-parallel conversion module

由于INCDEC只能指示超前和滞后,所以当校准完毕后,相位校准信号始终处于0~1的跳动状态中.动态调整相位可以使数据的中心始终和时钟的上升沿保持对齐.动态校准相位流程如图8所示.

图8 相位动态调整流程Fig.8 Phase dynamic adjustment process

1.4 数据对齐

当传输串行数据时,LVDS总线前端将并行数据序列化进行传输,串并转换单元需要将串行数据转换成并行数据,此时需要对数据进行对齐,即确定这一帧的第一位.

通过LVDS链路双方约定固定帧0xEB确定当前总线是否空闲和数据是否对齐完成.当LVDS总线初始化或空闲时,总线上的数据不为0xEB,则需要使能SERDES的BITSLIP信号,每使能一次,相当于转换输出的并行信号循环移位一次,直到并行数据与约定的数据0xEB一致时,如图9所示,则表示数据对齐.

图9 数据对齐Fig.9 Data alignment

1.5 片内缓存

本设计的缓冲区采用FPGA片内块RAM,利用Xilinx提供的FIFO IP核生成首字预见型FIFO.首字预见型FIFO可以在不影响读写功能的前提下,观测到即将出队列的数据,相比于标准FIFO,首字预见型FIFO更加灵活,更有益于指令的发送和控制.相比于外部RAM,此设计方式可以缩小体积,降低成本.

1.6 USB传输单元

USB接口芯片采用FTDI公司的FT232H,支持UART、同步FIFO等多种模式,具有传输速度快、时序简单等优点[10-11].

1.6.1 初始化流程

FT232H芯片的初始化流程主要是配置工作模式以及初始化时钟.FTDI公司提供了FT_Prog应用程序,可以配置工作模式、驱动电流强度、压摆率和挂起状态等多种参数,并将配置信息烧写到配置芯片中.USB芯片每次上电都会读取配置芯片EEPROM中保存的配置信息,以确定FT232H的工作模式.但此时芯片还不能完全工作在同步FIFO模式,还需要应用程序驱动芯片设置模式,使用驱动提供的接口FT_SetBitMode命令选择同步FIFO,芯片才会产生工作的60 MHz 时钟[9].

1.6.2 传输控制

FT232H芯片的传输时序控制十分简单,当进行写FT232H芯片时,如果芯片准备好可以被读出数据,则会驱动RXF引脚.当RXF信号为低电平时,用户可以驱动OE信号和RD信号,并根据FT232H芯片输出的时钟将数据同步地读出来.当进行写FT232H时,如果TXE有效,表示FT232H片内缓冲区非满,此时可以驱动TX信号为低,根据FT232H输出的时钟将数据写入芯片中.

1.7 上位机

1.7.1 驱动

FTDI公司为FT232H芯片提供FTDIBUS.SYS驱动包括虚拟COM端口(VCP)驱动和直接驱动(D2XX).VCP驱动模拟标准的PC串行端口,USB设备可以作为一个标准RS232的通信设备.D2XX驱动程序允许通过一个DLL接口直接访问USB设备.

上位机在Qt环境下使用C++语言编写,将驱动中提供的ftd2xx.h以及ftd2xx.lib链接到工程中,即可直接驱动FTDI公司提供的动态链接库FTD2XX.DLL.通过动态链接库中的接口增大了PC端USB的缓冲区,提高了突发传输的瞬时速度.

1.7.2 缓冲区设计

为了提高USB接口的传输速度,上位机采用多个线程并设置了两个大容量缓冲区,如图10所示,其中一个线程读取USB设备中的数据并将数据保存在其中一个缓冲区中,当一个缓冲区存满之后,继续将数据保存在另一个缓冲区,另一个线程负责将存满数据的缓冲区写到硬盘中.两个线程同时工作,读取USB接口的数据与写硬盘同时进行,大大提高了USB接口的传输速度[12].

图10 上位机多线程结构Fig.10 Multi-threaded structure of the host computer

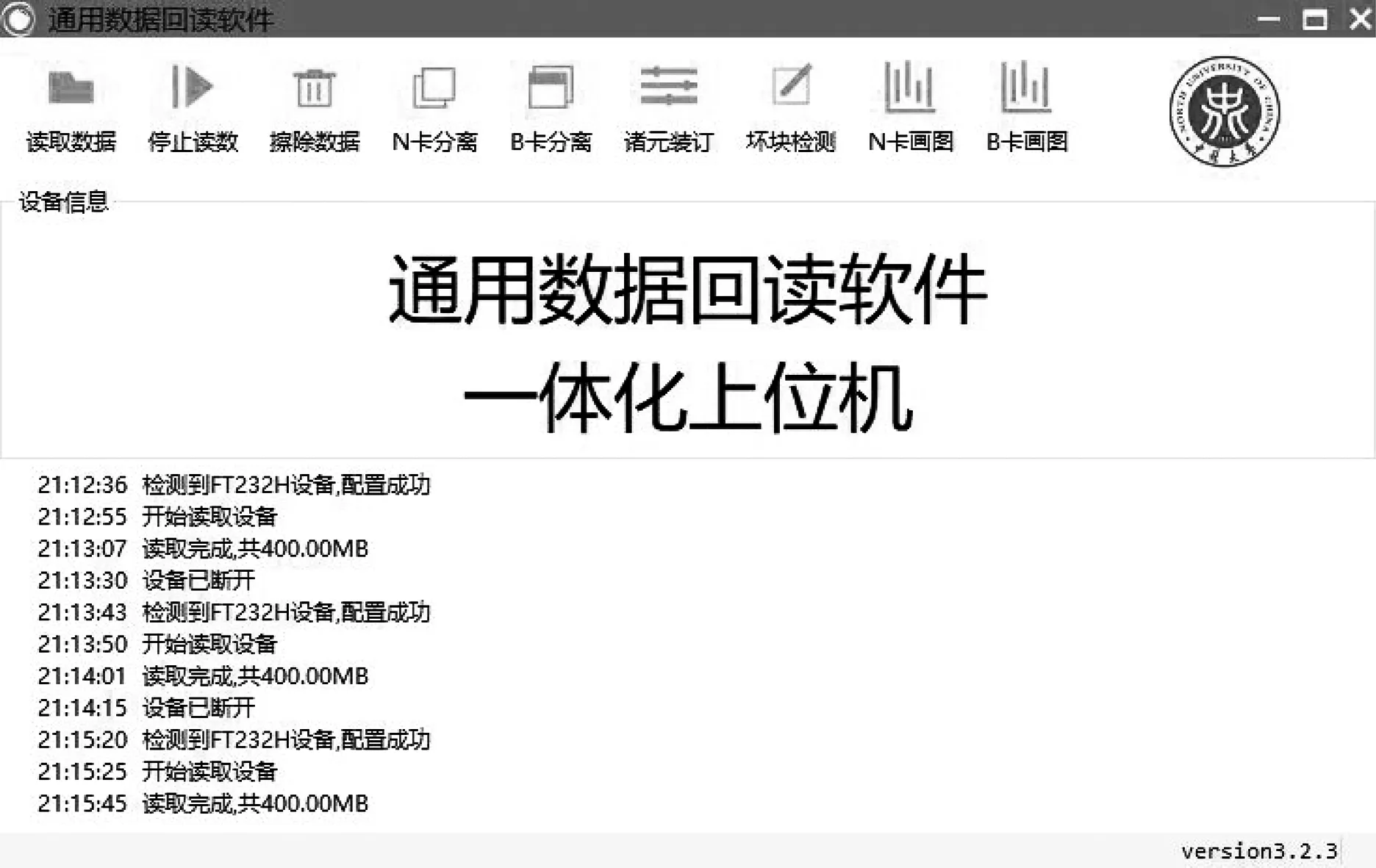

上位机的主要功能为配置设备、发送读取命令、擦除命令以及数据处理.上位机启动后就会持续监测设备,当检测到设备连接到上位机,上位机会自动发出配置指令,这样FT232H芯片才能工作在预期的状态.其他命令为上位机与设备前端约定好握手协议,用来实现读取、擦除和停止等多种功能.

2 硬件实验结果

首先使用Xilinx公司提供的ICON和ILA两个IP核进行测试,验证整个相位校准的流程.如图11所示为抓取的真实波形,根据图中标记1,当鉴相器VALID信号拉高时,INCDEC指示的相位状态有效.获取到当前数据和时钟的相位关系后,开始进行相位校准,使能IODELAY2的CE信号,并根据INCDEC指示的状态控制IODELAY2的INC信号将信息传递给IODELAY2,IODELAY2接收到相位信息则会进入BUSY状态,当BUSY拉低时,即可使能IODELAY2的CAL信号,此时IODELAY2再次进入BUSY状态开始调整延迟,当BUSY再次拉低时表示延迟调整完成.紧接着进入标记2的状态,延迟调整完成后鉴相器会再次指示调整之后的相位关系.从图中可以看到,在VALID信号有效时,INCDEC处于高低电平的跳变状态,此时相位的校准已然完成.

图11 相位校准的实际过程Fig.11 The actual process of phase calibration

然后验证通用数据回读系统的时钟兼容功能,通过如图12所示的硬件电路进行数据回读测试,通过前端LVDS总线发送数据,数据回读系统接收数据,并将接收到的数据通过USB接口发送到上位机.

图12 硬件电路Fig.12 Hardware circuit

将设备上电,上位机会检测到设备并配置设备,通过上位机对采集设备发送指令,确认指令后前端采集设备会将数据通过USB传输设备将数据传输到上位机.实际测试时分为3种情况:

1) 时钟线缆与数据线缆等长,以大约40 MB/s 的速度传输数据;

2) 时钟线缆与数据线缆不等长,以大约40 MB/s 的速度传输数据;

3) 时钟线缆与数据线缆等长,以大约20 MB/s 的速度传输数据.

数据的内容为一个字节的递增数,大小均为400 MB.如图13所示,使用两种不同速度的时钟传输400 MB数据分别用时12 s和20 s.数据传输的结果如图14所示,3次测试接收到的数据相同.

图13 传输时间Fig.13 Transmission time

图14 回读的数据Fig.14 Read back data

3 结 论

本文分别从数据回读系统的硬件总体设计、自适应时钟的实现和通过动态调整相位方法解决链路不等长和温度等因素造成的误码现象,并通过构造多线程上位机来提升USB接口的传输速度.通过对多种速度的LVDS总线进行数据回读测试,系统可以自动适应不同时钟速度的传输,并且传输的数据相同.经过验证,通过BUFIO2对时钟进行分频,鉴相器等实现动态调整时钟和数据的相位关系,自动适应不同的时钟频率,实现了速度兼容的通用数据总线系统,为离线式数据存储系统的回读提供了一种通用的传输速度快、灵活可靠和可移植性强的方案.