基于以太网高速协议通道的FPGA 端系统设计

2021-02-03孙伟龙

王 乐,赵 刚,孙伟龙

(北方自动控制技术研究所,太原 030006)

0 引言

由于计算机处理器速度和外围设备速度的不断提高,在众多实验环境中需要高速数据互连介质,用于通信的介质需能够实现长距离传递可靠的数据[1-2]。为了突破所有这些限制,需保证互连技术是串行且异步的。与其他技术相比,光纤通道是具有更高数据速率的互连技术[3]。光纤通道支持不同的协议,以不同的速率传输数据,如音频和视频[4]。光纤通道的高带宽和减少的干扰特性使其具有进行高速通信的优势[5-6]。航空电子环境需要高速互连介质来在终端系统之间传输大量数据。根据航空电子环境(AE)的要求,光纤通道委员会(FC)在航空电子环境中提供了子协议FPGA[6]。目前,光纤通道已被用作航空电子总线以及专用总线,以实现较高的数据速率,从而在单元之间传输数据和视频[7-8]。航空电子环境需要高速互连介质来在终端系统之间传输大量数据。根据航空电子环境(AE)的要求,光纤通道委员会(FC)在航空电子环境中提供了子协议FPGA[9]。目前,光纤通道既用作航空电子总线,又用作高数据速率的专用总线,以在设备之间传输数据和视频[10]。FPGA 是协议和配置文件的集合,指定了光纤通道在设备中的应用,用于商业和军事航空航天领域[8-9]。

基于以上情况,结合航空电子系统的通信需求,提出了一种基于以太网的航空电子环境数据协议的设计方法,该方法通过FPGA 平台端系统中实现,具备并发执行能力,同时考虑了错误检测机制,将错误检测机制嵌入到协议设计中,以验证其在端系统中数据接收的完整性。

1 FPGA 协议

FPGA 协议提供了不同的服务类别,即1 类,2类,3 类和6 类。这些服务类别的主要区别在于两个通信端口之间通信服务的分配和保留。

1 类是专用的连接服务,提供两个端口之间的专用连接。这是一个基于确认的协议。

2 类不是专用的连接服务。它是在帧边界具有结构多路复用的服务。

3 类是一种连接少且未经确认的服务。

6 类是专用的连接服务,具有多播连接功能。单个源端口将与多个目标端口形成专用连接。

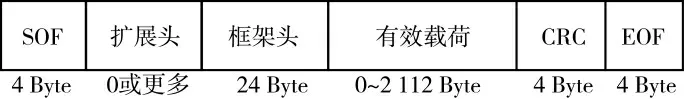

FPGA 协议应包含最大2 148 个字节的帧。该框架将由5 个字段组成,包括:帧开始(SOF)、帧头、数据字段、CRC、帧结束(EOF)。

为了维持适当的链路,应该在帧之间发送空闲的原始信号(理想帧)。FC_AE 帧的帧结构如图1 所示。

图1 FPGA 帧结构

描述:

1)帧开始(SOF)

帧起始定界符是一个有序集和多个定界符,用于序列控制。SOF 分隔符通常由SOFX 表示,其中X表示使用该分隔符的特定类。

2)扩展头

扩展页眉是框架的可选页眉。如果存在扩展的标头,则紧随其后是SOF 分隔符。扩展头的存在是由帧头定义的。扩展头用于在框架中添加额外的功能。

3)帧头

如果扩展头不可用,则帧头将紧随SOF 分隔符。帧头用于控制链接操作,设备协议传输,还用于检测序列中丢失的帧或乱序帧。

4)有效载荷

需要从一个终端系统发送到另一终端系统的数据打包在此有效负载字段中。每帧有效负载的最大为2 112 Byte。

5)CRC

CRC 是帧的循环冗余校验。标头的开始和标头的结束不包括在CRC 计算中。CRC 是一个4 Byte的字,是为扩展头(如果存在)、帧头和有效载荷计算的。CRC 用于帧的错误处理。

6)帧尾(EOF)

EOF 分隔符是一个4 Byte 字,是一个有序集,紧跟在帧的CRC 字段之后有多个EOF 定界符用于序列控制。

2 协议实施中使用的框架

在这种类型的服务中,目标可以丢弃源发送的多个帧而无需任何确认。流控制框架不属于此类服务。实现数据帧通信序列以建立通信。数据帧有两种类型。初始化帧在两个NX_port 之间创建通信电路,而普通数据帧则将信息从源端口传输到目标端口。

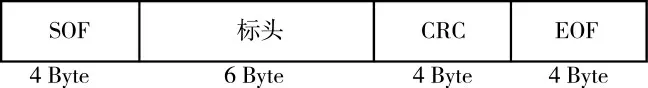

初始化帧的结构如图2 所示。

图2 初始化帧的帧结构

初始化帧的SOF 定界符是SOF 启动(Sofi)。该帧建立两个端口之间的通信。标头包含序列ID,源ID 和目标ID 的信息。由于该帧是第1 帧,因此,该帧的序列计数为0。标头中的其余字段填充有适当的信息,以将该帧表示为第1 帧。由于第1 帧是通信初始化帧,因此,它不包含数据。为不包括SOF 和EOF 分隔符的完整帧计算CRC,并将其填充在CRC字段中。EOF 字段包含EOFn3 的值,该值指示帧的正常结束。此帧中使用的EOF 并不表示通信终止。

普通帧的SOF 定界符为SOF 普通类3(SOFn3)。该值表示该帧是数据帧。标头中的序列计数(SEQ_CNT)字段(标准)指示序列中当前帧的计数。数据帧由标题和有效载荷字段组成。有效负载字段填充有要传输到目标终端系统的数据。为报头和有效载荷计算CRC。CRC 被打包在帧中的有效载荷字段之后。EOF 字段由帧定界符的末尾组成,它可以代表帧的正常端或端口之间通信序列的端接。

3 架构设计

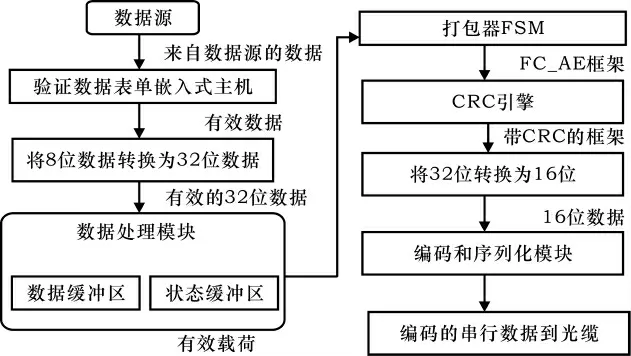

光纤通道数据发送器设计的框图如图3 所示。台式计算机被用作实现的数据源。在主机系统中会生成有效载荷,以及应通过光纤通道帧发送的标头信息。数据以UDP 数据包的形式生成,这些数据包从主机系统发送到FPGA。

图3 TX 设计模块

3.1 数据搜集与处理

主机系统用于以UDP 数据包的形式生成数据并发送到FPGA。主机与FPGA 之间的通信是通过以太网链路建立的。

1)数据包生成:Visual Studio 用作生成以太网数据包的软件开发平台。在Windows 平台上打开并配置了基于以太网的套接字,以建立以太网链接。一旦配置了套接字,就可以通过套接字将数据传输到FPGA。

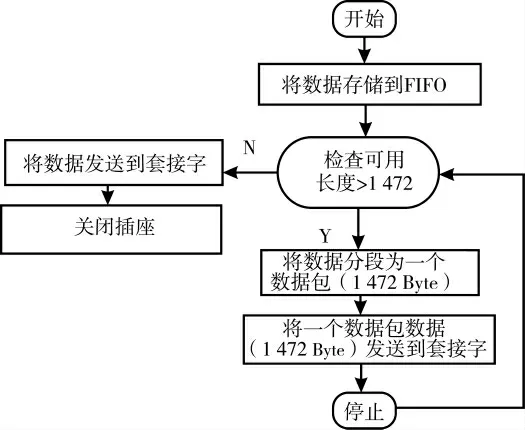

2)生成数据包:产生UDP 数据包的流程图如图4 所示。可以通过以太网发送的最大有效负载大小为1 472 Byte。如果数据大于1 472 Byte,则应将数据分段并通过多个数据包传输。

主机生成的以太网数据包(UDP)由FPGA 板接收。

主机系统应将其他数据包连同UDP 数据包一起发送到FPGA。接收到的数据必须经过验证,以区分目标UDP 数据包与其他帧。验证是通过对照板IP 地址和端口号检查UDP 帧中的目标IP 地址和端口号来完成的。当IP 地址和端口号匹配时,帧应被视为有效的UDP 帧。

UDP 数据包中的数据字段是面向字节的(8位),需要转换为字格式(32 位)才能将数据从UDP数据包映射到FC_AE 帧。由转换器模块完成向32位的转换。转换器模块在时钟的每个上升沿接收字节数据。该模块将数据的每4 个字节与第4 个时钟脉冲的上升沿连接在一起。这4 个字节(32 位)的数据作为输出发送。

来自转换模块的32 位字数据流在有效载荷FIFO 中进行缓冲。

每个接收到的数据包的状态都存储在状态FIFO 中。状态FIFO 指示有效载荷FIFO 中是否存在有效的载荷数据包数据。

此外,将从转换器模块获得的有效数据存储在数据FIFO 中。在每个VAL ID SHIame 的末尾,SHIame 的状态存储在状态FIFO 中。根据FIFO 中空间的可用性执行将数据和状态写入相应FIFO 的操作。光纤通道帧打包器模块监视状态FIFO,以生成FC 帧。

图4 生成UDP 数据包的流程图

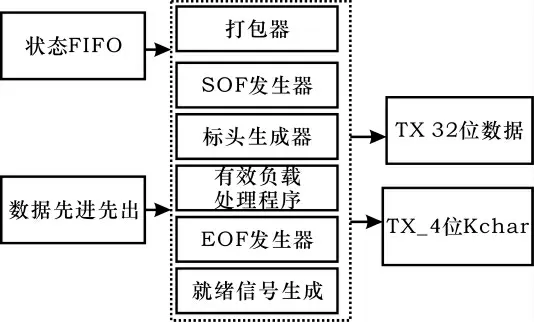

3.2 打包器模块

图5 FC_AE 帧打包器

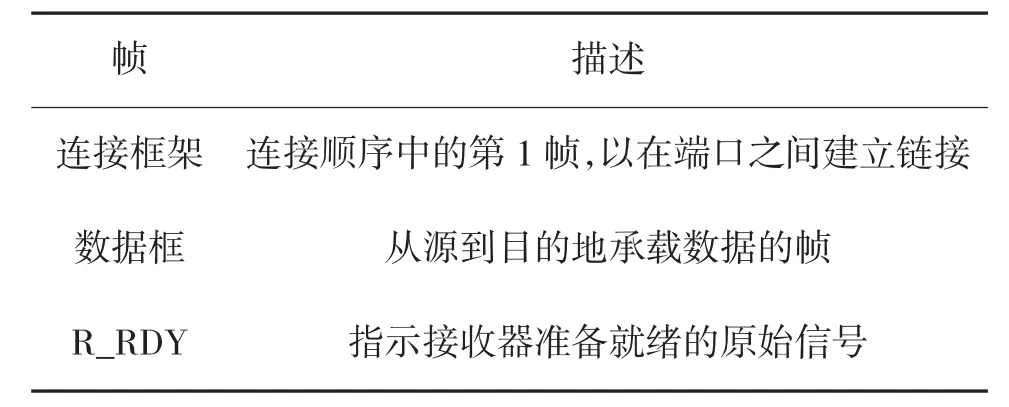

FPGA 帧的字段包括SOF、标头、有效负载、CRC 和EOF。根据状态FIFO 中状态信息的可用性,生成FC 帧。状态FIFO 为空表示有效载荷FIFO 中的数据不可用。打包器将生成空闲字,以在数据帧不可用期间维持端端口之间的连接性。3 类服务是在光纤通道协议上实现的。下页表1 显示了第3 类服务支持的帧和信号。

打包器模块生成表1 中所示的帧。此模块生成32 位的数据(TX-Data)和4 位的特殊字符指示符(TX-KC HAR)。4b KCHAR 对于8b/10b 编码是必需的。

表1 在CLASS3 服务中使用的帧

打包器模块中的每个状态如下:

1)SOF 生成

从主机获取的数据中有效载荷的第32 位字包含有关要生成的帧类型的信息。根据该值,此模块将为不同类型的帧生成必要的SOF 分隔符类型。

2)标头生成器

有关基于光纤通道的协议帧的标头信息存储在数据FIFO 中。标头生成模块从数据FIFO 中读取数据,并将其打包为光纤通道数据帧的标头字段。

3)有效负载处理程序

可以通过基于光纤通道的数据协议帧发送的最大有效负载大小为2 112 Byte。有效负载处理程序从有效负载FIFO 读取数据,直到数据包的末尾。有效负载处理程序从有效负载FIFO 中读取一个数据包数据,以生成一个光纤通道帧。数据FIFO 上帧数据的最后一个字由最后一个识别信号加起来表示。

4)EOF 生成

从主机获得的数据中有效载荷的第1 个32位字包含有关要生成的帧类型的信息。根据该值,此模块会为不同类型的帧生成必要的EOF 定界符类型。

5)R_RD Y 生成器

打包器模块根据接收模块的请求生成READY信号。当接收器准备好接收帧时,它请求打包器模块生成R-ROY 信号。发送器向接收器发送确认,作为就绪信号生成的指示。

6)打包器的Control_flow

打包器工作的状态序列如图6 所示。

图6 打包程序的状态图

打包器保持空闲状态,直到数据FIFO 中的有效数据可用为止。初始化帧是根据数据FIFO 中有效数据的可用性生成的。初始化帧的结构如图3 所示。在生成初始化帧之后,打包器等待R_RDY 信号的接收以依次生成下一帧。在从接收器打包器接收到R_RDY 信号后,将开始生成顺序的下一个数据帧,其结构如图4 所示。该循环持续进行,直到发送该序列中的最后一个数据帧为止。打包器轮询来自接收器的请求,以生成R_RDY。在生成空闲字期间生成就绪信号。数据序列完成后,打包器将保持空闲状态,直到要生成帧的下一个数据序列可用为止。

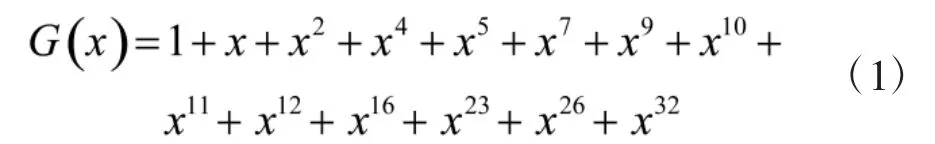

3.3 CRC 引擎模块

CRC 是紧随数据字段之后的4 Byte 字。此CRC字段用于在接收方检查帧的数据完整性。SOF 和EOF 分隔符不包括在CRC 计算中。

通常将CRC 计算为原始传输位到标准多项式的模2 除法的余数。用于计算CRC 的标准多项式,如式(1)所示。

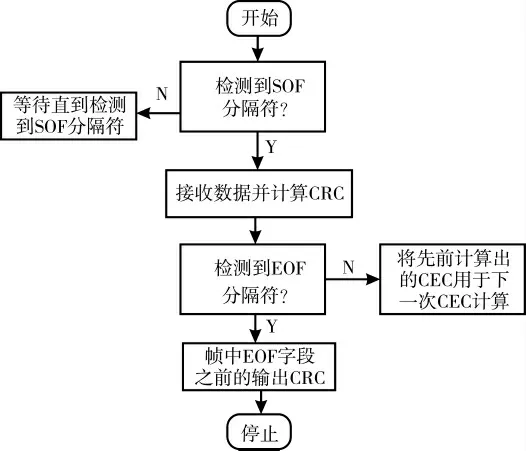

并行CRC 计算方法用于CRC 计算。FC_AE 帧中CRC 计算的机制如图7 所示。

图7 CRC 计算

在检测到SOF 分隔符后,CRC 引擎将根据SOF分隔符之后的32 位数据开始计算CRC。为标头和数据字段计算CRC。根据当前计算的CRC 和帧中的下一个32 位来计算下一个CRC 位。重复此过程,直至检测到EOF 分隔符。在检测到EOF 定界符后,CRC 引擎将停止计算CRC 的过程,并生成最终的CRC 值。最终的CRC 值紧随数据字段之后和EOF字段之前。

3.4 编码和序列化

通过光纤通道传输的数据以8b/10b 编码格式进行编码。Xilinx MGT 模块中的8b/10b 编码器用于实现编码机制。8b/10b 编码器每8 位数据生成10 位数据。32 位数据以及4 位特殊字符指示符作为编码器模块的输入。转换器将32 位数据编码为40 位数据。转换后的数据被馈送到串行器模块,该模块将并行数据输入转换为高速串行数据。

4 实验与分析

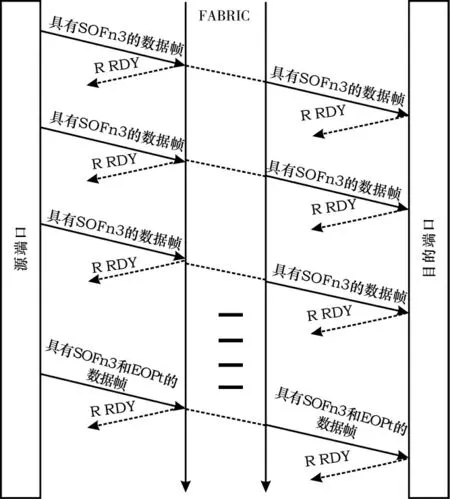

本节介绍通过基于光纤通道的帧在两个端口之间的通信机制。

实现的设计协议序列处理如图8 所示。源将初始帧发送到光纤网。在检查Frame 标头中的目标ID后,Fabric 会将框架路由到相应的目标端口。基于结构缓冲区中用于接收帧空间的可用性,它以R_RDY基本信号进行响应。类似地,目标端口根据目标端口中缓冲区的可用性以R_RDY 信号响应光纤网络。接收到源端口的R_RDY 信号后,它会将其帧结构如图4 所示的数据帧发送到结构,结构将帧发送到目标端口。

图8 协议顺序

如果源端口中没有任何数据或目标端口尚未准备好接收数据,则端口之间的通信将暂停。源端口以终止帧类型发送序列中的最后一帧,以指示序列中的最后一帧。

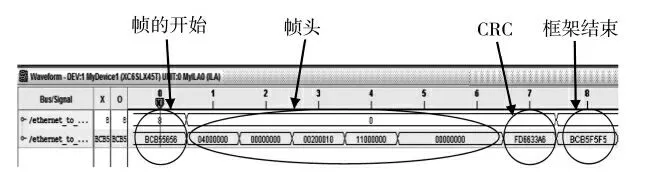

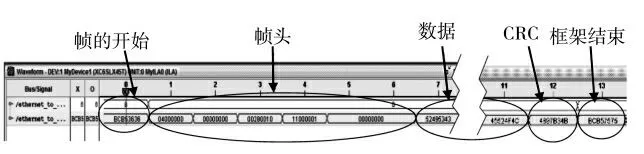

图9 和图10 显示了用于协议实施的工具捕获的样本帧。

图9 显示了为实现协议而生成的初始化帧,该帧开始了端系统之间的通信。起始帧定界符值为“BCB55656”,这表明生成的帧是初始化帧。帧结束定界符为“BCB5F5F5”,表示帧的正常结束。

图9 初始化框架

图10 数据框

图10 表示用于协议实现的数据帧,该协议帧结束了系统之间的通信。结束帧中的开始帧分隔符是“BCB53636”,它表示正常的开始帧。分隔符的末尾是“BCB57575”,它指示终端系统之间的通信终止。

5 结论

本文提出了一种基于以太网的航空电子环境数据协议的设计方法。该方法在FPGA 平台端系统中实现传输,具备并发执行能力,同时考虑了错误检测机制,以确保在终端系统中接收到数据的完整性。该协议在数据传输方面表现出极大的优势,具有高速、并发性的特点,特别是在高速应用中,经测试,协议中的数据传输速度约为1 Gb/s。其实验结果表明这是一个高效经济的方法。