基于CORDIC的成像声呐加权系数实时生成方法研究

2021-01-08夏伟杰凡志邈

刘 雪,夏伟杰,凡志邈

(南京航空航天大学电子信息工程学院,江苏南京 210016)

0 引 言

成像声呐在海洋资源开发和海洋防卫等方面有着重要的意义。因其具有作用距离远、能够直观显示观测区域状况和识别目标等特点,被广泛地应用于军事、经济领域。在成像声呐系统[1-3]的设计过程中,为了实现对目标更为细腻的刻画,系统的角度分辨率和距离分辨率指标往往都很高。成像声呐的接收阵列结构对系统性能影响巨大,且接收阵列结构决定着声呐信号处理算法的选择。线阵作为一种经典的阵列结构,在水声设备等相关领域有着广泛的应用和研究[4-5]。传统成像声呐多采用预存固定加权系数的方法进行波束形成[6-8],虽然运算复杂度小,但需要预存大量的系数;在线列阵宽带多波束形成技术中,存储一个声速下的固定加权系数,便已占用了44%随机存储器(Random Access Memory,RAM)资源。可见预存储方法对系统存储能力的要求非常苛刻,亟需引入实时生成的方法来解决该问题。目前已有学者将CORDIC算法引入成像声呐波束形成算法中。杨长根等[9]采用CORDIC算法实现扇形变换和复数求模运算,陈朋等[10]在三维声呐频域波束形成算法中利用 CORDIC直接实现复数的相位旋转功能,马超[11]设计了一种基于CORDIC的快速傅里叶变换(Fast Fourier Transform, FFT)处理器,用于声呐波束形成。此外,在其他工程应用的FPGA实现中也引入了CORDIC,王韬等[12]在移动通信的梯度跟踪算法现场可编程门阵列(Field Programmalble Gate Array, FPGA)实现方案中,引入CORDIC算法实现三角函数的计算。受前述文献中CORDIC算法的不同应用启发,本文提出了一种基于CORDIC的实时生成加权系数算法,以解决硬件中RAM资源占用过多的问题。

本文在研制便携式微小型宽带多波束成像声呐背景下展开,围绕实时生成加权系数的FPGA实现方法进行研究,以缓解FPGA中RAM的资源消耗问题。本文的成像声呐相关技术指标为:量程120 m,视角 120°,中心频率 720 kHz,带宽 100 kHz,波束数512,波束间距0.23°,量程分辨率0.8 cm,最高帧率20 Hz。

1 成像声呐加权系数分析

1.1 线列阵波束形成理论[13]

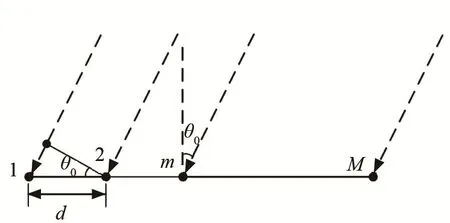

如图1所示,等间隔线列阵由M个相同的阵元1,2,…,m,…,M组成,阵列间距为d,各阵元的接收方向图相同,幅度加权系数为Ak(k=1,2,…,M)。

图1 基元间隔相等的线列阵Fig.1 A linear array of equally spaced elements

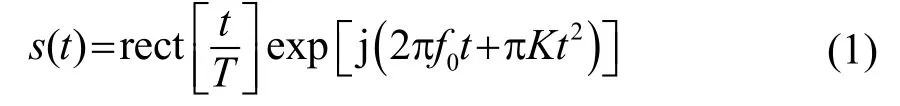

本文使用的声呐发射基阵是由 64个阵元组成的,这些阵元以弧形排列成弧阵;接收阵为线阵,由 96个阵元组成。为获得更高的距离分辨率,本文采用线性调频信号作为发射信号,信号中心频率为720 kHz,带宽为100 kHz。在同等阵列结构条件下,窄带波束形成仅需要考虑信号来向对导向矢量的影响,而宽带波束形成还需要考虑带宽内信号频率变化的影响。故在FPGA实现时,需要采用宽带多波束形成技术。声呐发射信号的复数形式为

其中,rect[⋅]为矩形窗函数。

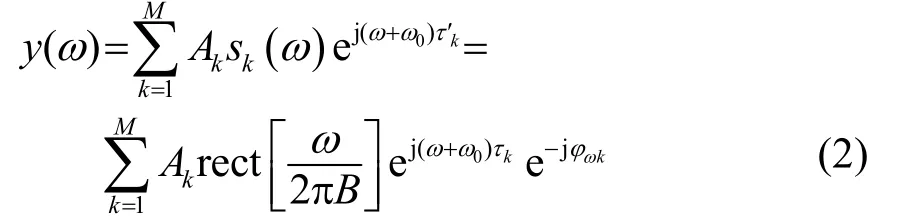

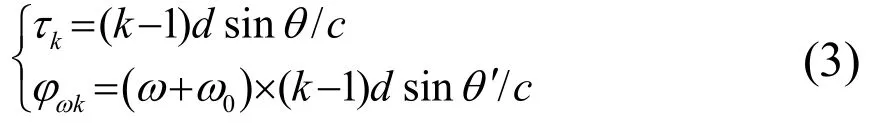

该信号遇到目标反射产生延迟τ,得到具有延迟τ的回波信号。首先对回波信号进行复解调、降采样;然后采用离散傅里叶变换(Discrete Fourier Transform, DFT)方法将时域信号变换到频域进行处理,对于变换后的频域信号进行脉冲压缩;最后,将一个或多个连续频点看作一个窄带进行处理,运用频域波束形成方法,进行逐个频点加权移相相加,得到θi方向的波束输出:

其中:sk(ω)是第k个水听器在脉冲压缩后频域的表达形式;ω0是声呐回波信号的中心角频率;τk是第k个阵元相对于接收阵第1个阵元的延时。对于宽带信号,补偿相移的时候,需要考虑频率点的不同。

ϕωk是第k个阵元信号需要补偿的相位,不同的相位补偿可以改变波束的指向,多个相位补偿方法即可形成多个波束。τk、ϕωk的表达式为

其中:c为水中声速,d为等间隔的阵元间距,本文中d=λ/2= 1.04 mm(中心频率为 720 kHz),θ为信号来向,θ'为均匀分布在120°视角范围内的第k个波束的指向角度。

Ak是第k个水听器的幅度加权系数,用于改善波束性能。采用切比雪夫加权,可以在波束宽度展宽很少的前提下降低旁瓣的宽度,从而提升波束性能。

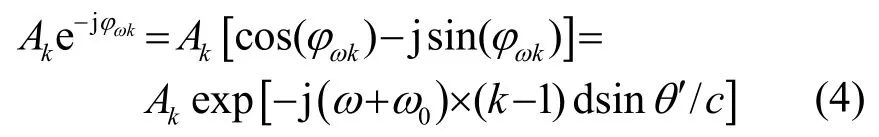

由式(2)、(3)可知,要进行计算的加权系数为

其中:θ'=(i−1)×q0−π/3,i=1,2,…,512,q0为波束间距,q0=(2π/3)/511。

1.2 预存储式生成方法

为了使用FPGA实现1.1节线列阵频域宽带多波束形成技术[14-16],首先需要使用Matlab软件将加权系数计算出来。对于宽带多波束形成,每个频点的加权系数都需要单独生成。本文基于 64频点的脉冲压缩结果,每 96个通道进行波束形成,则一组加权系数就是一个96× 64的二维数组。如要产生512个波束,则需要3 145 728个加权系数。

由于上述加权系数数量较大,已超出本文FPGA芯片选型的RAM容量,为了降低FPGA的存储压力,将逐频点(64点)补偿的方法改为划分为8个子频带的方式[17],其理论仿真及硬件实现已经验证了采用8个子频带的方式进行补偿几乎不会对波束形成结果有任何影响。因此,最终需要存储1 572 864个加权系数。

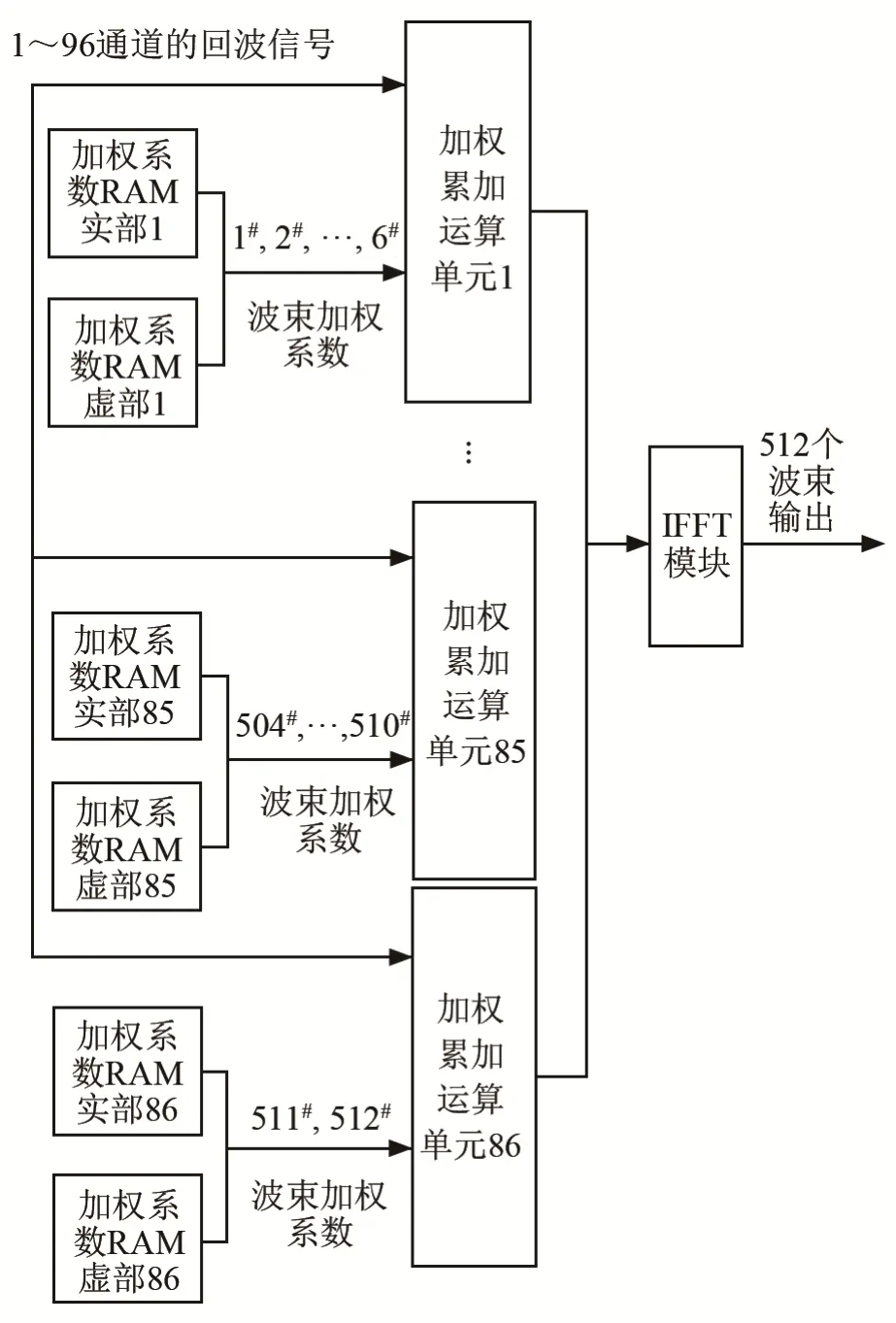

在 FPGA中使用上述加权系数时,需要在FPGA实例化若干个RAM,然后将加权系数存储进去,以便于在波束形成时可以直接从RAM中读取加权系数并与脉冲压缩后的通道数据相乘,最后进行逆傅里叶变换(Inverse Fast Fourier Transform,IFFT)来实现多波束的产生。FPGA实现流程如图2所示。

图2 现有预存储式方法的FPGA实现流程Fig.2 FPGA implementation process with the existing pre-storage method

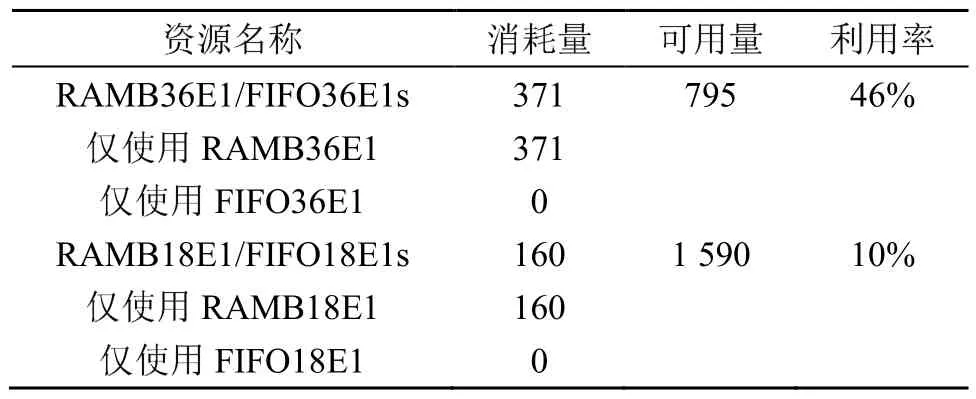

图2中采用预存储式生成方法,将Akcos(ϕωk)与Aksin(ϕωk)分别存储在两个系数RAM中,形成1组波束在1种声速下的实/虚部加权值。每个RAM的存储深度为 6 144,每个波束形成需预存波束加权系数矢量实际所需存储空间为6144× 2× 16 bit= 196 608 bit=24 kB,整个系统所占用 RAM 空间大小为24 kB× 86≈ 2 064 kB。资源消耗报告如表1所示。

表1 现有预存储式生成方法的资源消耗报告Table 1 The resource consumption report of the existing pre-storage method

2 基于 CORDIC的加权系数实时生成方法

2.1 实现方法

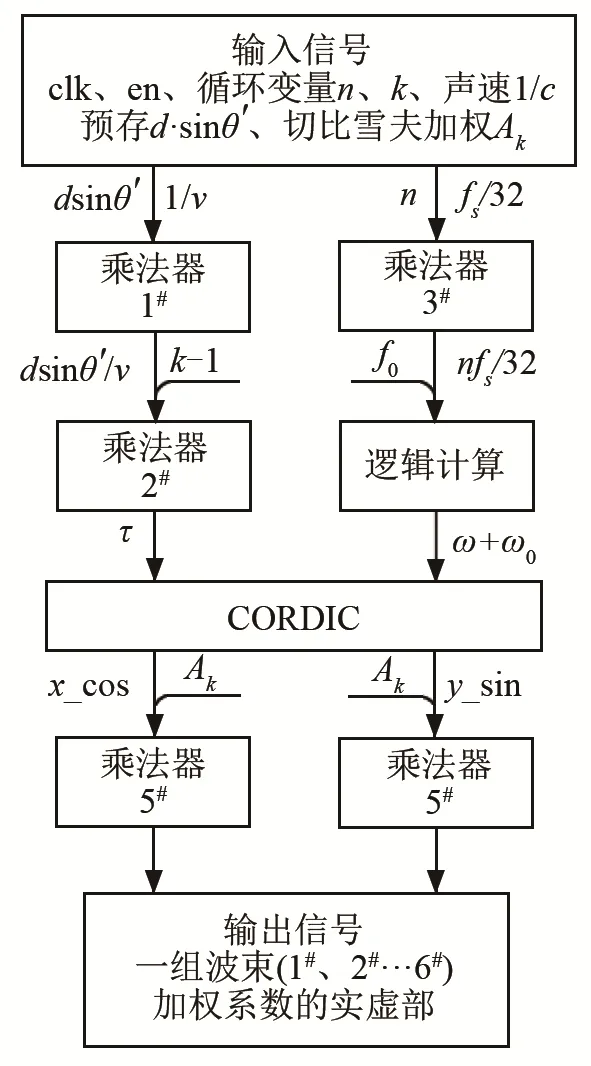

在FPGA中实时完成1.1节中式(3)的计算,不仅涉及到加减乘除四种运算,还涉及到sin函数、exp()函数这类三角函数。对于乘法使用乘法器实现,对于所有的除法,我们将其转换为对应乘法进行运算。sin()函数可以直接用CORDIC IP核计算得到[11],而exp()函数可以借助于欧拉公式将其转换为cos()和sin()运算,也使用CORDIC IP核计算得到。具体实现

步骤如下:

(1) 控制循环变量

加权系数中涉及到频点n、通道数k、波束数目i三个循环变量;FPGA中可以控制n的变化与时钟clk同步,n增加到64时,k自增1,k增加到96时,i自增1,以此往复循环。

(2) 计算τ'

由1.1节可知:τ'=(k−1)dsinθ'/c。

ⓐ 预存波束角度

由于d是一个常数,可以使用Matlab软件计算出512个dsinθ',将其分别存储在86个RAM中,深度为6,这样可以避免使用FPGA计算sinθ'时逻辑资源不够用的情况出现。

ⓑ 调用乘法器

dsinθ'的值在上一步已经得到了,避免使用除法器,我们可以采用上位机下发声速的倒数1/c,在FPGA中调用两次乘法器,即可计算出τ。

(3) 计算exp中的常数

在FPGA程序中我们定义成phase变量l来表示exp括号中的相位值,同样调用两次乘法器即可计算出相位值。

(4) 计算exp

根据欧拉公式,我们将相位值输入到CORDIC中,即可得到加权系数的实部和虚部。

CORDIC IP核要求输入值必须为−1~1之间的数值,但是相位值却不是处于−1~1之间,如果将相位值直接输入到CORDIC中,超出有效输入范围的值对应的输出是无效的,因此导致 CORDIC输出出现部分正确、部分不正确的情况,为了将所有的值缩放到−1~1之间,需要将相位值的高两位使用高第三位的值进行填充,即:scale_phase={phase[17],phase[17],phase[17],phase[16:0]},然后相位的前三位作为定点数的整数部分,后面 17位作为小数部分即可,得到scale_phase作为CORDIC的输入相位。

(5) 切比雪夫加权

最后调用两个乘法器,将步骤(4)的结果与切比雪夫幅度加权系数进行相乘,得到最终的波束加权系数。

综上,基于CORDIC实时方法生成加权系数的FPGA实现流程如图3所示。其中,clk为该模块的时钟信号,en为使能信号,v为实时声速,fs为采样频率,x_cos为cordic ip核的输出的余弦值,x_sin为cordic ip核的输出的正弦值。

图3 基于CORDIC的实时权系数生成的FPGA实现Fig.3 FPGA implementation with the CORDIC based dynamic weight generation module

本文共需要86个上述模块完成512个波束形成加权系数的计算。

2.2 资源消耗对比

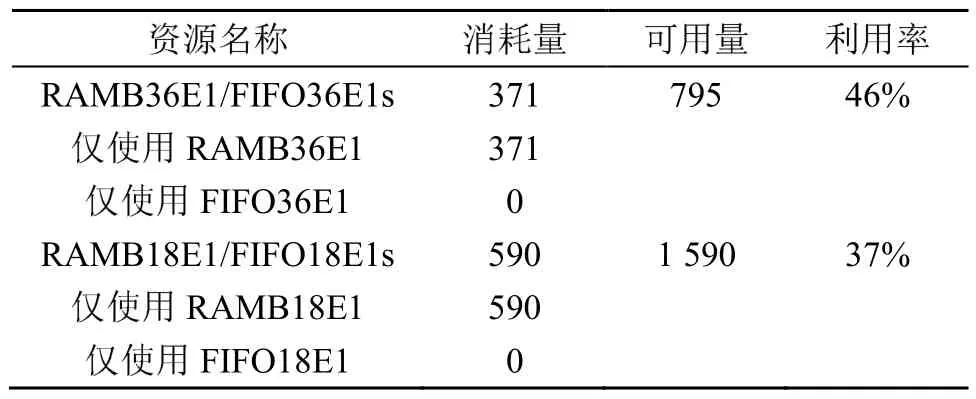

采用 CORDIC实时生成方法的资源消耗报告如表2所示。

表2 基于CORDIC实时生成方法资源消耗报告Table 2 The resource consumption report of the CORDIC based real-time generation method

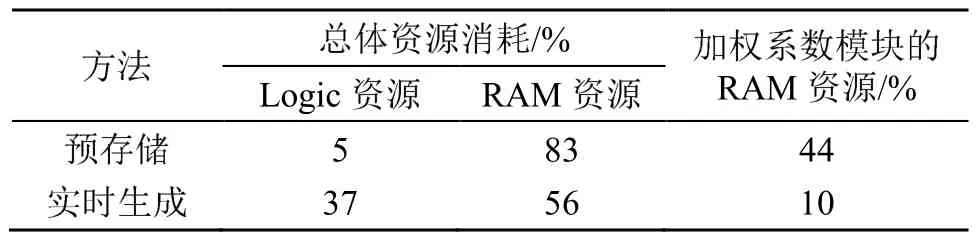

由前面的仿真实验分析,表3给出了两种方法的资源消耗对比。

表3 两种权系数生成方法的资源消耗Table 3 Comparison of resource consumption between the two generation methods of weight coefficients

3 结 论

本文提出了一种基于 CORDIC的成像声呐加权系数实时生成方法,该方法用逻辑资源代替存储器资源,改进了预存储式生成方法。经过综合、布局布线后,显示整体系统模块消耗的逻辑资源增加了32个百分点,RAM资源占用降低了27个百分点,有效地均衡了两种资源的利用率。对于波束加权系数模块的RAM资源占用率。在原有基础上了降低了77%,很大程度节省了FPGA的资源。