LHAASO-WFCTA读出电子学系统架构设计

2020-12-04张进文张寿山胡刚菱杨朝文

张进文,周 荣,张寿山,李 尧,熊 浩,胡刚菱,杨朝文

(1.四川大学物理学院, 成都 610065; 2.中国科学院高能物理研究所, 北京 100049)

1 引 言

大型高海拔宇宙线观测站(Large High Altitude Air Shower Observatory,LHAASO)是我国“十二五”规划中的重大科学项目,该观测站站址修建在四川省甘孜州稻城县的海子山上,平均海拔4 400 m[1-2]. LHAASO使用了复合探测的设计方案,由多种探测器阵列共同构成,包括电磁粒子探测器阵列,水切伦科夫探测器阵列,广角切伦科夫望远镜阵列[3-4]. 广角切伦科夫望远镜阵列(wide field of view Cherenkov telescope array,WFCTA)用来探测大气簇射时产生的切伦科夫光和荧光,使用了可移动的设计,方便根据探测需求进行不同的布局,每台望远镜有1 024个硅光电倍增管(silicon photomultiplier,SiPM),视角为0.5°. 为了读出1 024个通道的数据,我们需要设计一套读出电子学系统,目前已有的读出电子学方案,如LHAASO的电磁粒子探测器阵列(ED)或者水切伦科夫探测器阵列(WCDA),采用无触发的方式[5-6],直接对每个通道的时间信息和电荷信息进行测量,然后把各通道的数据包上传到服务器,离线进行事例分析. 而望远镜不仅仅需要获得事例的时间和电荷信息,各个通道的波形信息包含了宇宙线物理的相关信息,也需要被记录下来. 按单通道数据量1 024 bit,且单道触发率为10 kHz计算,1 024通道就需要10 Gbit/s的带宽才可以将数据全部传出. 因此,ED或WCDA的读出电子学设计对WFCTA望远镜来说并不适用,需要开发一套新的架构,实现事例数据的在线挑选. 设计思路为:采用前端电子学联合后端触发电路的方式,在前端电子学上实现第一级触发:判别着火通道,然后在触发电路上实现第二级触发:根据着火通道的位置判别是否事例触发. 与无触发的方式相比,可以通过对事例的在线判别,过滤掉噪声数据,减少数据量,并且前端电子学只需要将着火通道的位置信息发送到触发电路上,而不用将通道的全部数据都发送到触发电路上进行事例判别,这样又减少了前端电子学和触发电路之间的数据量,使得系统的带宽得到充分利用. 为了兼容记录切伦科夫信号和荧光信号的波形,考虑到荧光信号是μs量级,在波形获取时使用4点压缩方式,将模数转换器(analog to digital convertor,ADC)采样点的相邻4点累加起来作为波形点,这样每个事例波形包含28个波形点,覆盖2.24 μs的宽度. 根据WFCTA项目需求,读出电子学的主要指标如表1所示.

表1 读出电子学主要指标

2 WFCTA读出电子学系统

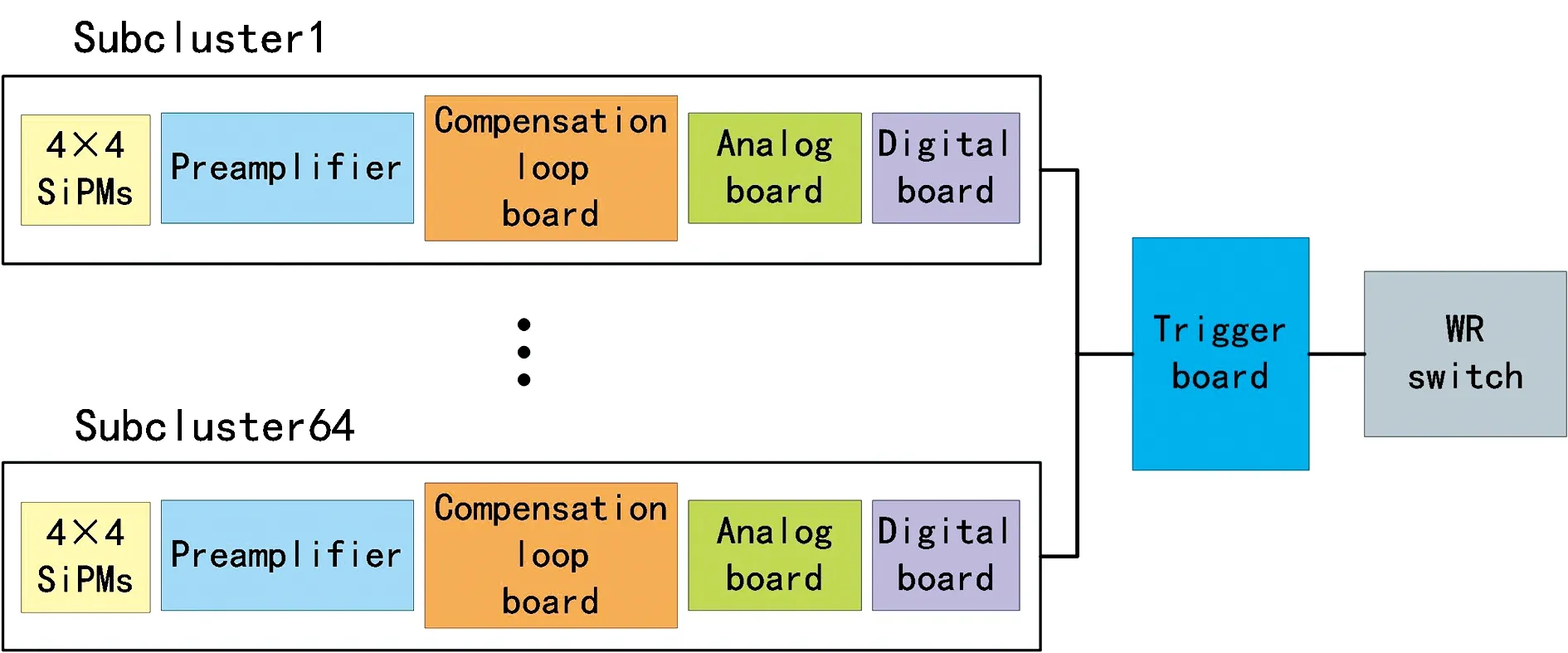

读出电子学的硬件设计分为两部分:子模块和触发电路[7]. 如图1所示,读出电子学由64个子模块和一块触发电路组成. 每个子模块由4×4的SiPM阵列、前置放大电路[8]、温度偏压补偿电路[9]、模拟电路[10]和数字电路[11]组成.

图1 WFCTA读出电子学框架Fig.1 Framework of the WFCTA readout electronics system

SiPM阵列将收集入射的切伦科夫光或荧光,前置放大电路把来自SiPM的电流信号转化成为电压信号,以供后续电路处理. 模拟电路用来处理前置放大电路的输出信号,对信号进行放大,分为高低两种增益,覆盖3 200倍的动态范围. 温度偏压补偿电路的作用是读取SiPM的温度信息,并向SiPM提供所需高压. 数字电路的作用是对模拟板的信号进行数字化处理和触发判选. 触发电路负责对事例数据进行筛选和汇总.

2.1 在线触发架构

子模块读出电子学的结构如图2所示,4×4的SiPM阵列与前放板的输出信号半高宽为42 ns,由模拟板进行处理,子模块包含两块模拟板,分别处理8路信号,为了满足测量10~32 000 P.E.的动态范围,模拟板采用高低增益设计. 数字电路上使用了两片采样率为50 MHz,12 bit的AD9249对模拟信号进行数字化处理,并且使用Spartan-6系列的现场可编程门阵列(Field Programmable Gate Array,FPGA)对串行数据进行解串,解串后的原始采样点(20 ns/bin)会流入FPGA开辟的两条线形缓存中,一条线性缓存用来计算单道触发,使用宽度80 ns的积分窗口逐点滑动,每滑过1.6 μs就找出积分窗口的最大值,然后将该值扣除基线,再分别与单道阈值和记录阈值进行比较[12]. 如果过单道阈值则单道触发,相应单道触发标志位为1,如果过记录阈值则记录标志位为1. 单道标志用来对单通道的触发进行判断,而记录标志则用于判断单通道数据是否应该被保留记录. 另一条线性缓存用来进行波形压缩,原始采样点会进行4点求和,和值被存在线性缓存中,事例获取模块将直接从该缓存中获取波形数据. 一个子模块的单道触发信号由16 bit单道触发标志组成,每个bit分别代表相应的SiPM通道是否过单道阈值.

图2 WFCTA子模块读出电子学框架Fig.2 Framework of the WFCTA subcluster readout electronics

图3 WFCTA读出电子学在线触发逻辑框架Fig.3 Framework of the WFCTA readout electronics online trigger logic

每个子模块的单道触发模块将会把16 bit的单道触发信息串行发送给触发电路,如图3. 触发电路上使用8个FPGA(FPGA1-8)对单道触发信号进行汇总,每个FPGA分别汇总8个子模块传来的单道触发信息. 由于进行事例触发判选的FPGA9plus与FPGA1-8之间的管脚有限,所以在FPGA1-8上对单道信息进行汇总,把两个子模块的单道信息合并为32 bit,再串行发送到FPGA9plus上,这样FPGA1-8与FPGA9plus将分别有4对差分线用来传输单道信息. 单道信息的传输是流水线式的,子模块每1.6 μs会向触发电路的FPGA1-8发送一次单道触发信息,代表当前1.6 μs的窗口内单道是否触发,FPGA1-8每1.6 μs向FPGA9plus发送一次汇总后的单道触发信息,FPGA9plus每1.6 μs会判断收到的1 024 bit单道信息是否满足事例触发条件并产生事例触发信号返回给64个子模块,当子模块收到事例触发信号后会耗时1.6 μs对触发标志进行解析. 因此,子模块从发出单道触发信号再到接收事例触发信号耗时4个1.6 μs,合计6.4 μs. 由于触发信号传递产生的延迟,子模块上的先进先出队列(First in First Out,FIFO)至少需要可以容纳4个事例,而子模块上FPGA的资源足够容纳16个事例,可以满足需求. 如图2所示,如果事例触发,则子模块中的事例获取模块将从数据缓存中取出事例数据存入FIFO中,在子模块上同一个事例的各通道数据都是固定长度的,读取固定长度数据即可将同一个事例打包在一起,然后通过数据发送模块发送给触发电路. 子模块的温度偏压补偿电路用来获取SiPM的温度数据并为其设置高压,SiPM的温度和高压等状态数据将被发送到数字电路上,数字电路上使用FIFO对状态数据进行缓存,然后经过数据发送模块传输给触发电路.

2.2 事例获取架构

子模块上的数据发送模块将使用1对差分线将事例数据和状态数据串行发送到触发电路FPGA1-8上,如图4所示. 每个FPGA分别接收8个子模块的数据,并同时依据记录标志位去挑选需要保留的通道数据. 然后将它们汇总后再经过1对差分线串行发送给FPGA9. 小白兔(white rabbit,WR)是基于以太网技术而改进的全数字频率分布和时间同步技术[13],可以提供任意数量节点间频率锁相及亚纳秒级时间同步. WR交换机通过单模光纤与触发电路上的WR节点相连,为望远镜提供统一的参考频率和时间,FPGA10上的WR节点将解析出WR交换机传来的国际原子时(temps atomique international,TAI)并提供相应的秒脉冲(pulse per second,PPS). 事例时间由粗时间和细时间组成,粗时间为TAI,计数周期是秒,细时间统计由FPGA9上的时间获取模块完成,FPGA9使用50 MHz时钟对细时间进行计数,时间精度为20 ns. FPGA9上事例数据汇总模块使用8个FIFO分别对FPGA1-8传来的数据进行缓存,并与事例时间一起打包后发送给DDR3 SDRAM进行存储. DDR3 SDRAM选用了Micron公司的MT41J64M16-15E,缓存容量为1 Gbits. FPGA9上的事例数据发送模块将从DDR3中读取数据并发送给FPGA10. FPGA10使用FIFO对数据进行缓存然后使用TCP/IP协议经WR交换机上传到服务器.

图4 WFCTA读出电子学事例获取逻辑框架Fig.4 Framework of the WFCTA readout electronics event acquisition logic

3 实验室测试

3.1 波形获取

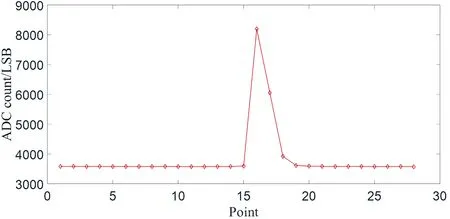

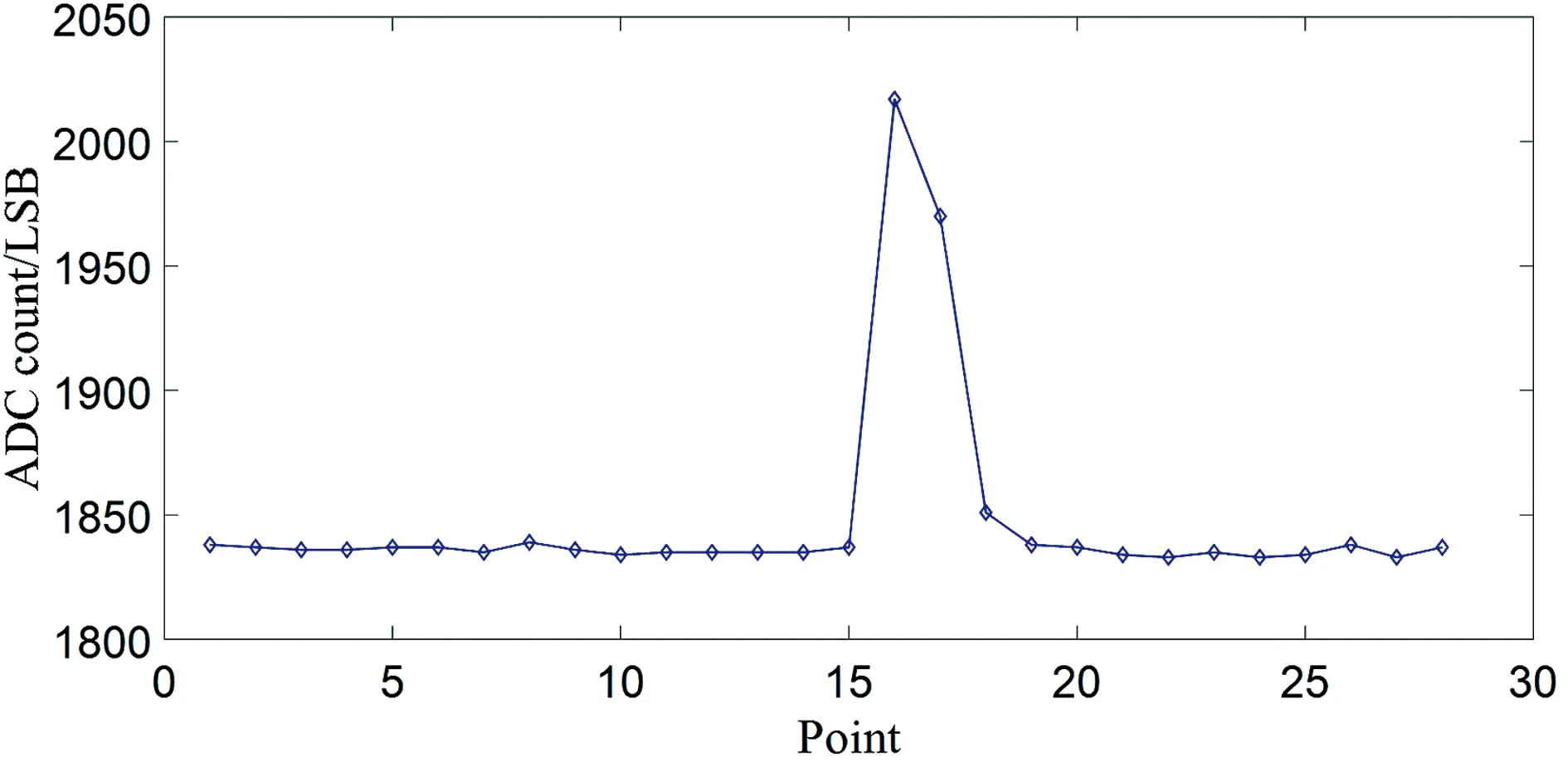

RIGOL(DG4102)信号发生器产生半高宽为42 ns的波形代替前置放大电路的输出信号,该信号经过模拟电路放大后进入数字电路,进行波形获取. 我们可以从获得的波形中计算出信号的电荷量,信号的电荷量与SiPM产生的光电子数目成正比. 实验室中自行研制的扇出电路用来将该信号扇出到每一个子模块,子模块的数据将会被触发电路接收并由WR交换机发送到上位机,使用Matlab对数据进行处理. 子模块一个通道的高低增益波形如图5和图6所示. 为了在线压缩数据量,波形的每一个点都代表了4个ADC采样点的和,每个ADC采样点是12 bit,不做压缩时,4个采样点总共48 bit,进行压缩后仅占14 bit,并且波形的电荷量和压缩前是一样的. 图中波形由28个波形点组成,总共代表112个ADC采样点,合计2.24 μs.

图5 高增益通道波形Fig.5 Waveform of high gain channel

图6 低增益通道波形Fig.6 Waveform of low gain channel

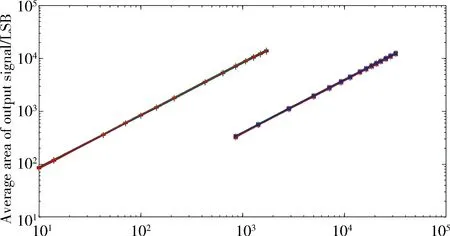

3.2 动态范围和高低增益比

用信号发生器产生不同幅度的波形来测试读出电子学系统的动态范围,图7显示了电荷测量结果,动态范围可以覆盖10~32 143 P.E.并且高增益通道和低增益通道的重叠区从 857~1 714 P.E.. 在理论设计中,高增益通道的增益是15,低增益通道增益是0.7,因此高低增益通道间的增益比是21.4. 我们使用信号幅度为857 P.E.的信号对高低增益比进行测试,图8为1 024个通道的高低增益比.

3.3 电荷测量分辨率

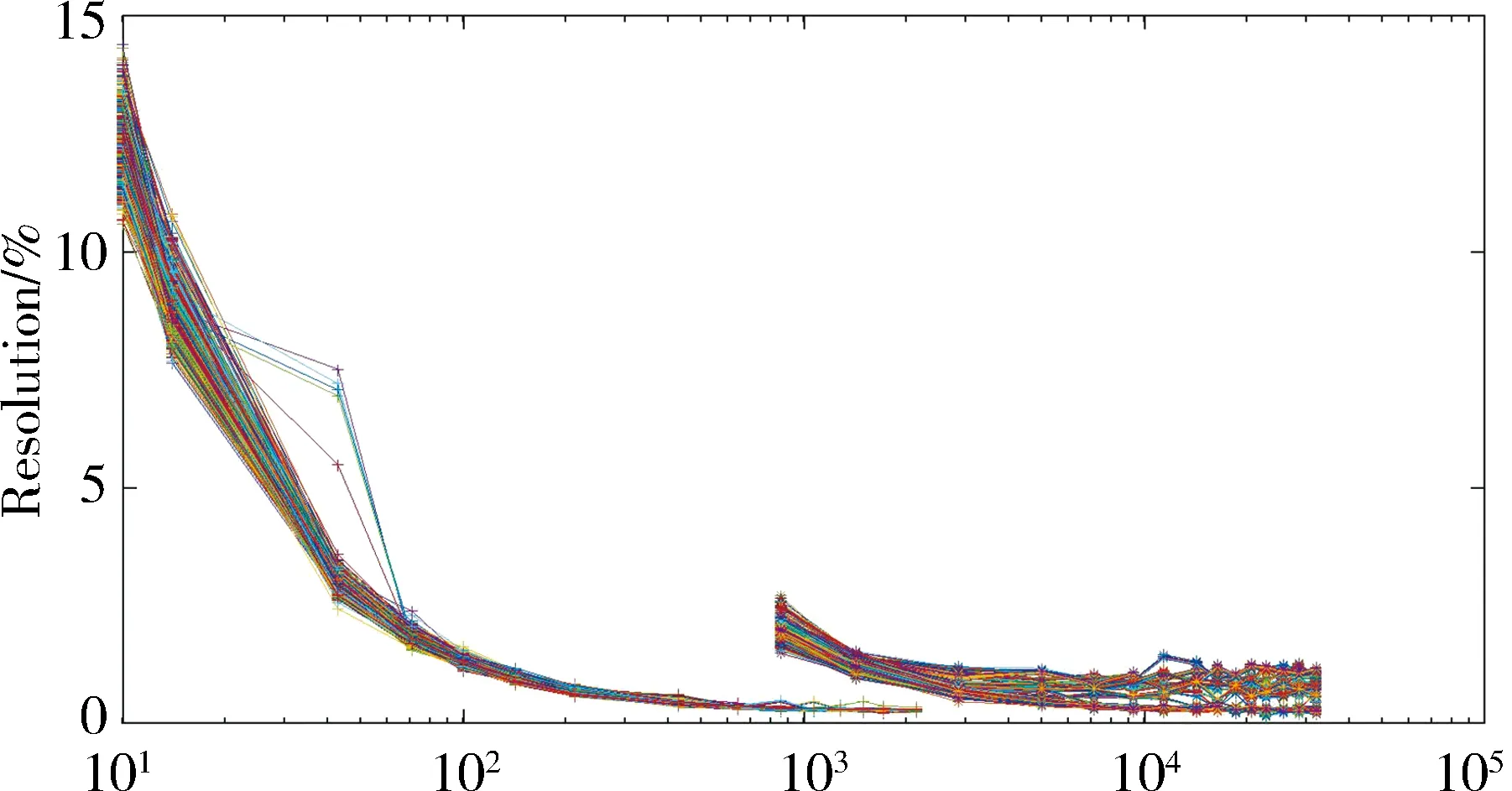

由于电子学系统的噪声和统计涨落,输出信号的波形面积会呈高斯分布,分辨率用来量化高斯分布的展宽,反映了噪声水平大小. 在实验室中使用信号发生器产生不同幅度的信号,幅度范围从10 P.E.一直测到32 143 P.E.,在每个幅度下分别采集1 000个波形,然后使用Matlab对电子学系统获取的波形面积进行统计,计算出波形面积均值和标准差,使用标准差除以均值即可得到相应幅度下的分辨率. 图9为电荷分辨率的测试结果,电荷分辨率在10 P.E.时优于20%,在32 000 P.E.时优于5%.

图7 电荷测量结果,1 024个高增益通道标记为“+”,1 024个低增益通道标记为“*”

图8 1 024个通道的高低增益比

图9 分辨率测量结果,1 024个高增益通道标记为“+”,1 024个低增益通道标记为“*”Fig.9 Resolution measurement results,1 024 high gain channels marked as “ + ” and 1 024 low gain channels marked as “*”

3.4 相对偏差

电子学系统是一个线性系统,为了衡量系统的线性程度,使用相对偏差来进行量化. 相对偏差的定义为:(测量值-拟合值)/测量值×100%,对1 024个通道的相对偏差进行测量,如图10所示,相对偏差在10 P.E.时优于5%,在32 000 P.E.时优于2%.

图10 相对偏差测量结果,1 024个高增益通道标记为“+”,1 024个低增益通道标记为“*”Fig.10 Relative deviation measurement results,1 024 high gain channels marked as “ + ” and 1 024 low gain channels marked as “*”

4 结 论

LHAASO-WFCTA望远镜读出电子学系统使用了在线触发架构:采用64个子模块先将SiPM着火信息传到触发电路,由触发电路进行在线触发判选,然后将事例触发信息回传给64个子模块的方式进行数据获取. 实验室测试表明:电子学系统可以正确获取信号波形,电荷测量的动态范围可以覆盖10~32 143 P.E. 并且高增益通道和低增益通道的重叠区为857~1 714 P.E.,高低增益比值与设计相符,电荷分辨率在10 P.E.时优于20%,在32 000 P.E.时优于5%,相对偏差在10 P.E.时优于5%,在32 000 P.E.时优于2%,指标满足WFCTA项目所需.