基于FPGA的FIR数字滤波器设计及实现

2020-11-05宋卓达王志乾李建荣沈铖武刘绍锦

宋卓达, 王志乾, 李建荣, 沈铖武, 刘绍锦

(1.中国科学院 长春光学精密机械与物理研究所,吉林 长春130033;2.中国科学院大学,北京100049)

1 引 言

在高速旋转部件的性能测试、强度及疲劳试验过程中,通常采用应变测量技术,实时采集旋转部件载荷的应变信号,进行分析和处理,为旋转部件的结构设计提供理论分析数据[1]。在应变信号采集的过程中,应变电桥的输出电压信号的变化十分微小,达到μV级。为获得高质量的低频电压信号,本文采用一种基于FPGA的FIR数字滤波器进行信号处理,在高转速、气动性复杂、震动环境恶劣的情况下,提高所采集应变信号的精度。采用软硬件协同设计技术,利用FPGA定制IP,每一个模块都能单独完成,又能轻松整合在一起形成一个系统[2]。

FIR滤波器的实质是将输入的连续时间信号按照设定的算法转换成离散时间信号的滤波装置[3],而FPGA内含丰富的IP核和LUT表结构,能够完整地将FIR数字滤波器移植到FPGA上,并且可以根据实际需求在线修改滤波器的参数,大幅缩减了产品的设计周期,并增强应变信号采集系统本身的集成度和灵活性。

利用可编程逻辑器件和EDA技术实现FIR数字滤波器是现代嵌入式系统信号处理环节普遍采用的手段[4],随着FPGA逻辑单元数量和集成度不断提高,可在 FPGA 上实现FIR数字滤波器的算法复杂程度、量化系数位宽、阶数等也随之提高,具有可观的发展前景。

2 系统框架

应变信号采集系统的总体框架如图1所示,整个系统分为模拟部分和数字部分。

图1 应变信号采集系统流程框图Fig.1 Block diagram of strain signal acquisition system

其中模拟部分有4个应变信号采集通道,每个采集通道包含对应变电桥的模拟信号进行预放大、调理和A/D采集,数字信号部分包括对模拟板前端电压信号偏移量修正和温度补偿控制、程控自动增益、A/D采集的读写控制和接收经过A/D采集后的信号,并对其进行缓存和处理[5]。最后将信号通过UART串行总线传输至PC端显示[6]。

3 FIR数字滤波器的设计

3.1 基本原理和结构

FIR数字滤波器为单位脉冲响应有限长序列[7],是非递归性线性时不变因果系统,对于N阶FIR滤波器输入时间序列x(n)的输出表达式为:

(1)

系统传递函数可表示为:

(2)

式中:h(n)为滤波器第级n抽头系数,x(n-i)为延时i个抽头输入。

FIR滤波器按构成形式主要有直接型、级联型、线性相位FIR滤波器等[8]。其中直接型结构如图2所示,该结构需要N个乘法器,每次采样y(n)都需要进行n次乘法和n-1次加法实现乘累加之和[9]。

图2 直接型FIR滤波器网络结构Fig.2 Network structure of direct FIR filter

对于线性相位FIR滤波器,其单位响应是对称或反对称的,即h(n) = ±h(N-1-n),利用其对称性可以简化网络结构,当h(n)为偶对称且N为偶数时:

(3)

其线性网络结构如图3所示,仅需要N/2个乘法器。FIR滤波器实际上是一个分节的延时线,把每一节的输出加权累加得到滤波器的输出[10]。本设计采用线性相位FIR数字滤波器。

图3 FIR滤波器线性相位网络结构Fig.3 Linear phase network structure of FIR filter

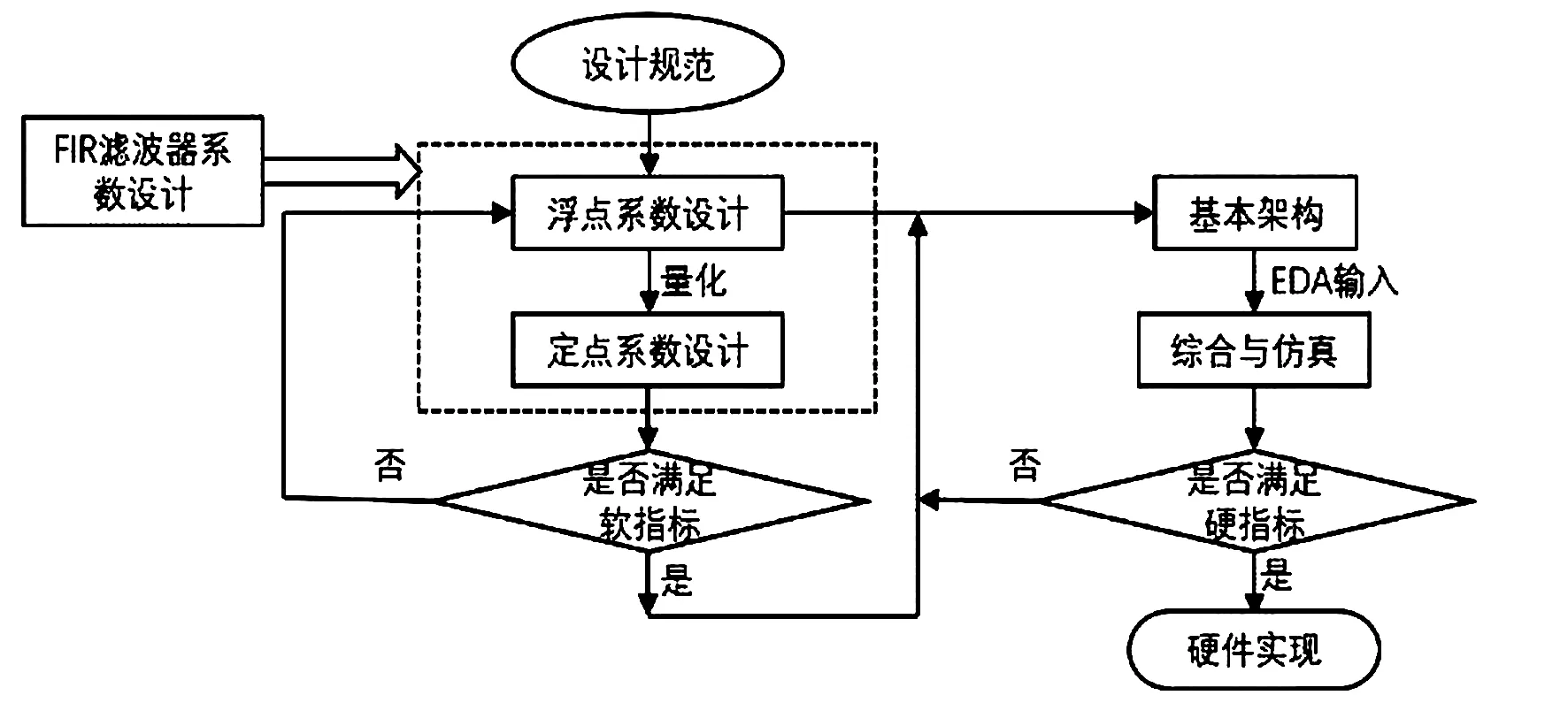

3.2 FIR滤波器设计流程

FIR数字滤波器设计流程如图4所示,整个FIR数字滤波器的设计可以分为滤波器系数设计和滤波器在FPGA上实现两个部分。利用Matlab软件设计出FIR数字滤波器各级抽头系数,并将FIR数字滤波器的功能移植到FPGA上。

图4 FIR滤波器设计流程图Fig.4 Flow chart of FIR filter design

4 FIR数字滤波器的FPGA实现

4.1 Matlab设计滤波器系数

通过使用Matalb中FDA Tool工具箱设计出一个15阶低通线性相位FIR数字滤波器,其采样频率为20 kHz,截止频率为3 kHz,长度为16位,并采用布莱克曼窗实现,将滤波器浮点系数量化为12位。运行所编辑的滤波器,并将量化后的滤波器系数写入FIRCOE.TXT文件中。滤波器设计界面如图5所示。

图5 FDAtool滤波器设计界面Fig.5 Design interface of FDATool filter

4.2 Simulink仿真滤波器输入信号

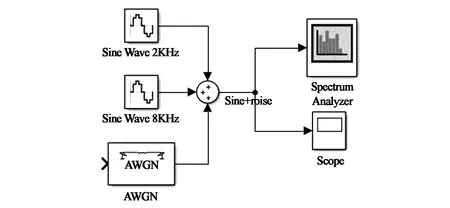

将Simulink中正弦波信号产生模块sine wave、高斯白噪声模块AWGN通过多信号叠加模块add生成一个采样频率为20 kHz的信号干扰源,并生成12位量化系数,再与2 kHz和8 kHz的正弦波信号合成作为FPGA的输入信号。信号发生模块如图6所示。

图6 合成信号发生模块Fig.6 Schematic diagram of synthetic signal generating module

4.3 IP核设计FIR数字滤波器

进入QuartusⅡ IP核设置界面,设计一个15阶低通线性滤波器,将4.2中的FIRCOE系数文件导入到Coefficient set中[11],配置好滤波器各项参数,生成FIR数字滤波器模块,并将其实例化引用。数字滤波器RTL级原理如图7所示,其中ast _sink_ data[11..0]和ast_ source _data[25..0]分别为信号输入端口和数据输出端口。整个模块只占用2 199个逻辑元,占用率不到10%。

图7 数字滤波器RTL级原理图Fig.7 RTL level schematic diagram of digital filter

5 FIR数字滤波器仿真与性能测试

5.1 FIR数字滤波器功能仿真

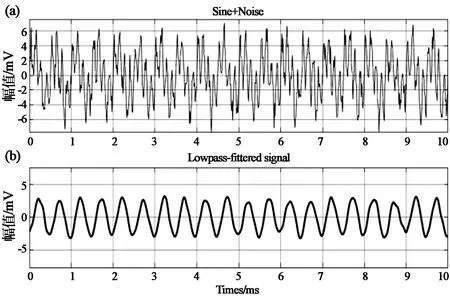

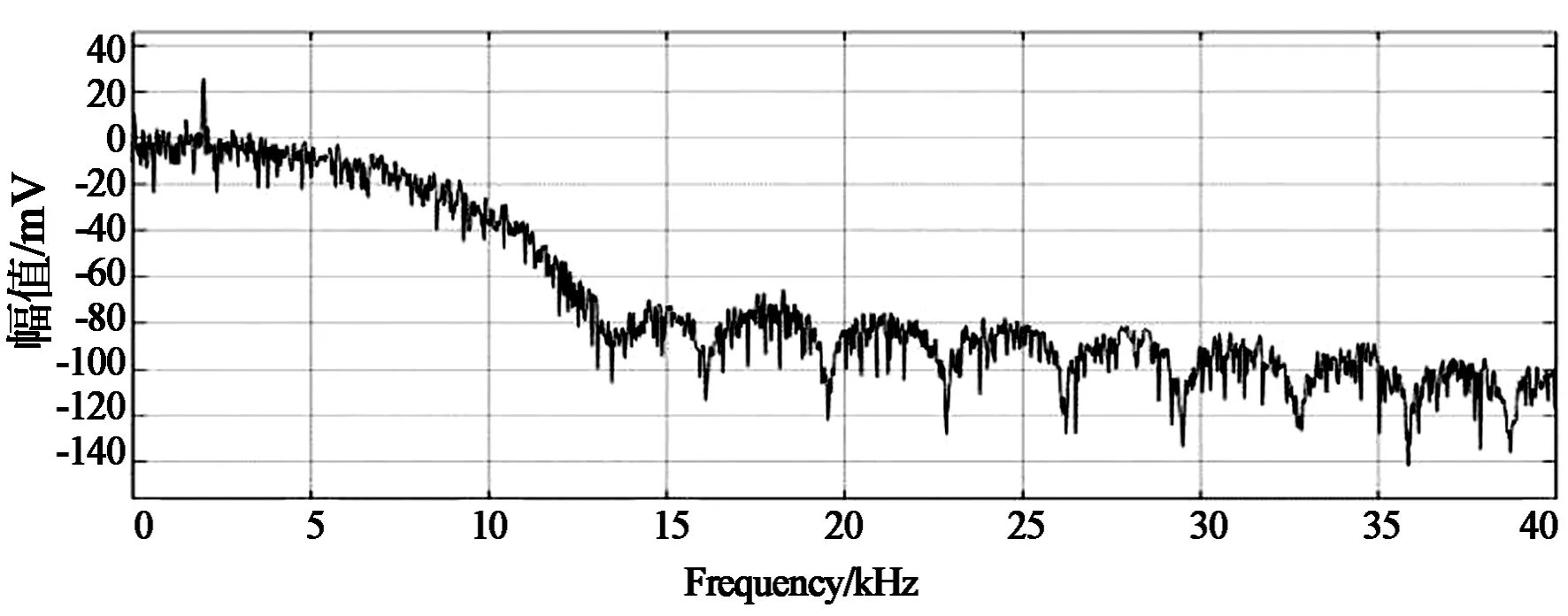

搭建FPGA与Simulink联合实时环路平台,在Simulink创建测试模块,通过测试模块产生信号,再传送到FPGA,FPGA将信号处理后返回Simulink显示[12]。首先在Simulink中创建用户板卡,配制板卡上FPGA芯片信息,本设计FPGA采用的是CycloneⅣ系列EP4CE6E22C8N。然后采用JTAG连接方式,设置JTAG接口类型、时钟信号频率、引脚号、时钟类型、复位信号引脚、复位电平等信息,并将配置的信息保存在logic_board.xml文件中。创建Simulink模型,将配置好的logic board.xml文件导入,加载RTL文件即Verilog代码文件,并将其设置为顶层文件,自动配置IO口,将数据传送到Simulink中。仿真结果如图8、图9所示。

图8 合成信号滤波前(a)后(b)时域波形图Fig.8 Time domain waveform before (a) and after (b) filtering of synthetic signal

(a)滤波前合成信号频域波形(a) Frequency domain waveform of synthesized signal before filtering

(b)滤波后合成信号频域波形(b) Frequency domain waveform of filtered synthetic signal图9 合成信号滤波前后频域波形图Fig.9 Frequency domain waveform before and after filtering of synthetic signal

由图8、图9可知,滤波后的合成信号在时域和频域上趋于缓和,毛刺噪声已经滤除,并且同时滤除了8 kHz高频信号分量,滤波后的信号已形成规则平滑的频率为2 kHz的单频正弦信号,因此,FIR线性相位低通滤波功能在FPGA上已经实现。

5.2 FIR数字滤波器性能分析

将应变信号采集系统的4个应变采集通道分别对高速旋转部件的4个点进行应变测量,并且通过串口将FIR数字滤波前后量化结果的文本文件导入Matlab中,进行数据处理,得到FIR数字滤波前后的均方差,如表1所示。

表1 FIR数字滤波前后均方差Tab.1 Mean square deviation before and after FIR digital filtering

由表1FIR数字滤波前后量化信号均方差的对比可知,经过FIR数字滤波器后,信号的均方差大幅度下降,4个通道的采集信号均方差平均下降28.5%,具有良好的滤波效果。

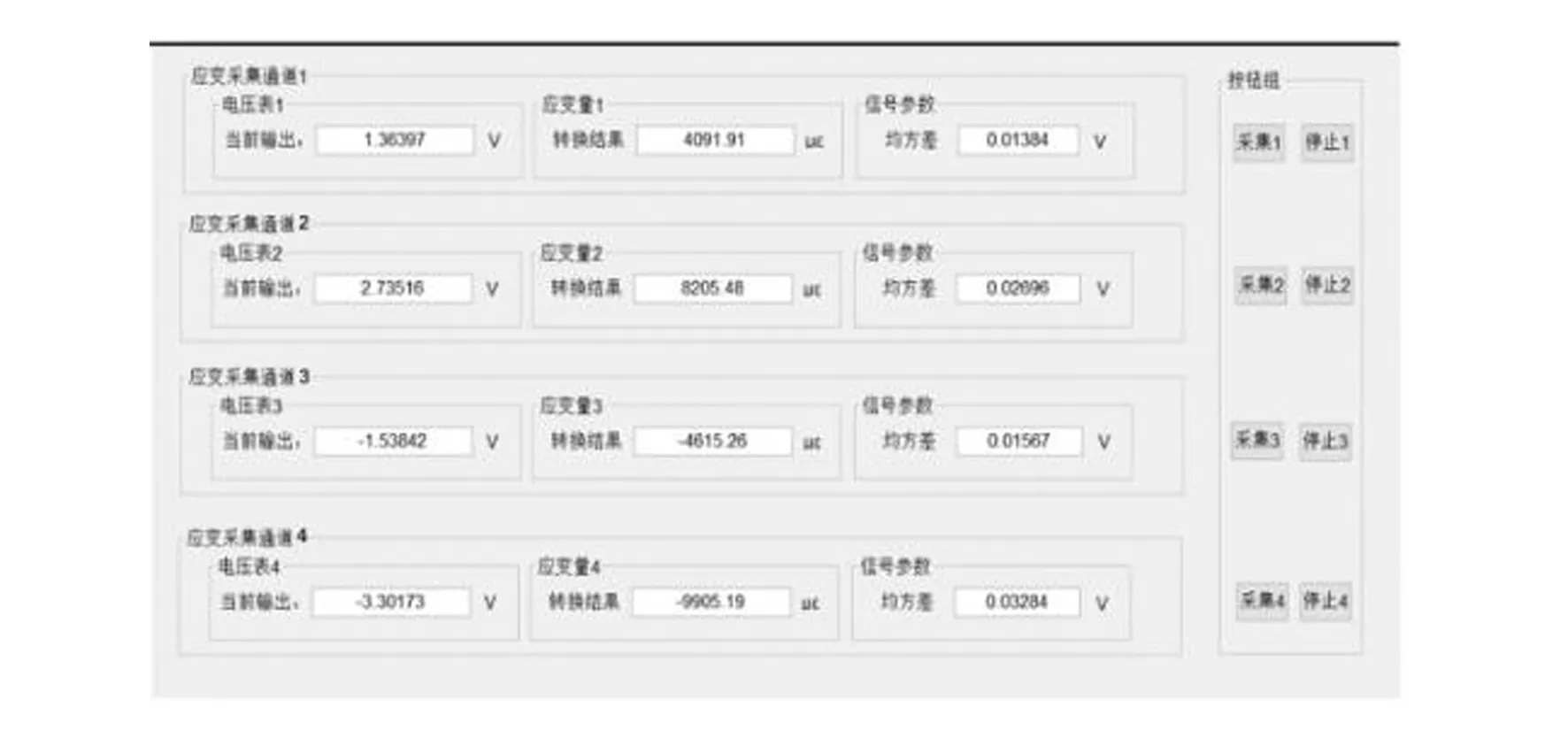

5.3 界面显示

为了能够将4个应变采集通道中的最终采样结果通过串口在PC端实时显示,使用Matlab中GUI工具箱设计出显示界面,并且通过式(4)将采样结果转化为对应的电压值。

(4)

式中:Vref为ADC参考电压、GND为输出结果为0时的最低电压,ADCReselt为采样结果,N为ADC位数。同时根据式(5),在全桥测量的情况下将电压转换成相应的应变量。

Uo=EKε

(5)

式中:E为电桥电压,K为应变灵敏系数,ε为应变量。显示界面如图10所示。

图10 界面显示Fig.10 Interface display

6 结 论

本文针对应变信号采集系统提出一种基于FPGA的FIR线性相位低通数字滤波器方案,构建了数字滤波器设计与仿真体系,最终在FPGA上实现,而且仿真系统可以任意改变合成信号的类型、数字滤波器的种类和各项参数,相比传统的通过编写testbentch脚本仿真文件导入Modelsim来实现仿真结果,简化了复杂的仿真步骤,不需要在FPGA上增添信号发生模块,同时保证了实验可靠性。通过高速旋转部件的多次应变测量,结果表明数字滤波前后量化信号的均方差下降28.5%,具有良好的滤波效果。增加显示界面,便于观察采样结果的动态变化。

对于接触式应变信号采集系统而言,将整个FIR数字滤波器的功能移植在FPGA上,增强功能的同时,系统的体积、质量、电路复杂程度均不受影响,从而不会影响直升机在飞行测试中旋翼系统的动态平衡。