基于FPGA的图像叠加和跨屏拼接融合方法

2020-11-05李少甫

万 权, 李少甫

(西南科技大学 信息工程学院,四川 绵阳 621010)

1 引 言

随着视频处理的快速发展,视频显示的方式也越来越丰富,显示设备广泛应用于调度中心、视屏监控、演出背景等,传统的单图层显示方式已经不能满足多样性显示的需求,如王明宇采用双线性融合算法实现视频源的大屏拼接[1],这种显示方式可应用在大部分多屏显示场景中,但显示界面往往只能调用一个图像源;严飞采用双三次插值算法实现了两个图层的叠加[2],但是只在一个显示屏上输出,没有对图像进行拼接处理。针对大屏拼接中不同图像源叠加的问题,本文设计了一种多功能视频拼接系统,使得每一路输出信号都支持图像叠加与图像拼接;同时允许输入多种分辨率格式,输出分辨率可以根据使用者需求进行实时调整[3]。由于双线性插值算法的画质比最邻近插值算法高,且硬件资源占用比双三次插值算法少,既能满足图像画质的要求又能满足跨屏拼接所需的多路资源要求,所以本文采用双线性插值算法作为系统的缩放算法[4-8]。

2 系统组成

2.1 基本模块

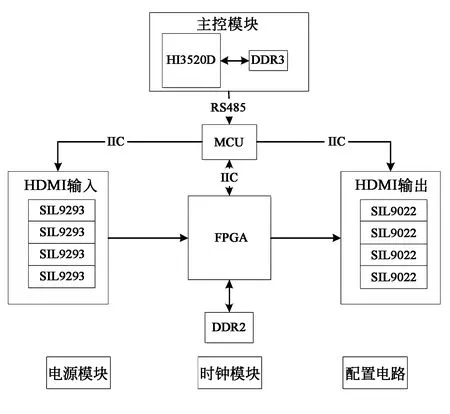

视频拼接系统包括4路Sil9293视频输入模块、4路Sil9022视频输出模块、DDR2(Double Data Rate 2)存储模块、现场可编程门阵列(Field Programmable Gate Array,FPGA)算法执行模块、Hi3520D主控模块、MCU(Microcontroller Unit)单片机模块、以及其他必要模块(电源模块、时钟模块、配置模块),系统的硬件设计图如图1所示,FPGA[9-10]型号为LFE3-70EA-6FN672C,是lattice公司ECP3系列产品,单片机型号为STM32f030-RT86。

图1 多功能视频拼接系统硬件结构图Fig.1 Hardware structure diagram of multifunctional video stitching

2.2 信号流向

Sil9293视屏输入模块通过采集外部HDMI接口输入的视屏信号,转换为YCbCr(4∶2∶2)格式[11]的16 bit位宽数据流,当FPGA收到数据流立即进行数据有效性判断,如果视频流数据判断为有效,那么将存储到DDR2中,当单片机告知FPGA需要对图像进行缩放计算时,缩放模块通过读取存储在DDR2中对应的信号源数据到RAM中,进而参与图像的缩放计算,计算结果输出到Sil9022视频输出模块,最终转换为HDMI视频信号输出。

2.3 主控模块

主控模块主要由海思的视屏解码芯片Hi3520D[12]和DDR3组成,首先通过SPI接口写入预处理程序,再通过主控板上的以太网接口连接到PC主机,在PC端可视化界面上绘制出每一路输出需要显示的图像窗口并选取信号源,之后Hi3520D产生与输出窗口对应的参数信息(起始地址、终止地址、图层显示优先级、目标显示分辨率),再通过RS485接口[13]发送到单片机,参与每一路视频输出的缩放倍数计算,主控模块如图2所示。

图2 主控模块Fig.2 Schematic diagram of system master control module

3 DDR2读写解析

3.1 数据采集与存储

一帧图像可分为有效区域和消隐区域,有效区域的长宽即为图像的分辨率,也是人眼在显示器上看到的视频区域;视屏传输采用内同步传输方式[14-15],即图像的每一行的起始和终止标志,插入到视频流中一起传输,在保证有效数据量不变的情况下,又减少了外部同步信号引脚,节约了硬件IO口资源。根据扫描方式的不同视频可分为逐行扫描和隔行扫描,它们由视频起始标志或者终止标志来区别。采用verilog语言对FPGA进行编程,按照BT1120的图像标准[16],采集有效数据的起始标志(sol_flag)和终止标志(eol_flag),同时对起始标志后的数据进行计数,直到结束标志到来时才停止。一个连续的起始和终止标志之间的计数值,即表示视频分辨率的横向值;同理对一帧数据中有效区域前的起始标志个数进行计数,即可得到视频分辨率的纵向值。

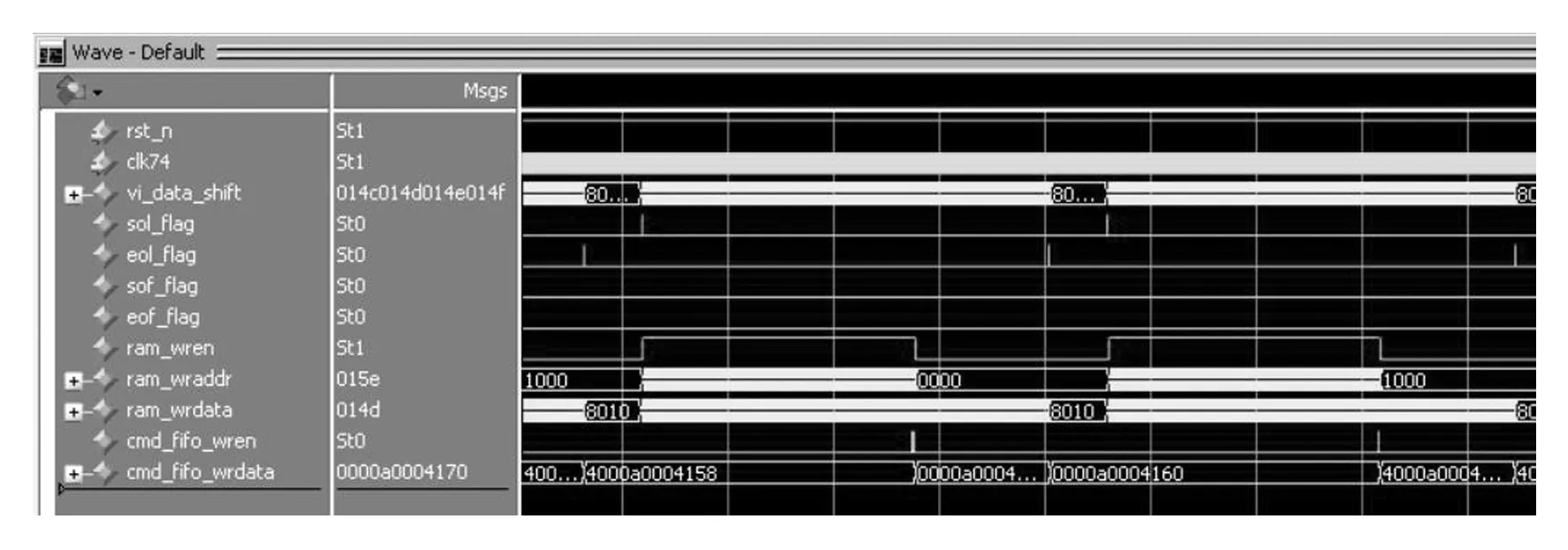

数据存储前,需要先判断视频源的输入格式。标志位由4个连续的像素点数据组成,所以采用移位寄存的方式对视频流进行连续存储,由vi_data_shift表示这4个值,当FPGA检测到一帧视频图像中有隔行扫描起始标志时,即条件(vi_data_shift[63∶0]==64'hffff00000000c7c7)成立,则认为图像是隔行扫描图像,如果不成立则视屏源为逐行扫描格式,如图3图像的起始终止标志。

图3 图像的起始终止标志Fig.3 Start and end of image

本设计采用了RAM_FIFO(Random Access Memory,First Input First Output)架构的存储方式[17],图像以行为单位进行数据缓存,通过乒乓操作使有效的视频数据写入到RAM中,当一行数据写入结束时,立即产生一个激活FIFO的写使能命令(cmd_fifo_wren),同时对输入的视频参数(当前数据通道号、当前行号、突发长度、存储DDR的起始地址)进行存储,当FIFO的“空”输出标志为低电平时,表示允许DDR2的控制模块读取FIFO中的视频参数数据,控制模块调用Diamond中固有的IP核(DDR2 SDRAM Controller)实现数据存储到DDR2的过程[18]。

3.2 读数据

双线性插值算法最少需要用两行图像数据进行插值计算,所以需要提前从内存中读取2行数据;每一个视频显示窗口,在插值计算时,为了满足读写RAM时数据操作不冲突,采取缓存4行数据的方式交叉写入[19]。使用两组RAM,每组可容纳两行的视频数据,RAM1的两行存储空间分别命名为a行和b行,RAM2的两行存储空间命名为c行和d行;当FPGA从单片机接收到读命令后,以行为单位依次从DDR2中读出对应的数据,并按照a-c-b-d的顺序循环写入两个RAM空间,如图4所示,同时读取已经写好的连续两行数据的连续两点进行缩放计算,保证了读与写之间互不影响。

图4 DDR2中一路数据存取逻辑图Fig.4 Diagram of DDR2 data access logic

3.3 提高DDR2读写效率

本设计为4个视频源的同时输入,且4个处理后的视频信号同时输出,为了满足多路信号的同时处理要求,提高DDR2的读写效率就显得很有必要,本文通过两个方面来提高内存读写的效率。其一,采用FPGA内部的时钟IP核提高读写时钟的频率,通过调节PLL(Phase Locked Loop)的输出时钟,使得读写RAM的频率高达200 MHz;其二,提高数据传输带宽,使用4组16 bit位宽的DDR2内存颗粒,通过并联方式组成64位宽的数据传输总线;又因为DDR2拥有两倍DDR内存预读取能力,故实际每个时钟周期从RAM中读/写的数据位宽为128 bit(8个像素点),如图4数据存取逻辑图。

每组RAM空间大小为4 096×16 bit,可缓存两行1 K的视频图像数据,一行数据有效像素点最多为1 920个,所以一行存储空间能够存储一行图像数据。

4 缩放步骤

4.1 新像素点计算

双线性插值算法并没有产生实际意义上的新像素值,所有新的像素值都是通过计算得到。因此,如何计算新像素值便成为实现算法的关键。双线性图像缩放算法在计算新像素值时需要有相邻两行原图像像素值作为计算依据。因此,为了保证图像的连续性,必须通过具有大容量的存储器件DDR2来缓存几帧图像数据。双线性图像缩放算法计算新像素值时需要知道缩放前后图像的横纵比值,然后再用新像素的坐标值分别与缩放倍数的横向比值和纵向比值相乘,以此来确定当前新像素在原图像中的坐标位置。考虑到直接的除法运算在FPGA中会导致严重的时序违规,采用移位除法又占用大量资源,且该除法运算没有实时性要求,即被除数与除数不会随时钟连续变化。因此可由单片机来完成视频源到目标分辨率缩放倍数的计算,计算结果再返回FPGA执行。

4.2 图像缩放解析

计算缩放倍数时,主控板通过RS485总线发送开窗所需的参数给单片机,目标显示分辨率与输入视频源的分辨率共同计算得到图像缩放倍数;FPGA实时更新所有视频源分辨率信息,单片机通过IIC总线每隔1 s时间读取一次FPGA寄存的分辨率,实时更新缩放的倍数;计算方法如下:

(1)

(2)

其中:in_width表示输入分辨率宽度,out_width表示输出分辨率宽度,in_hight表示输入分辨率高度,out_hight表示输出分辨率高度,x表示横向缩放倍数,y表示纵向缩放倍数。

(1)新像素坐标位置计算

新像素的坐标设为P′(u′,v′),该坐标点在视频源图像中对应的坐标位置设为P(u,v),用P′点的坐标与相应比值相乘即可得到新像素在视频源图像中的坐标位置P(u,v)。

P(u,v)=P(u′·x,v′·y)

(3)

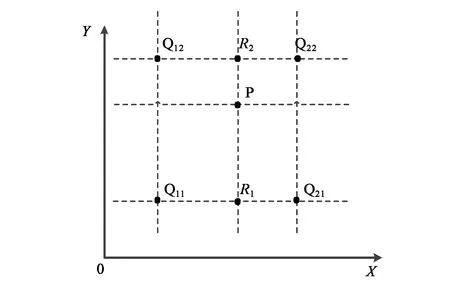

由P点的整数部分可得到它的4个相邻点Q11(i,j)、Q12(i,j+1)、Q21(i+1,j)、Q22(i+1,j+1),P点为相邻点闭合空间上的任意一点。在双线性插值算法中,像素值是由周围4个相邻点的像素值加权求和得出,如图5双线性算法原理。

图5 双线性算法原理Fig.5 Diagram of bilinear algorithm principle

(2)新像素值计算

当新像素点在源图像中的坐标位置确定后,利用这4个像素值与P点坐标小数部分对应相乘后再相加,最后得到新像素点的值[20]。

(3)乘法实现

FPGA在需要乘法运算的地方均使用FPGA内部乘法器IP核(DSP_MULT)来实现乘法运算[21]。

设f( )为源图像中像素点坐标对应的像素值,相邻点的值表示为f(i,j)、f(i,j+1)、f(i+1,j)、f(i+1,j+1),

图5中R2、R1分别为P点在上、下边界的分量,可作为计算P点的中间值,u,v为P点小数部分的值。首先计算出R1、R2的像素值:

f(R1)=(1-u)·f(i,j)+u·f(i+1,j)

(4)

f(R2)=(1-u)·f(i,j+1)+u·f(i+1,j+1)

(5)

再由横向两个点R1、R2的值计算出纵向点P的值:

f(P)=(1-v)·f(R1)+v·f(R2)

(6)

通过时钟上升沿驱动计算模块,即可输出源源不断的新视频信号。

5 条件与验证

5.1 实验条件

采用Lattice公司的Diamond软件作为程序编译平台,然后对FPGA中的各个功能子模块进行综合、布局布线。主控板通过网线连接电脑,并采用RS485总线连接FPGA执行板,如图6系统结构图。输出端口连接4个1 920×1 080分辨率的显示器。

图6 系统结构图Fig.6 Diagram of system structure

显示器以2×2的矩阵方式拼接显示,在拼接状态下满屏图像的分辨率为3 840×2 160,系统的每一个输出通道分配了两个图像显示窗口,每一个窗口可以独立处理一个图层的图像,当大屏拼接和图像叠加两种显示方式同时存在于一个输出通道时,通过单片机选择图层的优先级,高优先级的图像覆盖低优先级图像,最终以一个图层的方式输出。

5.2 仿真

编译软件集成了仿真工具Reveal Analyzer,能够实时获取工程中数据的变化,如图7所示。其中data_rdy电平为高时,表示外部视频源正在写入内存,read_data_valid电平为高时,表示视频数据从内存中读出[22],可以看出视频数据在不停地以行为单位对DDR2进行数据的写和读。

图7 DDR2读写仿真Fig.7 DDR2 read and write emulation

图像底图采用拼接的显示方法,其他3个窗口通过PC端控制可任意缩放,其中新开的窗口仍然可以实现跨屏拼接;采用4路1 080 P,频率为60 Hz的视频源作为系统的信号输入,显示效果如图8所示。此设计是在大屏拼接的基础上增加叠加图像的功能,此外当有多个信号源同时输入时,可通过开窗的方式显示多个不同的信号源。

图8 显示效果图Fig.8 Picture of show effect

实验结果表明,基于FPGA的双线性插值缩放系统,允许同时输入4路最大1 080 P的分辨率,输出分辨率最大为3 840×2 160,输出分辨率最小为50×50,对于输出的4路视频信号,每个信号允许开出2个任意缩放的窗口。FPGA消耗的LUT资源占总资源的25.06%,RAM占用总资源的36.67%。DSP计算资源占总资源的66.63%,如表1所示。

表1 FPGA资源使用情况Tab.1 FPGA resource usage

续 表

6 结 论

本文以实际市场需求为导向,针对图像的大屏拼接显示,提出了一种多功能视频拼接系统的硬件结构设计,采用乒乓操作提高数据传输的稳定性。通过加大数据传输的位宽,提高数据读写的频率,使得允许同时多路视频的输入和输出;同时单片机对输入视频的分辨率进行实时检测,当分辨率变化时,输出视频也随之动态调整,提高了系统的应用能力。在Diamond环境中对该实验进行编译与测试,结果表明,输出的4路图像都可实现图像叠加和跨屏拼接的功能,最小输出分辨率为50×50的图像,最大输出分辨率为3 840×2 160的图像,满足常规要求的同时,也满足一些特殊场景显示的需求。