基于FPGA的MEMS陀螺阵列信号采集系统

2020-10-19周中鑫张印强李丽娟

周中鑫,张印强,李丽娟,刘 琴

(南京工业大学电气工程与控制科学学院,江苏南京 211800)

0 引言

MEMS(micro electromechanical system)陀螺仪与其他类型的陀螺仪相比,具有体积小、价格低、质量轻和集成度高等优点,已经在工业和汽车等领域得到广泛应用[1-3]。但其精度较低,不能满足高性能要求,而基于数据融合技术的MEMS陀螺阵列可以大幅度提高测量精度,其数据信号的实时采集是惯性导航系统的关键部分。现今采集系统的控制器大多使用单片机或DSP,完成任务的过程是将命令逐条执行,若将其作为主控制器去读取陀螺阵列的数据,由于存在程序执行延时,难以得到陀螺阵列同一时刻的数据。因此,采集系统选用大容量、并行运行、高速度的现场可编程逻辑门阵列(FPGA)作为主控芯片。

本文设计了一种基于FPGA的MEMS陀螺阵列信号采集系统。搭建的系统由硬件设计与数据采集系统软件实现这两部分组成。以型号为EP4CE15F17C8N的FPGA为控制器,通过对SPI通讯协议模块、存储模块、串口通信模块等各个模块的开发,实现对ADXRS810陀螺阵列的数据采集,并通过实验平台进行验证,确保系统的实时可靠性。

1 FPGA信号采集系统硬件设计

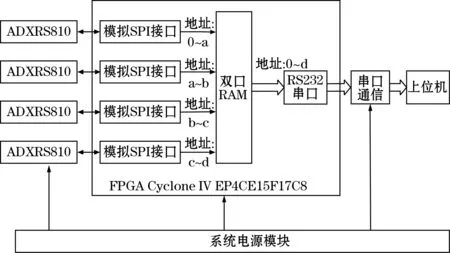

MEMS陀螺阵列采集系统是通过控制器同时对多个陀螺仪进行数据采集[4]。选用Cyclone IV系列的FPGA最小系统为控制器,设计ADXRS810陀螺阵列的外围电路,通过SPI协议与从机上的MEMS陀螺进行通信,采用双口RAM模块给阵列陀螺分配不同的地址并通过MAX232串口实现和上位机的通讯。图1为阵列陀螺采集系统硬件连接框图。

图1 阵列陀螺采集系统硬件连接框图

1.1 MEMS陀螺仪模块

从机的MEMS陀螺仪选用ADXRS系列的810芯片。它是一款测量单轴(Z轴)角速度的传感器且工作频率最高可达8.8 MHz,通过SPI通信协议与主机实现命令接收与数据传输。ADXRS810工作电压范围为3.3~5 V,当设计电路选取的供电电压为3.3 V时,选用AMS1117-3.3稳压器芯片,将5 V电源转化为3.3 V。其中电容是用来滤除直流电源中不需要的交流成分,使直流电压变的平滑。陀螺仪外围电路如图2所示,MOSI、SCLK、CS和MISO为SPI通信引脚,为了确保内部升压调节器正常工作,VX引脚应使用560 μH的电感值,同时要保证电感能够承受50 mA的峰值电流。

图2 ADXRS810电路图

1.2 FPGA控制模块

信号采集系统的处理器选用Cyclone iv系列芯片,该系列芯片相较于MAX系列功耗更低、集成度更高,数据处理的速度也显著提高。芯片集成了收发器、DSP和PCle等硬件IP模块,调用方便。芯片内部的存储容量大,逻辑单元丰富,可以满足多种通信协议要求。FPGA内部有4个PLL(锁相环)可通过其进行倍频或分频,能够满足绝大部分外设备的时钟要求[5-6]。

本文选用型号为EP4CE15F17C8N的FPGA开发板为下位机的控制器件,其硬件框图如图3所示。开发板外接存储芯片包括:SDRAM、并行FLASH、串行FLASH、SRAM和EEPROM,可缓存和处理大容量数据。串口芯片为MAX232,可通过它实现和上位机的通讯。开发板有5路独立按键,本文用其中一路给陀螺阵列做触发信号。

图3 FPGA硬件框图

双口RAM是在一个SRAM存储器上的读写的地址线、数据线和控制线是独立的,读和写互不干扰,允许对存储单元同时异步地访问,即共享式多端口存储器。因为数据可以共享,因而在访问过程中需要仲裁控制[7]。内部的仲裁逻辑控制可以为调用IP核的用户提供如下功能:对同一个地址单元进行访问时的时序先后控制;对存储单元数据块的访问进行权限的分配等。双口RAM同样可以作为实时的数据采集发送的缓冲器。

2 数据采集系统软件设计

2.1 SPI通信协议

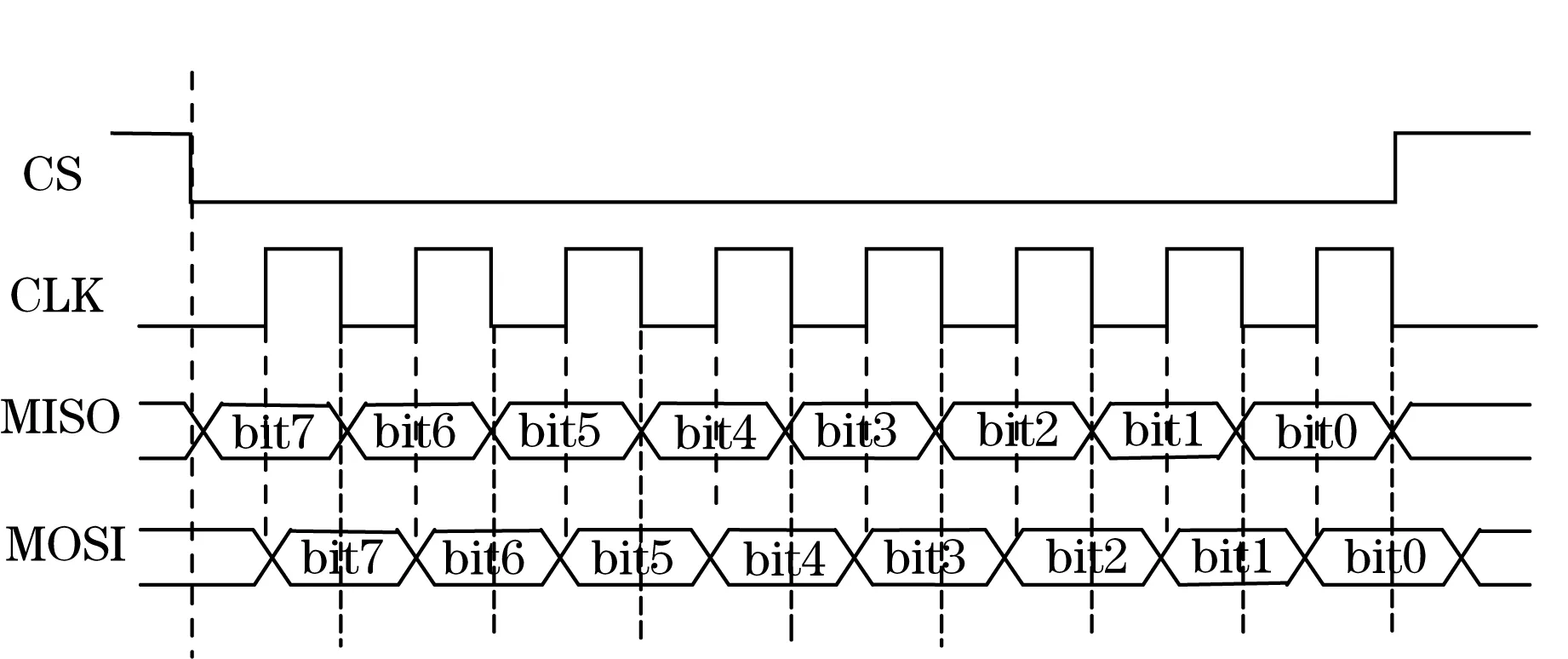

控制器FPGA与陀螺仪之间的通信协议是串行外设接口(serion perpheral interface,SPI),由于SPI协议是全双工的,因而可以快速实现主机与外围设备之间的同步信息交互。它主要是主从方式通信,通常是一主对一从和一主对多从的通讯[8]。标准的SPI是四根线,通常只占用芯片的4个接线口,如图4所示。当只有3根线的时候MOSI和MISO共用一根线,只能用于单向传输。

图4 SPI总线时序

以本文的主从通信为例,图4各个引脚的意义是:

(1)MOSI:FPGA(master,主机)输出命令,陀螺仪(slave,从机)接收命令。

(2)MISO:陀螺仪(slave,从机)输出数据,FPGA(master,主机)接收数据。

(3)SCLK:时钟信号,由主机产生。

(4)NSS:片选使能信号,由主机控制。

当NNS为低电平时,主机使能从机,可以进行主从之间的通讯,此时注意主机和从机数据交互的形式。同步通信中,数据的发送和采样是在一个时钟周期的上升沿或者下降沿进行的。同时,数据从产生到它能够稳定发送需要一定时间,所以,数据的接收最快只能在一个时钟周期,如在上升沿发送数据,那么接收数据最快只能是下降沿。反之如在下降沿发送数据,那么接收最快只能是上升沿。

因而SPI的通讯模式被分为4种,从模式0(CPHA=0;CPOL=0)到模式3(CPHA=1;CPOL=1),具体模式由CPHA(时钟的相位)和CPOL(时钟的极性)共同决定。通信过程分为空闲时刻和通信时刻,若SCLK在数据发送前后的空闲状态是高电平,那么CPOL=1,若是低电平,那么CPOL=0。

CPHA=1,表示数据是在一个时钟的第一个沿输出,若CPOL=0,数据在上升沿输出;若CPOL=1,数据在下降沿输出。

CPHA=0,表示数据是在一个时钟的第一个沿采样,若CPOL=0,数据在上升沿采样;若CPOL=1,数据在下降沿采样。

本文所采用的模式0,即CPHA=0;CPOL=0,如图5所示,以8位数据传输为例,空闲状态为低电平,且是在第一个时钟的上升沿采集数据。

图5 CPHA=0,CPOL=0;SPI时序

2.1.1 SPI通信状态机的设计

主要设计了SPI通信协议状态机,将32位的数据收发过程转化为4次8位传输。以发送过程为例,分为idle、WAIT、r_mem、w_reg和stop 5个状态。首先通过按键启动信号State~22,进入idle状态,若接收到下降沿使能信号,则进入WAIT状态,并且将第一次的8位数据缓存,判断依据为wait_cnt[3]==1′b1;发送结束后进入r_mem缓存状态,再进入w_reg将8位数据依次发后再重新进入WAIT状态,重复4次至32位数据发送完成,最后进入stop状态,此时片选为高。一次发送结束,重新返回idle,等待接收片选使能信号,开始下一轮的数据发送。SPI通信状态机转移图如图6所示。

图6 SPI通信状态机转移图

2.1.2 SPI时序仿真

通过用时序模拟软件Modelsim进行仿真验证,可以直观的观察到各个节点的时序图,能够观察到时钟的上升沿或者下降沿时,它们是否符合应有的触发关系,每一位的数据传输是否对应。

2.1.2.1 建立testbench测试文本

利用for+forever循环实现50 MHz时钟信号的模拟仿真程序。一开始clk=0,10 ns后,clk会翻转形成上升沿,再隔10 ns,clk又会翻转形成下降沿,这样就形成了周期为20 ns,频率为50 MHz的时序。原程序中的触发条件是按下开始键给的触发信号,可以写为延时100 μs后形成一个上升沿触发信号。同时源程序中的延时100 ms,50 ms, 1 ms都需要相应的缩短为100 μs左右,这样可以在接下来的view窗口中方便观察,不会出现大面积的无数据现象。

2.1.2.2 输入赋值

由于仿真时并不会由从机对其发送数据,因而为了有效观察,需要给MISO赋初值。本着简单的原则,同样写了for+forever的循环,使得MISO有规律的0,1变化,形成观察中变化的输入数据。

最后将vt文本和v文本放入仿真环境进行测试。在view窗口进行观察显示的CLK时序,以及各个需要观测的节点对应的数据。主要观察SPI时序,观察4个节点MOSI、MISO、SCLK、CS与给定的理想时钟CLK之间的关系是否符合模式要求。

由图7的SPI协议的局部观察可知,CLK时钟上升沿计数25次后,SPI协议时钟翻转,时长为500 ns,一个周期为1 000 ns,刚好是20 ns周期的500倍,SCLK时钟正确。同时从图中的箭头和所指直线可以观察到MOSI是在SCLK为下降沿时产生变化,图中三角形所显示,当SCLK为上升沿时,MOSI不变的情况下,接收缓存in_data仍然为1,图中椭圆形所显示,只有在上升沿时才会采集MISO变化的数据。CS为低电平,片选情况也正确,因而说明SPI的时序是符合

图7 SPI时序仿真

模式0的。

图8是去掉CLK信号观察整体时序,由图8可知Start_sig置1后,整个采集过程开始,当CS低电平使能,图中箭头是初始化信号中MOSI高电位发送部分,发送完CS变为高电平,同时三角形所指是数据发送接收通讯部分结束,发送Spi_Done_sig高电平信号,则Spi_Start_sig信号置低,椭圆是向FIFO发送数据命令,而后片选使能,开始新一轮的数据通信。

图8 整体时序仿真

2.2 阵列陀螺数据读取

基于Quartus ii软件编程环境,阵列陀螺数据采集过程选用Verilog HDL作为输入语言,通过控制每个时钟来驱动信号与寄存器传输。数据采集系统的流程图如图9所示。

图9 数据采集系统图

数据采集系统具体分为以下步骤:

开关键:FPGA实验板(主机)和陀螺阵列(从机)上电后,通过主机上的按键给从机一个初始Start信号,并且也可以通过它关闭二者的通信。

初始化:根据数据手册的描写,延时100 ms,向从机发送第一个32位命令2000_0003,将命令数据由Start_module发送给SPI_Module。之后再延时50 ms,发送命令2000_0000,重复3次。

ID地址读取:向陀螺仪的ID寄存器读取地址来确定SPI的通信时序是否正确,ID寄存器是2个8位地址组成的16位的寄存器,但只需向首地址发送命令即可。发送读取ID地址命令8018_0000,返回的32位数据中data20-data5的16位数据为ID数据。若接收到的数据为0x5201或者是0x5202,则认为整个初始化正确。

SPI通信:使用计数模块为通信协议的SCLK提供1 MHz时钟。由于晶振频率为50 MHz,是SCLK时钟频率的50倍。那么当晶振提供的时钟完成25个周期时,SPI协议的时钟才会产生变化,每计数25个周期产生时钟沿的变化,则可形成1 MHz时钟频率。Start_module发送命令的同时,向SPI_Module发送片选信号和开始信号。片选信号由高变低后,检测到SCLK为上升沿,则将32位数由高到低依次发送至MOSI口;若检测到SCLK为下降沿,则将MISO口接收数据放置buf中。

双口RAM:双口RAM选取深度为64,宽度为32的存储空间,并且对各个陀螺仪存储地址进行分配,Addr0-15、ADDR16-31、Addr32-47、Addr32-47分别分配给陀螺1、2、3和4。

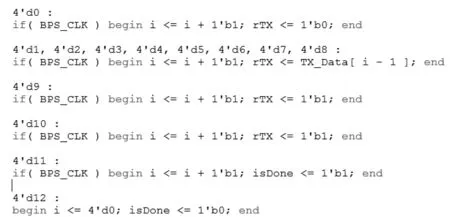

串口模块:检测双口RAM的发送信号,Tx_interface模块读出数据,将数据存入TX_Control模块。由于串口是8位数据进行发送与接收,所以TX_Control模块将32位数据由高位至低位分为4次发送至串口。设置串口波特率为9 600 bps,采用计数模块,一个周期是5 208次,当满足2 604次,频率时钟翻转,当检测到波特率时钟为上升沿时,向TX_Pin_Out口由高至低发送数据。将RAM_module模块发来的四组数据传输完成后,才会接收下一次的数据,避免数据发送混乱。串口发送部分程序如图10所示。

图10 串口发送部分程序图

图11是整个阵列陀螺采集系统的RTL视图。

图11 阵列陀螺RTL视图

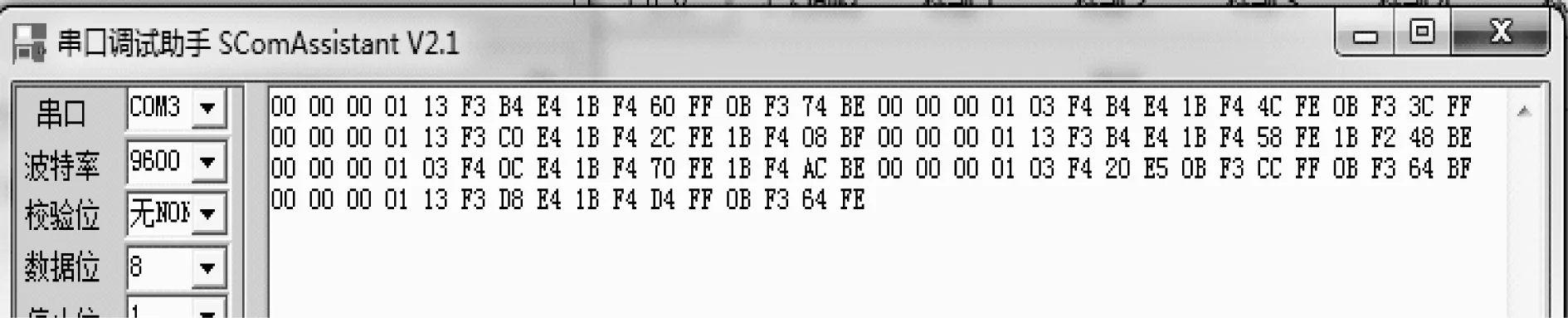

3 实验测试

实验系统测试:首先将MEMS陀螺阵列的电路板和FPGA实验板相连放置在桌面上,接通电源,连接上位机;然后通过FPGA实验板的按键给从机一个初始化的信号开始读取数据;最后在上位机串口显示MEMS陀螺阵列的Z轴输出的数据。图12是测试电路实物工作图。

(a)串口数据

4 结束语

本文设计了MEMS陀螺阵列的信号采集系统。采用Cyclone IV系列的EP4CEF15F17C8最小系统作为信号采集的控制器,搭建了由4个ADXRS系列的MEMS陀螺仪组成的外围电路,通过时序仿真验证了程序的可行性,并通过实验测试实现主机(FPGA)对从机(MEMS陀螺阵列)数据的实时读取,具有一定的工程应用价值。