基于FPGA的CameraLink图像数据接口设计

2020-10-19单彦虎张晋顼任勇峰武慧军

单彦虎,张晋顼,任勇峰,武慧军

(中北大学电子测试技术国家重点实验室,山西太原 030051)

0 引言

图像数据的采集与处理在航天测试领域中发挥着重要作用。CameraLink接口作为高速相机最主要的标准接口之一,它的出现使得高速图像源数据和图像采集装置之间的速度得到匹配。目前多采用串并转换芯片组成的多种驱动器和接收器来实现CameraLink接口,通过CameraLink接口接收两路图像数据至少需要两块接口芯片,需要占据PCB较大的面积,由于FPGA需要接收28位并行数据所以占用了大量布线面积以及IO口资源,同时传输数据的速率也受转换芯片的限制。但是使用这种方法可以减小主控芯片对CameraLink接口数据的编解码压力,一定程度上降低了接口开发的难度。因此,这也是目前应用最广泛的CameraLink接口实现方法[1-3]。为了适应图像采集装置小型化低成本的开发要求,本设计提出采用CameraLink接口实现方案,在FPGA内部的Select IO IP核源码的基础上,对IP核源码进行适当更改,实现了一种基于FPGA内部原语的CameraLink接口的实现方法[4],速率可达192 MB/s,其中有效数据速率达110 MB/s。

1 设计方案

1.1 总体方案

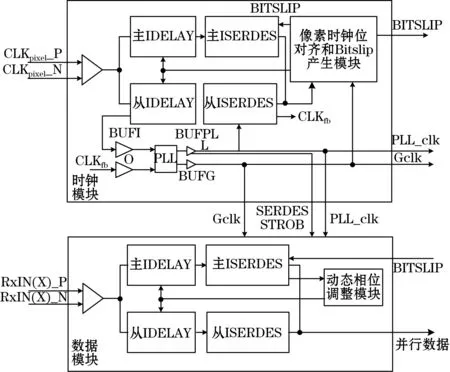

本设计基于主控芯片FPGA,在不通过CameraLink串转并芯片的情况下直接接收带有编帧格式LVDS数据,完成更高速率、无误码的传输。数据流从FPGA的IO口到FIFO缓存的实现过程如图1所示。

图1 图像数据流框图

1.2 CameraLink接口接收端的FPGA实现

CameraLink接口的数据传输基础就是低压差分信号(LVDS)形式传输。完整的CameraLink接口至少应该包含1对TX端和RX端(发送端和接收端)。发送端采用3.5 mA的恒流源发送数据,在接收端口处差分端串接1个100 Ω电阻,将电流形式的数据传输转换为低压差分电压。发送端通过改变电流流向控制接收端电压极性,从而控制接收端的逻辑“0”和“1”。RX端接收5路LVDS信号,其中4路为串行数据流和1路为专用串行时钟流。接收端的主要功能是将串行数据单端信号按照解串比为1∶7进行解串,将这5条LVDS信号还原为28路并行的单端数据信号以及1路伴随时钟的单端信号[5]。

FPGA内含丰富的原语和专业IP核可以将FPGA的IO例化为多种形式的电平接口。例如本设计选用的主控芯片Spartan-6 FPGA,通过配置它内部SelectIO IP核可以将FPGA的IO引脚匹配为差分引脚,并且通过设置IP核的一些基本参数就可以将5对差分对配置为符合CameraLink接口标准的电气接口。此设计通过调用FPGA内核,配置IO引脚为差分模式,实现CameraLink接口,用来接收发送端的5路LVDS信号。内部原理框图如图2所示。

图2 FPGA内部串转并原理框图

2 数据接收端控制逻辑

2.1 约定数据格式

本文采用图像标准卡作为图像数据源。标准卡基于PCI设计,此卡作用除了产生特定格式数据源外还包括后期数据的回读与回读数据的校验[6-7]。约定图像数据传输格式为1 024×1 024如表1所示。数据源通过Camera Link接口并转串芯片按数据格式发送数据。

表1 数据格式

2.2 数据接收逻辑

CameraLink标准规定将28位的数据信号中的4位用作同步信号,保证高速传输模式下数据能正确接收,这4位信号中有1位保留信号,其余3位信号定义为帧同步信号(FVAL)、行同步信号(LVAL)、数据有效信号(DVAL)。当发送新一帧数据时首先将FVAL拉高表示一帧数据即将发送,然后将LVAL拉高则表示相机要发送一行有效数据,当FVAL和LVAl同时为高后DVAL只要为高即表示有相机发送有效数据[8]。

由于有效像素数据为16 bit,设计的Camera Link接收模块解串出来的数据位28 bit,因此需要剔除28 bit数据中的无效数据位。Camera Link标准中规定3个PORT的像素数据信号与4 bit使能信号与28 bit TX端接口位映射关系如表2所示。28-bit数据位置映射如图3所示,其中“RxIOclk”为对像素时钟“RxCLK IN”的解码时钟,芯片内部根据该时钟对串行数据进行采样。同时根据Camera Link接口标准16 bit像素数据占用PORTA和PORTB两个PORT,结合表2,接收的27位数据中的低16位即为16 bit的有效像素数据,同时高3位为视频图像数据的同步信息位。

图3 28-bit数据位置映射图

表2 28-bit TX端口与PORT的映射

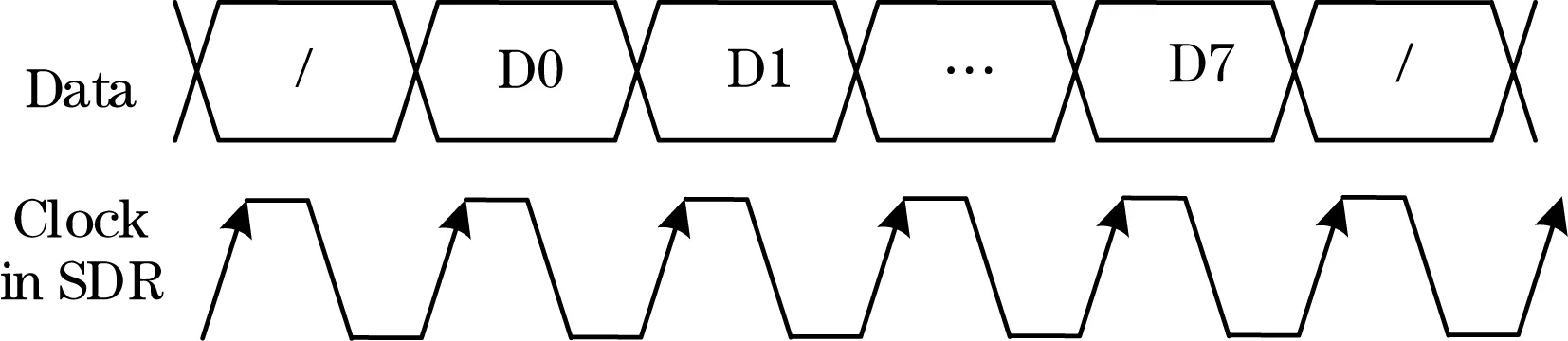

数据传输速率较快,在对图像数据接收时,主要依靠FVAL、LVAL、DVAL 3个信号对数据图像数据进行接收。数据接收逻辑时钟采用55 MHz,该时钟使用经BUFG输出的Gclk,数据在Gclk的上升沿由Camera Link接收模块输出,为了保证数据的准确性,数据接收模块在时钟Gclk的下降沿对数据进行接收。采用BUFPLL的LOCKOUT引脚作为数据接收模块的复位信号,当LOCKOUT输出为高时表示时钟已经同步。采用单位传输速率(signal data rate,SDR)模式,在55 MHz时钟下有效像素传输速率可达110 MHz/s,图4为SDR模式下数据与时钟的对应关系。图5为数据接收模块接收一行数据的逻辑实现流程图。在进行数据接收时需要依靠行同步和帧同步信号,由图6可知当帧同步信号由低变高时表示数据新一幅图像开始传输,没有数据同步信号,当行同步信号由低变高的上升沿即开始新一行数据传输。接收到数据后需要对数据进行编帧便于数据存储和分析,根据设计需求如表3所示帧结构,其中帧头用于开始新一幅图像,帧计数用于计算图像幅数,数据校验和用来后期数据处理时校验每一幅图像中是否有误码丢数情况。

图4 SDR模式时序图

图5 数据接收流程

图6 Camera Link接口时序需求

表3 数据编帧结构

3 接口逻辑功能仿真

本设计Camera Link数据接收采用SDR接收模式。当数据流的变化频率和对应时钟的变化频率相同时称为单倍传输速率(signal data rate,SDR)模式,每个数据位均在时钟的上升沿(或者下降沿)时变化[9]。SDR模式下通过时钟的上升沿和下降沿可以比较精确的控制采样点落到数据保持时间的中部,逻辑实现相对复杂,对数据的建立时间要求较低。采用FPGA中的PLL和BUFPLL实现对像素时钟的倍频和同步。图2 Camera Link接收端FPGA实现原理框图中像素时钟CLKpixel首先经过延时模块平衡掉7位数据深度的延时后输入PLL。PLL的只输出2个时钟信号,一个是对CLKpixel进行7倍频得到PLL_clk用于数据和时钟解串,另一个经BUFG后作为全局时钟Gclk。当PLL用于数据接收时必须使能反馈时钟CLKfb引脚,CLKfb是ISSERDES的时钟反馈引脚的输出时钟输出后经BUFIOFB原语转换后输入,这种机制可以保证进行倍频后的时钟PLL_clk和原始输入的时钟CLKpixel保持相位相同。为了便于分析,采用28Bit独热码作为数据源激励对Camera link接口进行仿真。图7为仿真波形截图(没有执行PORT映射等操作)。根据仿真波形截图,容易分析出接口逻辑满足设计需求。

图7 FPGA实现CameraLink接口接收端仿真波形图

4 试验验证

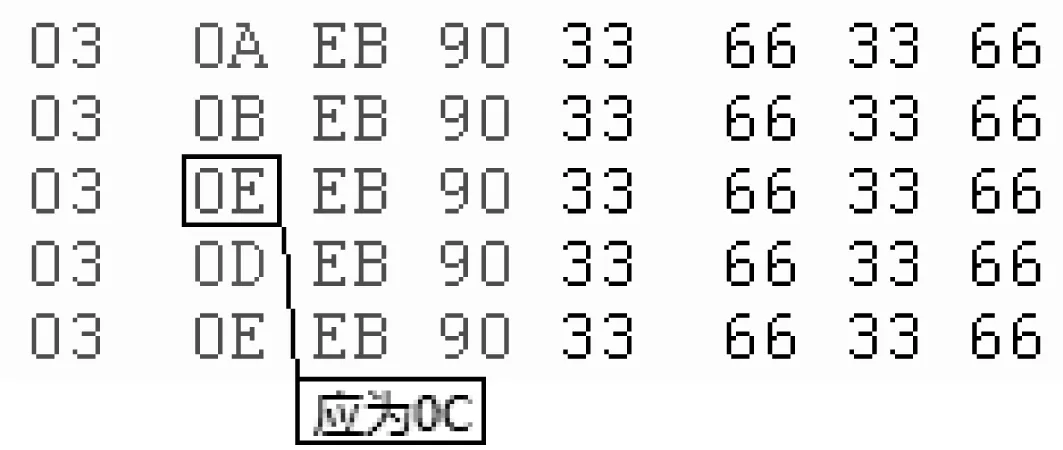

测试时将标准卡安装在CPCI机箱上,模拟图像数据通过2 m电缆发送至接收单元。作为图像数据源,标准卡按照表1通过DS90285芯片发送数据。接收数据后,读取并校验数据的准确性,发现数据出现误码。查看回读后的原始数据发现:数据行计数低二位数据容易出现错误(如图8行计数0C错接为0E)。考虑到数据衰减,改用0.4 m电缆传输,数据没有出现误码。分析长线衰减程度:通过示波器抓取并比对发送端及接收端数据波形,接收端数据虽然衰减但仍然在LVDS信号协议可接受范围(250~450 mV)(量取的接收端差分电压如表4所示),从而确定长线衰减不为主要原因。

图8 数据错误示意图

表4 接收端差分电压

在抓取接收端数据波形时发现有频率约为400 kHz的干扰信号一直存在。考虑到是由于开关电源引起的干扰,量取DC/DC电源壳地间发现如图9所示干扰,从波形图中可以看出干扰峰峰值接近1.8 V,频率大约为420 kHz,从而定位干扰源为DC/DC电源。在DC/DC接壳引脚与信号地间串接103电容,削弱干扰。量取干扰源波形如图10,幅值被削弱。使用2 m电缆测试,数据无误。验证了此次接口设计的可行性。

图9 DC/DC电源壳地间干扰

图10 削弱后的DC/DC电源壳地间干扰

5 结论

本次设计使用FPGA内部原语ISERDES和OSERDES实现了Camera Link接口数据的串并之间的相互转换,利用VHDL语言设计了数据接收逻辑和编帧逻辑。本设计基于FPGA的CameraLink接口在55 MHz时钟下实现110 MHz/s的数据接收。在FPGA的IO口短缺或是内部资源足够的情况下,完全可以使用原语编程代替串并转换芯片实现CameraLink接口数据的串并转换。