用于微结构气体探测器的类金刚石碳阻性电极制备研究

2020-06-16尚伦霖张广安李文生

尚伦霖,周 意,吕 游,张广安,李文生

(1.兰州理工大学 材料科学与工程学院,甘肃 兰州 730050;2.中国科学院 兰州化学物理研究所 固体润滑国家重点实验室,甘肃 兰州 730000;3.核探测与核电子学国家重点实验室,中国科学技术大学,安徽 合肥 230026)

20世纪80年代末,微条气体室(MSGC)探测器的诞生拉开了微结构气体探测器(MPGD)研发的序幕[1],随后气体电子倍增器(GEM)[2]和微网格气体(Micromegas)探测器[3]等得到快速发展。由于MPGD具有位置分辨好、计数率能力高、工作稳定、抗辐射能力强、容易加工成各种形状、造价低廉及能大面积生产等特点,已得到广泛应用[4]。但随着应用环境越来越苛刻,MPGD在工作过程中的打火现象也越来越严重。打火产生的放电不仅会加速探测器老化,且会损坏探测器的前端电子学,造成束流时间的浪费及探测器维护费用的提升。目前使用阻性电极是抑制打火现象的有效方法之一,常用的阻性电极是通过丝网印刷碳浆料制备,其具有成本低、制备过程快速简单及能在大面积探测器制作中应用等优点,却存在容易被打火放电损坏、面电阻精确度控制难、无法用于精细结构探测器的制作等缺点,因此开发适用于MPGD的新型阻性电极材料非常重要。

类金刚石碳(DLC)薄膜是一种由金刚石结构的sp3杂化键和石墨结构的sp2杂化键碳原子相互混杂构成的碳材料,具有优异的机械、光学、电学等性能,已在诸多领域得到广泛应用[5]。近年来,DLC阻性电极的研发和应用已引起了国内外微结构气体探测领域的密切关注。2013年,日本神户大学的Ochi[6-7]首次采用磁控溅射方法在Apical(聚酰亚胺材料)绝缘膜表面沉积DLC薄膜,制作成阻性电极并应用于10 cm×10 cm的Micromegas探测器。意大利国家核物理研究院(INFN)的Bencivenni等[8]使用DLC阻性电极研制出计数率能力高达3.5 MHz/cm2的双阻层μRWELL(Micro-Resistive WELL)探测器。Colaleo等[9]探索使用离子束溅射(IBS)和脉冲激光沉积(PLD)技术制备FTM探测器(Fast timing MPGDs)的DLC阻性电极。在国内,对DLC阻性电极及其在MPGD中应用方面的研究工作较少。

本文通过磁控溅射法制备DLC阻性电极,并对DLC阻性电极进行面电阻调控和性能优化。

1 DLC阻性电极的制备和表征方法

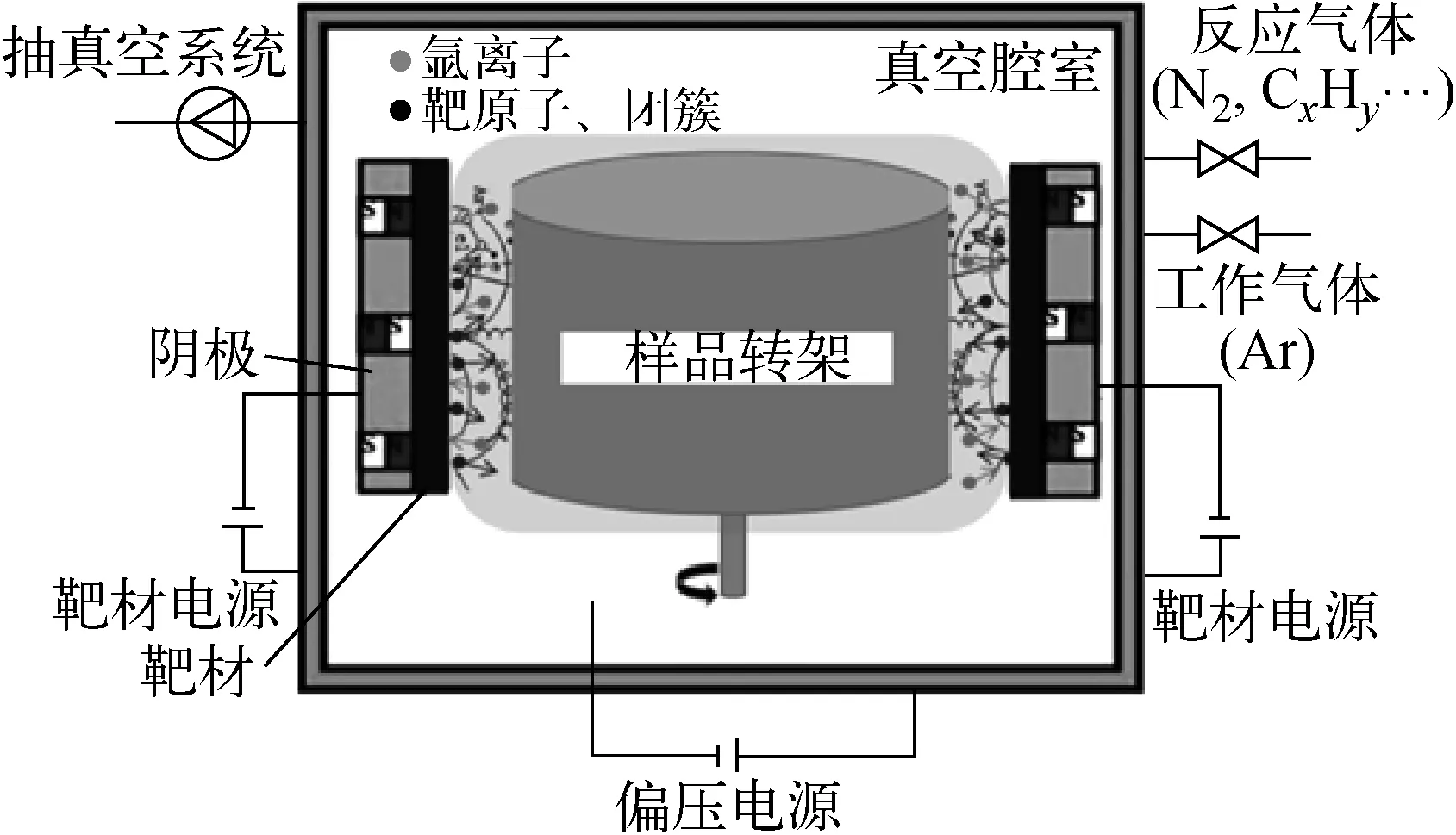

DLC阻性电极制备的设备如图1所示,其原理是真空腔室中辉光放电作用产生的大量电子在磁场束缚下不断解离氩气,得到的氩离子在电场力作用下轰击高纯石墨靶材,而二次电子继续解离氩气,这样会使高能氩离子不断轰击,溅射得到的碳原子、原子团簇沉积在基材表面并形核生长成DLC薄膜,同时也可在溅射过程中通入氢气、氮气和烃类等气体发生化学反应,制备元素掺杂的DLC薄膜。

图1 DLC阻性电极制备的设备示意图Fig.1 Schematic of device for DLC resistive electrode deposited

将用于制作MPGD电极的Apical膜通过酒精擦拭清洁后在70 ℃下烘烤10 h以上,再固定在样品转架上,抽真空至3.0×10-5Torr下通入高纯氩气,在Apical膜上施加高偏压进行轰击刻蚀后,溅射高纯石墨靶材进行制备DLC阻性电极。完成制备后,主要从面电阻、膜基结合强度和内应力等方面进行表征。面电阻测试方法如图2所示,将DLC薄膜平铺在水平面上,用两个平整的铜条压在DLC薄膜两端,再用万用表测量铜块所构成正方形区域的电阻。DLC阻性电极的膜基结合强度通过用蘸酒精的无尘布用力擦拭观察DLC膜是否脱落来考核。内应力大小通过将制备的DLC阻性电极平铺在水平面上观察卷曲程度来定性判断。

1——Apical基材;2——DLC薄膜;3——铜条;4——万用表图2 DLC阻性电极面电阻测试方法Fig.2 Method for testing surface resistivity of DLC resistive electrode

2 DLC阻性电极面电阻调控

DLC阻性电极的面电阻与MPGD的性能息息相关,适当的面电阻不仅能在探测器发生打火放电时产生较大压降而降低内部电场,达到抑制放电的效果,且可使感应信号保持高度透明的同时保证探测器具有高的计数率能力。研究发现,DLC阻性电极的面电阻与制备过程中石墨靶电流、真空度、元素掺杂等因素有关。

2.1 石墨靶电流

保持其他工艺参数一致,分别在不同靶电流下溅射高纯石墨靶材制备DLC阻性电极,研究靶电流对DLC面电阻的影响。如图3所示,随靶电流的增大,DLC面电阻呈降低趋势,较大靶电流条件下溅射出的碳原子、碳原子团簇较多,沉积速率较快,制备的DLC阻性层厚度较大,使得阻性层中载流子的迁移率提高,导致面电阻变小。

图3 DLC阻性电极面电阻随靶电流的变化Fig.3 Surface resistivity change of DLC resistive electrode with target current

2.2 真空度

图4 DLC阻性电极面电阻随真空度的变化Fig.4 Surface resistivity change of DLC resistive electrode with vacuum degree

本底真空度是影响磁控溅射制备薄膜材料相关性能的重要因素之一[10]。在靶电流为1.0 A、转速为10 r/min、沉积时间为40 min的条件下改变真空度制备不同DLC阻性电极。如图4所示,DLC阻性电极的面电阻随真空度的升高而降低,在较低真空度(大于1.0×10-5Torr)时面电阻变化幅度较大,在较高真空度(小于0.4×10-5Torr)时面电阻变化幅度较小。其原因一方面是真空度较高时腔体内氧气、水蒸气等杂质分子较少,使沉积的DLC薄膜中掺入的杂质元素较少,微观结构中的sp2杂化键含量较高,导致较低的电阻;另一方面是低真空度条件下残余的杂质分子由于碰撞作用会降低溅射粒子在沉积过程中的能量,使薄膜无序化程度更高,电子迁移能力降低,导致电阻较高[11]。

2.3 元素掺杂

通过研究真空度对DLC阻性电极面电阻的影响,发现杂质元素对DLC的电学性能有着明显影响。在制备过程中分别通入不同流量的异丁烷和高纯氮气,研究氢元素和氮元素掺杂对DLC阻性电极面电阻的影响。如图5所示,在本底真空度为1.0×10-5Torr、靶电流为3.5 A、偏压为30 V、转速为5 r/min、沉积时间为240 min条件下,DLC阻性电极面电阻随异丁烷流量的增加显著升高,仅通入4.0 sccm时便超过了所使用万用表的量程范围(500 MΩ),这表明氢元素掺入对DLC阻性电极影响很大,会使DLC的微观结构和成分发生变化。据此,分别对不含氢DLC薄膜和含氢DLC(HDLC)薄膜进行X光电子能谱(XPS)分析,如图6所示。由图6可见,两种薄膜的C1s谱通过高斯分峰拟合可得到sp2杂化键、sp3杂化键和C—O键的3种峰,其相应计算结果列于表1。HDLC薄膜中的sp3杂化键含量较高,sp3与sp2的含量比大于DLC薄膜,这与刘磊等[12]的研究结果相同。其原因是由于薄膜制备过程中形成无序网络结构时,因碳碳键能大于碳氢键能,使得氢原子更易与碳原子外端的悬键结合,阻止sp2杂化键的形成,促进sp3杂化键数量的增加,这导致决定DLC导电行为的石墨结构sp2杂化键含量减少。此外,大量悬键被饱和也会使薄膜微观结构向类多聚物转变,导致薄膜电阻增加[13-14]。

图5 DLC阻性电极面电阻随异丁烷通入流量的变化Fig.5 Surface resistivity change of DLC resistive electrode with flow rate of isobutane

此外,在靶电流为1.0 A、偏压为30 V、转速为10 r/min、沉积时间为25 min的条件下制备不同掺氮DLC阻性电极,如图7所示,其面电阻随通入氮气流量的增加而显著升高,表明一定含量的氮元素掺杂可提高DLC阻性电极的面电阻。这与Lee等[15]的结果不一致,可能的原因是DLC阻性电极的电阻影响因素较复杂,在受氮元素掺杂影响的同时还会受沉积时间、厚度、偏压、靶电流等其他因素的综合影响。

图6 DLC和HDLC薄膜的XPS C1s谱Fig.6 XPS C1s spectrum of DLC and HDLC films

表1 DLC和HDLC薄膜XPS C1s谱的高斯分峰拟合结果Table 1 Gaussian-Lorentzian fitting result of XPS C1s spectrum of DLC and HDLC films

图7 DLC阻性电极面电阻随高纯氮气通入流量的变化Fig.7 Surface resistivity change of DLC resistive electrode with flow rate of high purity nitrogen

3 DLC阻性电极结合强度的优化

DLC阻性电极的结合强度是指DLC阻性层与基材Apical膜之间的结合力。研究中主要通过对Apical膜的前处理来优化结合强度。一方面通过对Apical膜表面进行喷砂预处理,适当提高表面粗糙度;另一方面在DLC阻性层溅射沉积之前对Apical膜加热并施加高偏压,使产生的高能离子对基材表面轰击刻蚀,形成有利于DLC形核生长的微观结构。通过这些基材前处理的方式能有效提高DLC阻性电极的结合强度,在用蘸酒精的无尘布擦拭中DLC阻性层未出现脱落现象,满足MPGD加工过程中刻蚀工艺的要求。

4 DLC阻性电极内应力的优化

在DLC阻性电极制备过程中,溅射沉积的DLC阻性层内应力过大可导致软基材Apical膜发生严重卷曲而不能用于探测器的制作和加工,因此对内应力的优化至关重要。已有研究[16-18]表明,DLC内应力可通过元素掺杂、高能粒子轰击、退火处理等方法来降低,然而这几种降低内应力的方法均会引起DLC面电阻的变化。因此,本研究通过强化基材、降低DLC阻性层厚度和优化设计装夹方式来调控DLC阻性电极的内应力。研究发现,选用背面敷铜层的Apical膜,不仅在DLC制备过程中起到支撑作用而减少DLC本身内应力的影响,还能结合探测器的加工工艺制作出新构型的MPGD。将DLC阻性层厚度控制在100 nm以内,优化装夹方式在Apical膜正反两面都制备DLC阻性层,均能有效降低DLC阻性电极的内应力,从而避免发生卷曲现象。图8示出DLC阻性电极样品内应力优化前后的对比,优化后(左侧)样品的内应力明显降低,满足探测器的制作要求。

图8 DLC阻性电极样品内应力优化前后的对比Fig.8 Comparison of DLC resistive electrode of internal stress after and before optimization

5 DLC阻性电极的应用

图9 μRWELL PCB结构示意图Fig.9 Schematic of μRWELL PCB structure

基于对DLC阻性电极面电阻、结合强度、内应力等影响因素的探索,进一步优化工艺参数制备出结合强度好、厚度约100 nm、面电阻约45 MΩ/□的DLC阻性电极,并在μRWELL探测器中成功应用。图9示出μRWELL PCB结构示意图。对探测器进行测试,使用8 keV铜靶X射线作为入射粒子源,在Ar∶CO2=70∶30混合气体中探测器的电子倍增系数达到104以上,计数率能力大于100 kHz/cm2;对于150 GeV的缪子,探测器的探测效率大于90%,探测器二维位置分辨能力优于70 μm[19]。

此外,研究中还将DLC阻性层沉积在其他基材上制备了适用于不同类型探测器的阻性电极,如沉积在尼龙、玻璃纤维和树脂球体表面制得阻性ACHINO,应用于暗物质探测器;沉积在丝网上得到DLC阻性丝网,用于单阻性层Micromegas探测器和光学读出的Micromegas探测器;沉积在PCB表面,用于大面积阻性厚型气体电子倍增器(THGEM)、μRWELL探测器;沉积在玻璃、氟化镁晶体表面,用于电阻板室(RPC)、多气隙电阻板室(MRPC)和光电探测器。

6 结论

本文采用磁控溅射技术制备了DLC阻性电极,研究了靶电流、真空度、元素掺杂等因素对DLC阻性电极面电阻的影响,随靶电流的增大和真空度的升高,DLC阻性电极的面电阻呈降低趋势。随氢元素和氮元素的掺杂,DLC阻性电极的面电阻呈增大趋势,且稳定性变差。

通过对膜基结合强度和内应力的优化,成功研制出厚度约为100 nm、面电阻约为45 MΩ/□的DLC阻性电极,并在μRWELL探测器中成功应用。掌握了磁控溅射法制备应用于多种MPGD的DLC阻性电极的方法,这为新构型探测器的研发和性能提升奠定了技术基础。