应用于微测辐射热计的12位SAR ADC的设计

2020-04-26黄伟奇唐祯安

黄伟奇,唐祯安

(大连理工大学电子信息与电气工程学部,辽宁省集成电路技术重点实验室,辽宁大连116024)

0 引言

红外探测器利用探测目标与成像背景之间的红外辐射差异,将红外辐射信号转变成电信号输出[1]。红外探测器分为光子红外探测器和热探测器。热探测器中的微测辐射热计因其工作波段宽、阵列密度高、成本低且性能优良等特点逐渐得到广泛关注[2]。微测辐射热计通过吸收辐射产生温升,该温升使热敏电阻阻值发生变化,从而产生变化的电压,通过读出电路读取该电压的变化值来探测红外辐射的大小。传统微测辐射热计输出模拟信号,需再经预处理电路减小干扰和噪声,由模数转换电路将模拟电压信号转换为数字信号,最后进行数字图像处理以供显示。数字化的微测辐射热计在读出电路芯片上集成模数转换器(ADC),可免去预处理电路,直接输出数字信号。微测辐射热计的数字化是目前国际上的研究重点,具有接口简单、高抗干扰、低读出噪声、高稳定性等特点[3]。

1 微测辐射热计片上ADC技术

1.1 微测辐射热计片上ADC的选型

微测辐射热计的红外焦平面与ADC的片上集成分为3种类型,分别是像元级ADC、列级ADC和芯片级ADC[4]。目前,国内常用的微测辐射热计探测阵列规模主要为 160×120,320×240,640×480、1 024×480等中小型阵列,帧频主要为 60 f/s[5]。对于 320×240以下的小规模阵列,采用芯片级ADC进行集成可减小芯片总功耗,且版图不受限也可提高ADC的转换性能。逐次逼近型模数转换器(SAR ADC)适用于芯片级ADC的应用。SAR ADC功耗低,转换速度中等,分辨率高,面积小,同时,转换异步信号时不产生通道延迟,非常适合芯片级ADC的应用。但是,芯片级ADC对ADC的转换速度有较高的要求,若转换速度过高,会引起较高的功耗和较大的时钟噪声与容性噪声。因此当SAR ADC作为芯片级ADC应用时要尤其注意速度与功耗的平衡。本文针对微测辐射热计芯片级ADC应用,设计了一款12位的低功耗SAR ADC。

1.2 SAR ADC 设计指标

本文SAR ADC的设计指标基于本课题组所研制的氧化钒微测辐射热计探测阵列及其读出电路的芯片测试结果,具体参数如表1所示。

读出电路工艺为 CSMC 0.18 μm CMOS 工艺,因此ADC基于相同的工艺进行设计。根据式(1)、式(2)、式(3)得到SAR ADC各参数的最小指标如表2所示。

式中:Vmin为最小分辨电压,V;RV为输出电压响应率,mV/K;Tmin为温度分辨率,K。

式中:SNDR为信噪比,dB;Vomin为最小输出电压值,V,这里为0.9 V;NETD为等效噪声温差,mK。

式中:SR为ADC采样速率,MSPS;160×160为阵列规模;FF 为帧频,f/s。

表2 SAR ADC设计指标

2 电路结构

SAR ADC电路设计分为电容阵列DAC设计,比较器的设计和数字逻辑控制电路的设计,本节内容对3个部分的设计分别进行阐述。

2.1 新型电容阵列DAC的设计

2.1.1 新型DAC电路结构

DAC的电路性能对整个ADC系统的功耗、面积、静态特性和动态特性产生影响。传统12位DAC阵列采用分段结构,若分为2段,设Cu表示单位电容容值,最高位电容值最小为26Cu,则电容总值过大,影响电路的功耗与面积;若分为3段,将会有2个桥接电容。桥接电容会带来较大的寄生电容,也将影响电路整体的线性度与信噪比,因此应减小桥接电容的个数。本文设计了一种新型的DAC阵列,能够减小电路功耗与面积,减小阵列噪声,提高ADC的有效位数与信噪比。

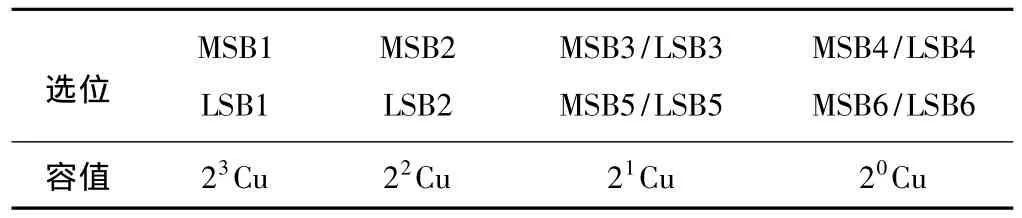

电路结构如图1所示。高6位电容MSB1~MSB6采用4-2的分段方式进行分段,设单位电容为Cu,第MSBN位码字电容值为CMSBN,满足高位开关改变时变化电压值为相邻低位开关改变时变化电压值的2倍,则CMSBN=2CMSBN+1。低6位电容LSB1~LSB6采用相同的4-2分段方式进行分段,且取值与MSB各位相同,同时并接在桥接电容两端。各码字的电容值如表3所示。

对于桥接电容 Cs,Cs=[2n/(2n-1)]Cu[6],其中 n 为分段低段的码字总数,本电路分段为4-2.则本电路中n=2。

图1 创新型DAC电容阵列

表3 各码字电容值

本阵列采用顶板采样的开关方式。电容阵列顶板与采样开关共接,底板连接各码字的转换开关。转接开关为三端口开关,其输出端接电容阵列的底板,输入端各接2个不同的参考电压。对于MSB1~MSB6高六位的转换开关,开关状态转换时满足ΔV=Vref1。对于LSB1~LSB6低六位满足ΔV=(1/26)Vref2。本创新电路所基于的原则为:通过改变转换开关每次的转换电压,从而减少电容个数的使用以及桥接电容个数的使用。

DAC工作过程:

(1)采样阶段:采样开关闭合,差分阵列的P阵列与N阵列分别接输入电压Vp与Vn,转换开关一端接电容底板,一端接高参考电压Vref1。如图2(a)所示。

(2)MSB转换阶段:采样开关打开。以MSB3开关为例,若MSB2位的比较结果为Vp>Vn,则本次转换时P阵列的MSB3开关将由高电平Vref1转接地,N阵列MSB3开关不变,按MSB1至MSB6的顺序依次转换,直至6位转换结束。如图2(b)所示。

(3)LSB转换阶段:以LSB1开关为例,若MSB6位的比较结果为Vp>Vn,则本次转换时P阵列的LSB1开关将由高电平 Vref1转接Vref2,N阵列LSB3开关不变,反之,P阵列的LSB1开关不变,N阵列的LSB1开关将由高电平Vref1转接Vref2。如图2(c)所示。

2.1.2 DAC 噪声分析

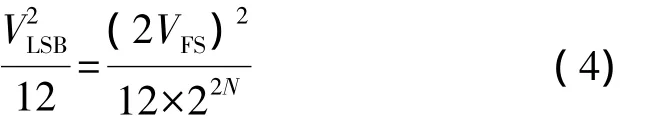

噪声是影响电路动态性能的主要因素。电容阵列噪声主要为采样和量化时的热噪声。对于一个N位的ADC,其量化噪声可表示为

式中:VLSB指ADC的最小量化电压;VFS为ADC输入信号摆幅。

热噪声的标准差可表示为

式中:k为玻尔兹曼常数;T为绝对温度;Ct为总采样电容值。

为减小电路热噪声对电路精度的影响,热噪声标准差应小于量化噪声,即

图2 转换时开关状态

根据此式可算出总电容值Ct,此电容值除以本电容阵列的单位电容个数,可以得到最小单位电容值,选择Cu=128 fF,可以满足设计要求。

2.1.3 DAC 功耗分析

本DAC的采样方式为顶板采样,此种方式比传统采样方式减少81.5%的功耗[7]。而本文的创新阵列在原顶板采样的基础上使功耗进一步减小,下文将详细分析此创新电容阵列DAC的功耗。

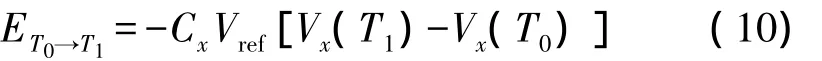

采样阶段DAC无功耗,对于转换阶段的功耗大小,设T0时刻为转换前状态,T1时刻为转换后状态。

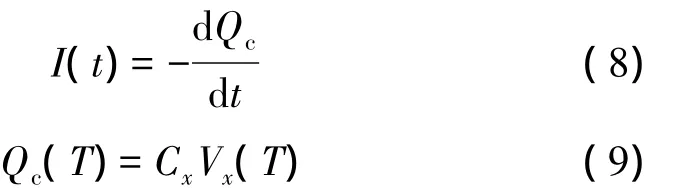

式中:ET0→T1为T0转换为T1的总功耗;I(t)为t时刻的电流大小。

式中:Vx为x端的电压;Qc为电容的电量值。

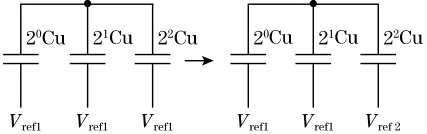

将顶板采样方式中的传统方案与创新的方案进行功耗对比。为便于比较,两者均选择两段式,传统方案选择6-6分段,创新方案选择3-3并3-3方案。如图3所示。

图3 两种方案电容阵列对比示意图

传统方案功耗分析:

最高位码字MSB1转换过程如图4所示,其功耗为

依次可求得MSB2~MSB6的功耗。在传统方案中,MSB1~MSB6与LSB1~LSB6功耗相同,传统方案总功耗为65Cu

创新方案功耗分析:

图4 传统方案MSB1转换过程

图5 创新方案MSB1转换过程

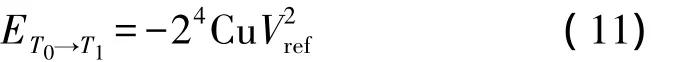

对于高六位 MSB1~MSB3,最高位 MSB1如图5所示,功耗为

MSB1~MSB3与 MSB4~MSB6功耗相同,可得MSB总功耗为10.5CuV

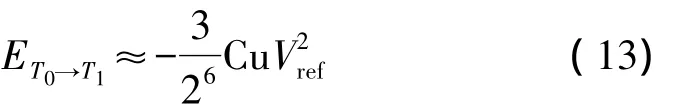

LSB1转换功耗。如图6所示。

图6 创新方案LSB1转换过程

同样可得LSB1~LSB6各自的功耗,总功耗约为0.16Cu

将MSB1~MSB6与LSB1~LSB6功耗相加,得到新阵列总功耗为10.56CuV。因此创新阵列的功耗仅为传统方案总功耗的16.24%。

将两种方案所使用的Cu个数以及功耗进行对比,如表4所示。Cu个数代表面积,可知创新方案的面积和功耗较传统方案大幅减小。

表4 传统方案与创新方案功耗对比

2.2 比较器的设计

高速低功耗SAR ADC要求比较器具高速高精度低功耗的性能,比较器的精度对整个电路的精度有较大的影响。为取得较高的精度,要求比较器的失调电压最小化和噪声最小化。本文选择使用前置放大器和动态锁存器的结构,前置放大器具有负指数响应,能将较小的输入迅速放大,动态锁存器具有正指数响应,输入较小时放大速度慢,当输入达到Vx,如图7所示,能使输出迅速达到电源电压[8],满足高速要求。

图7 预放大与锁存器输出曲线

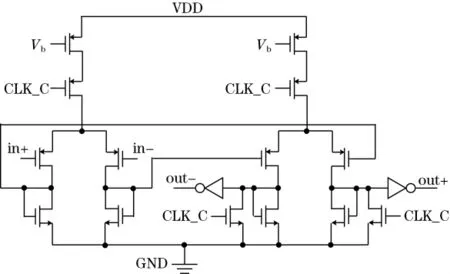

输入失调电压是影响电路增益误差的主要因素。为减小输入失调电压,可增大输入对管的宽长乘积,增大输入管过驱动电压。比较器噪声不仅影响电路线性增益,同时也影响电路的动态特性。比较器噪声的主要来源为动态比较器的回馈噪声,选择放大级与动态比较器级联的方式,可以将动态比较器回馈噪声大幅度减小。本文比较器结构如图8所示。

图8 比较器电路图

此设计具有低失调、低噪声、低功耗且高速的特点。经过仿真,本设计比较时间为1 ns,最小分辨电压小于1 μV,失调电压小于 0.1 μV,满足本 ADC 设计要求。

2.3 数字逻辑控制电路设计

本文数字逻辑电路选择异步时序,它具有多个优点:比较器内部的工作不需要外部提供高速时钟,由内部自己产生;DAC的建立由比较器控制,当比较器结束比较时才会产生激励信号促使DAC工作。

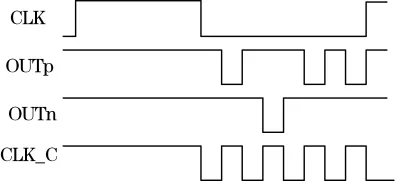

本文时序如图9所示。外部的总时钟信号为控制信号,当CLK为低电平时,电路采样,比较器的控制时钟不产生波形,当CLK为高电平时,电路进行比较,比较器的输出端p与n会产生2个相反的波形,使比较器控制时钟产生时钟信号。

图9 比较器时序图

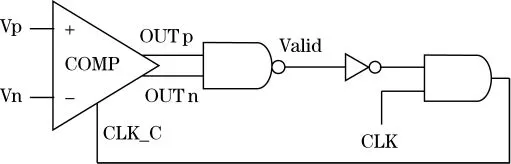

比较器时钟产生电路如图10所示。本文选择门控环形振荡电路产生时钟信号。此电路构成简单,功耗低,易实现,且占用面积小。

图10 比较器时钟产生电路

时序控制电路如图11所示。该电路由D触发器串联构成,电路时钟由时钟产生电路中的Valid信号控制,比较器开始工作后时序电路开始工作,每一个触发器控制一个码字的转换开关,同时电路由RN信号控制复位,当RN为低时,电路输出为0,整个ADC将停止工作,RN为高时,电路正常工作。

图11 时序控制电路

经过仿真,本数字电路采样速率可达5 MSPS,满足设计要求。

3 电路仿真与结果分析

本 SAR ADC 采用CSMC 0.18 μm CMOS 工艺,设计指标为:电源电压1.8 V,分辨率12 bits,采样率5 MHz,输入电压范围0~1.8 V。对整体电路进行仿真,仿真分为静态仿真与动态性能仿真。

3.1 静态仿真

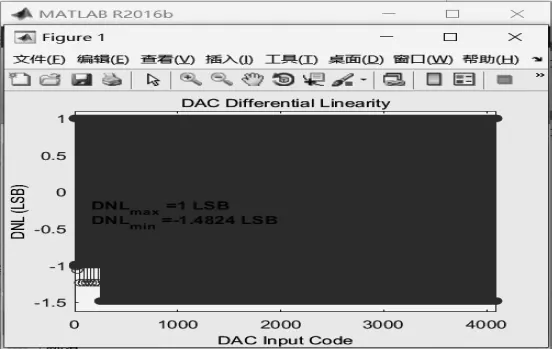

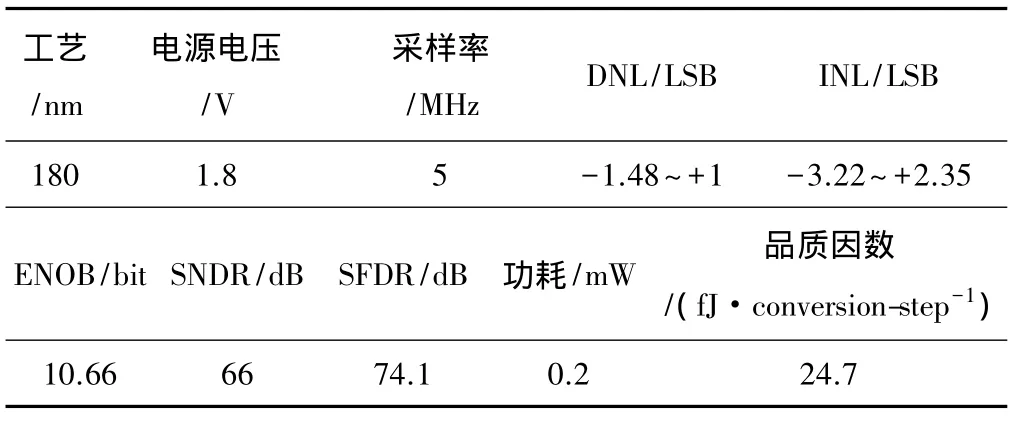

为检测电路的线性度,对电路进行静态仿真。静态参数的主要指标有:微分非线性(DNL)和积分非线性(INL)等。仿真结果如图12、图13所示。具体数值列于表5。

图12 电路DNL仿真结果

图13 电路INL仿真结果

表5 电路仿真结果统计

3.2 动态仿真

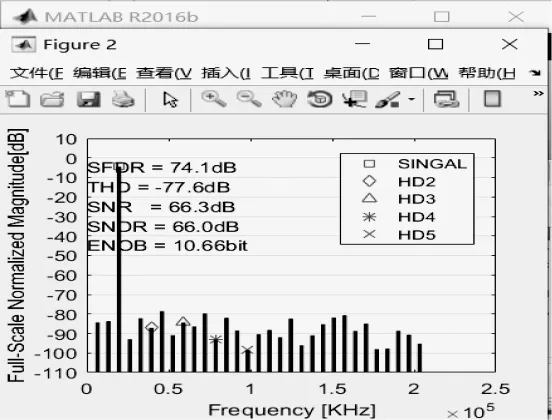

ADC动态参数主要有总谐波失真(THD)、信噪失真比(SNDR)无杂散动态范围(SFDR)和实际有效位数(ENOB)。当采样频率为5 MSPS时,选择频率为195.3 kHz的正弦波为输入信号,仿真结果如图14所示。具体数值列于表5。

3.3 各项仿真结果统计与分析

图14 电路动态仿真结果

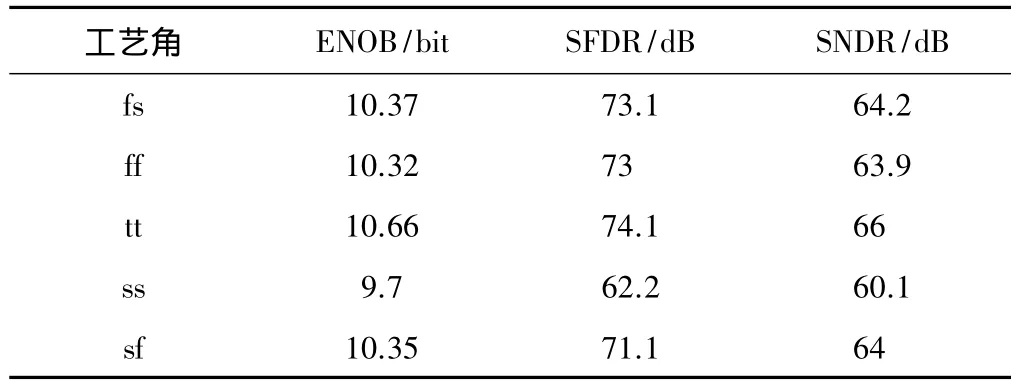

将电路参数以及静态、动态仿真结果以及功耗,品质因数(FoM)进行整理,如表5所示。由表5与表2对比可知,仿真结果满足设计要求。同时,功耗为200 μW,品质因数仅为 24.7 fJ/conversion-step,性能较好。对电路进行5个工艺角下的仿真,如表6所示,仿真结果稳定。

表6 工艺角仿真结果

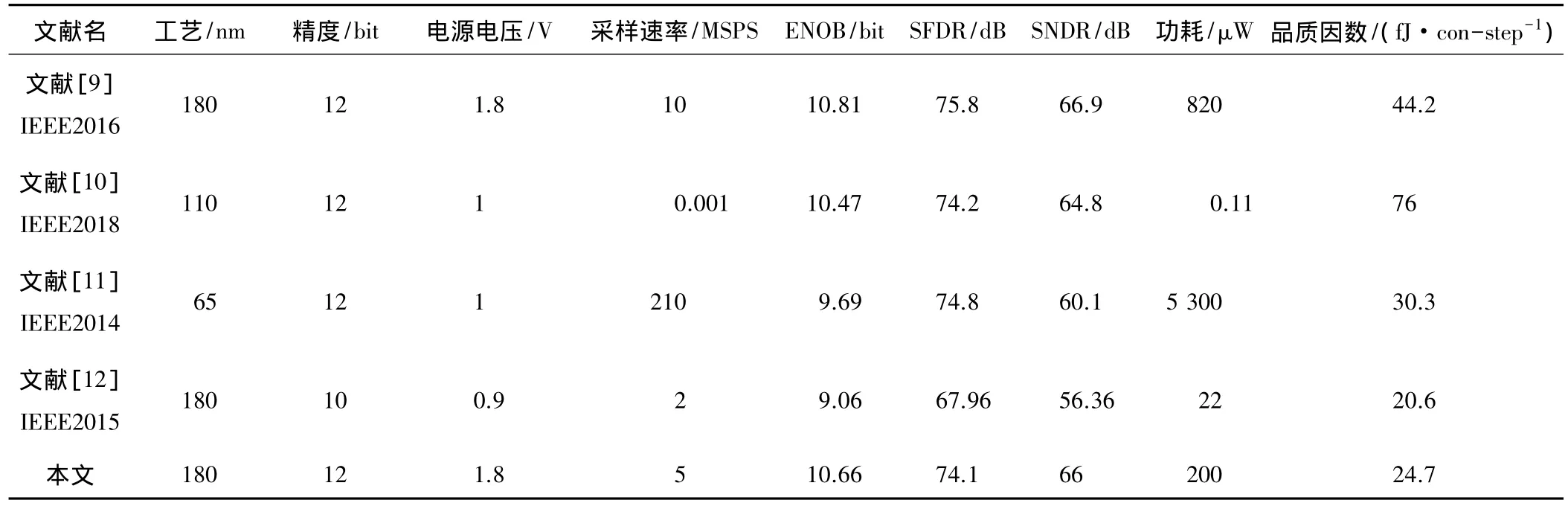

将本文仿真结果与近五年IEEE SAR ADC论文进行对比,如表7所示。与Liu S所著论文[9]相比,本文ENOB较差,但功耗较低,FoM更好;与Mao W所著论文[10],Lin C 所著论文[11]相比,本文动态性能更佳,品质因数也更高;与Zhu Z所著论文[12]相比,本文品质因数较差,但ENOB、SFDR、SNDR等几项参数,本文都较高;综合对比可知本设计性能较好,品质因数较高。

表7 本文仿真结果与近五年论文对比

4 结束语

本文提出一款适用于红外探测微测辐射热计的SAR ADC,该ADC具有低功耗高精度以及高采样率等特点。本文通过对电容阵列DAC的创新设计,比较器及数字电路的优化设计,使电路达到较高的性能,满足本课题组微测辐射热计的片上集成ADC设计要求。