数字中频芯片的仿真研究*

2020-03-22王燕

王 燕

(上海诺基亚贝尔股份有限公司,江苏 南京 210037)

0 引言

随着移动通信的发展,特别是5G 的大规模部署,基站技术在不断演进。网络覆盖理念的核心是将基带处理与射频部分分离,分为基带处理单元(Base Band Unit,BBU)和射频拉远单元(Remote Radio Unit,RRU)两大设备,两者之间通过光纤连接。

数字中频[1]是RRU 的核心部分,作为基带和射频之间的桥梁。它的需求体现在以下几个方面。

(1)基带输出的是刚刚组成帧的信号,单个载波的采样率是一定的,而载波有好几种,每种采样率都不同。因此,要兼容多种载波,需要转换到统一的采样率。E-UTRA 系统可配置的6 种信道带宽,如表1 所示。

表1 E-UTRA 系统可配置的6 种信道带宽

(2)受限于市场上可供选择的器件,中频采样率需要有合适的AD/DA 器件支持。

(3)运营商拥有的频段宽度并不限于一个载波的宽度,通常设计要求支持载波的位置覆盖整个频段,且需要支持同时有多个载波的设计。

(4)信号传输过程中,为了提高传输质量,许多工作放在数字部分可以取得更好的性能。数字部分可以设计出性能更好的滤波器、更准确的功率和相位控制、更准确的设计时延等。此外,现代通信为了提高功放的使用效率,使其在非线性区间也能正常工作,增加了CFR、DPD 等功能,而这些都需要在数字中频完成。

1 数字中频设计概述

典型的数字中频设计框图如图1 所示。

图1 数字中频设计

数字中频分为发射和接收两大块:从基带向射频方向为发射方向,称为下行;反之为接收方向,称为上行。

发射部分的数据流源于基带的成帧信号,CPRI[2]/OBSAI 模块从中提取I/Q 数据流发给成型滤波器。成型滤波器[3]的特点是具有较陡的过渡带和较低的阻带,从而抑制带外泄露。信号经过处理后,频谱形状能满足预期。DUC 即数字上变频,完成的工作主要是内插和滤波。内插在提高采样率的同时会产生频谱镜像,所以需要滤波处理。NCO 合路进行频谱搬移,将载波按需求放置在不同的位置。CFR 即波峰因子衰减,主要是改善OFDM 峰均比过高的缺陷,使得功放在合理动态范围内工作。DPD即数字预失真,使用反馈机制采样输出信号,并用以校正预失真算法,目的在于补偿功放的非线性失真。

接收部分可以看作发射部分的逆过程。值得注意的是AGC 模块,即自动增益控制,可以帮助AD器件实现更精确的量化。NCO 分路功能体现在将所需载波搬移至零频,方便DDC 对载波分选。DDC先滤除带外干扰,然后进行抽取,从而降低信号的采样率,与基带侧保持一致。后经过成型滤波器,最终I/Q 数据通过CPRI/OBSAI 接口发往基带。

2 数字中频仿真

一直以来,滤波器的设计和仿真都是基于matlab实现的,但是对于数字中频芯片,整体层面的RTL代码仿真也至关重要。实际工作过程中,摸索、积累出了一套切实可行的仿真方案。

2.1 数字中频仿真平台

仿真平台[4]的搭建如图2 所示。

图2 数字中频仿真平台

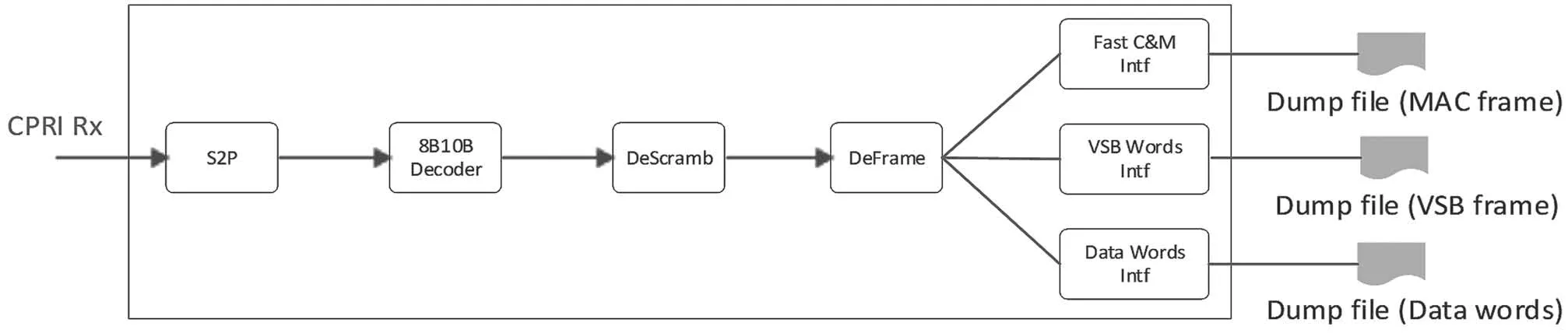

依托CPRI 验证IP 资源,在基带侧通过CPRI接口进行激励,保证双方能够正常同步。I/Q 数据的激励产生既支持sequence,也支持直接load 外部现成的数据文件。整合后的超帧需要经过加扰、8B/10B 的转换,而后经过并串转换驱动DUT,具体见图3。接收方向见图4,主要起到monitor 的作用,可以看作发送方向的逆过程,最终可以得到I/Q数据的dump 文件。

图3 CPRI_VIP 发送方向的处理流程

图4 CPRI_VIP 接收方向的处理流程

射频侧考虑针对DUT 内部的JESD 并口,采集JESD_Rx 接口上的数据,提取出正确的I/Q 数据格式文件;用function 产生或者直接load 外部数据作为激励,转换格式对JESD_Tx 接口进行驱动。

2.2 单音信号激励源仿真

单音信号也就是单一频率的正弦信号。将单音信号作为激励实施对整个数字中频的仿真,是一种简单且切实有效的方式。

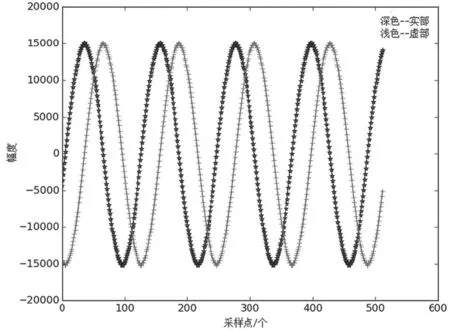

如2.1 章节所述,通过monitor 可以得到输出I/Q数据的dump 文件,但是该文件仅仅是16 bit 的I 数据和Q 数据的罗列,利用肉眼无法得到正确与否的结论,所以还需要借助python 脚本分析数据文件。

对模拟信号来说,可以通过时域分析和频域分析两个面来观察。两者的转换是由快速傅立叶变换(Fast Fourier Transform,FFT)和逆向快速傅立叶变换(Fast Fourier Transform,IFFT)来完成。时域的表示形象且直观,而频域分析更加简练,剖析问题更加深刻和方便,两者相辅相成。

Python 脚本的思想是从dump 文件末尾开始,向前取FFT 所需size 的4 倍数据进行分析,利用python 强大的画图功能,可以直接画出时域的图形;同时,python 也拥有数值计算的扩展库,可以针对数据进行FFT,从而画出频域图形。借助图形,人们可以一目了然地进行观察。

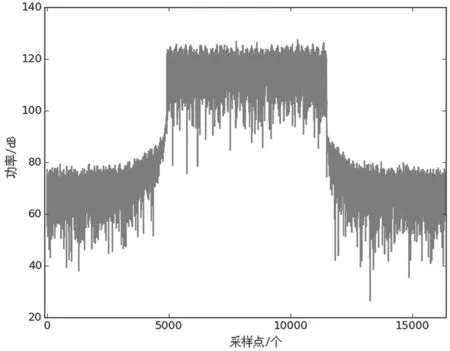

此外,根据给出的SCS 参数、频率、幅度,python 脚本可以计算特定数值点的预期功率,比对之后给出PASS/FAIL 的结论。单音时域波形和频谱,分别如图5 和图6 所示。

图5 单音时域波形

2.3 宽带信号激励源仿真

宽带信号与单音信号相比,可以更准确更全面地反映整个datapath 的功能和性能。实际的困难是仿真代码中要想通过函数直接产生宽带信号比较复杂。

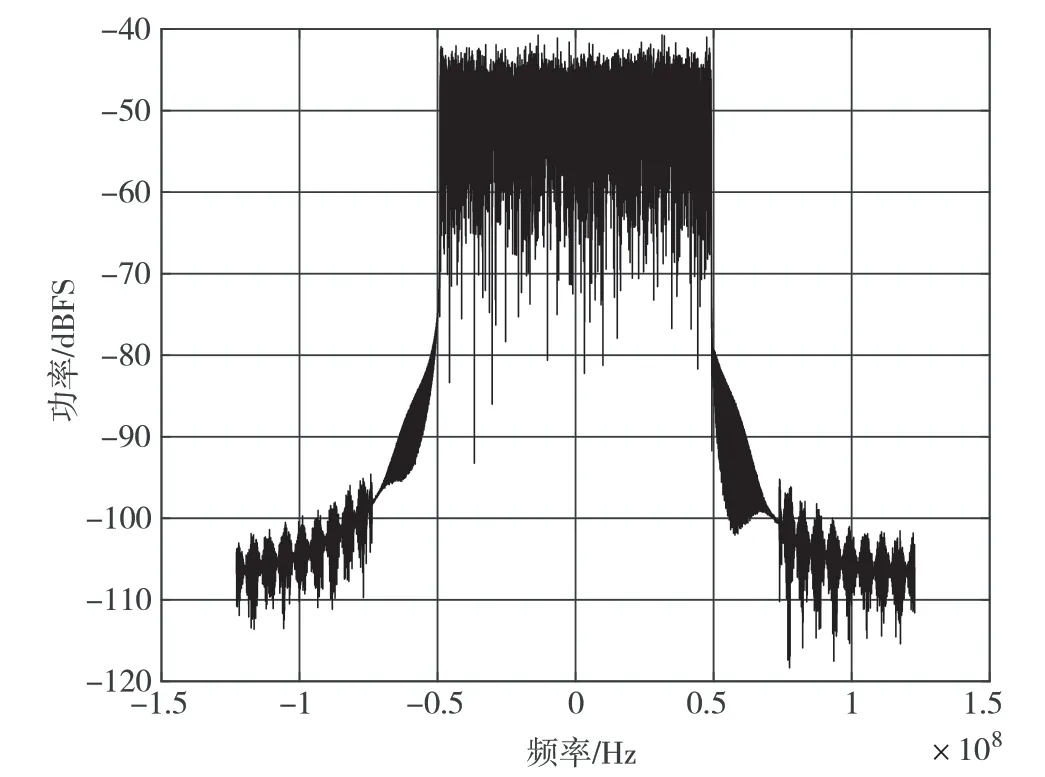

折中的办法是借助matlab[5]生成宽带信号。JESD输入信号以5G NR 100 MHz 为例,信号带宽100 MHz,数据率245.76 MHz,平均功率为-18.22 dBFS,在matlab 中时域波形如图7 所示,频谱如图8 所示。

图6 单音频谱

图7 matlab 100 MHz 信号时域波形

图8 matlab 100 MHz 信号频谱

matlab 产生的信号数据文件可以通过load 的方式加到JESD 输入侧进行激励。基带侧采集数据通过python 脚本画出的时域波形和频谱图(如图9 和图10 所示)满足预期。此外,在python 脚本中还可以进一步计算EVM 等指标,更全面地评估整体性能。

图9 基带侧信号时域波形

图10 基带侧信号频谱

2.4 Delay 仿真

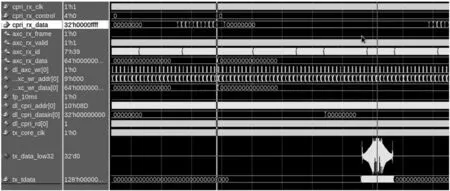

Delay的测量是数字中频测试不可缺少的一环,滤波器的阶数改变等都会引起delay 的变化。如何精确得到内部delay,是仿真研究的重点。

以下行的delay 测量来讲,可以考虑给CPRI接口输入的I/Q 数据进行特殊激励。可以理解为单脉冲,即大部分数据为0,特定一个为0xffff。在经过datapath 处理后,送给JESD 并口的数据呈现为一段较宽的对称非零波形。这里在questasim中,将信号的显示改为十进制,format 选择Analog(automatic),可以呈现为时域波形。以CPRI 接口的脉冲作为起点,JESD 非零波形的中心作为终点,这两者之间的差值即下行delay。

如图11 所示,仿真得到的delay 值可以与实际上板测得的值相互印证,固化后的delay 值在底层软件应用层面起着极为重要的作用。

图11 delay 测量结果

3 结语

仿真贯穿整个数字中频芯片的开发过程。从一定程度上讲,仿真的质量决定了芯片的研发质量。同时,仿真并不局限于对仿真工具的使用、对设计和协议的高度理解,还需要熟练运用各种脚本,如python、perl、tcl、makefile 以及matlab 等工具的辅助,是对综合能力要求极高的一项工作。只有在工作过程中不断创新,不断积累,才能找到更贴合设计的仿真策略。文中所述的仿真研究具有较大的通用价值,对其他数字中频项目的仿真同样有着重要的指导作用。