基于Goertzel 算法的选呼译码FPGA 模块设计*

2020-03-22潘路平何万昊

李 华,王 浩,潘路平,何万昊

(1.中电科航空电子有限公司,四川 成都 611731;2.电子科技大学,四川 成都 611730)

0 引言

提升国产机载电子产品的装机率,确保航电产品供应自主可控,是我国大飞机计划的主要战略目标之一。民航机载选择呼叫系统(Airborne Selcal System)是机载通信系统和应急系统的重要组成部分,功能是向机组人员提供来自地面通信站点的呼叫提示,以类似于“来电提醒”的形式向被呼机组警告接收地面呼叫,从而建立地面与空域内指定飞机的点对点通信。

目前,绝大多数在服役民航客机仍然配置的是模拟电路选呼系统,技术成熟、功能完善且性能稳定,但体积较大且功耗较高,与新型客机航电高集成化的需求不匹配。自研大型民机航电设备在我国尚处于起步阶段,而紧跟全球民机航电数字化、模块化、综合化趋势是必然的研制考量。李锋设计了基于DSP 的机载选呼解码器[1],通过数字计算芯片内嵌选呼程序的方式,一定程度上实现了选呼译码器集成,为进一步深入到芯片化层次奠定了基础;王海丽等设计了基于Goertzel 算法的选择呼叫译码电路[2],实现了Goertzel 算法的应用,初衷是为地勤人员设计一款选呼设备维护训练装置,未对照机载设备研制的适航标准或工业规范。

作为比ASIC 芯片开发灵活度更高的可编程逻辑器件,FPGA 可将硬件设计软件化,是将原由分立常规模拟电路组成的选呼设备压缩集成为一块电路板甚至一块芯片的最佳选择。Goertzel 算法是一种快速DFT 算法,可高效解析特定频点的傅里叶分量。本文提出了一种选呼译码器芯片模块设计的方法,采用Goertzel 算法,实现了将译码逻辑与高速FPGA 芯片设计相结合从而使新设计的选呼译码模块具有体积小、成本低、功耗低、效率高以及性能稳定等优点,预期可替代原传统选呼译码器设备。

1 选呼译码模块功能及原理

1.1 机载选呼系统

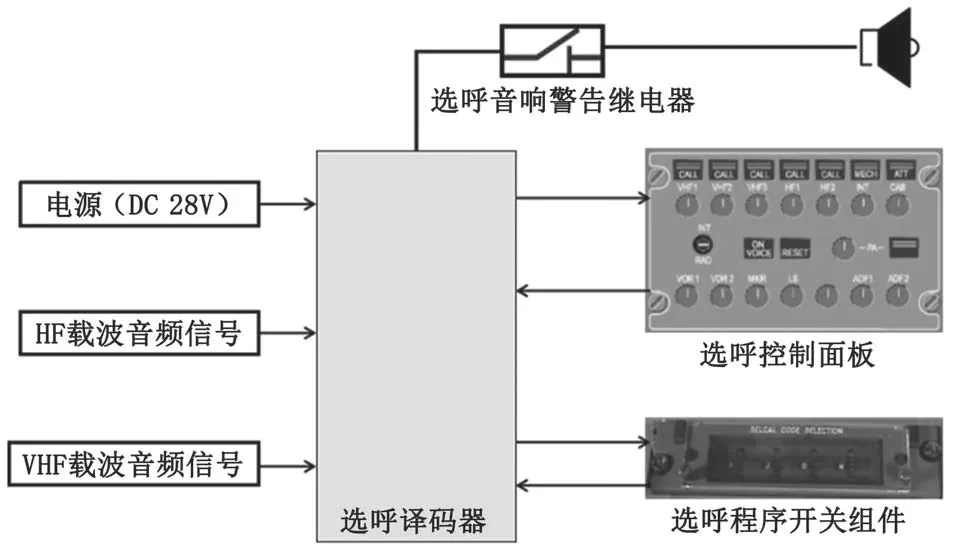

机载选呼系统由选择呼叫译码器(以下简称选呼译码器)、选择呼叫程序开关组件、选呼音响警告继电器和选呼控制面板组成[3],如图1 所示。选呼译码器是选呼系统的核心设备,通过解算地面发出的HF 或VHF 信号中携带的特定音频信号,转化成由4 个字母组成的飞机选呼编码,实现地空一对一通信。

HF 或VHF 接收机接收地面通信站发出的广播信号,选呼译码器解析该选呼码发送至选呼程序开关组建中设置的本机当时选呼码匹配。如果匹配成功,译码器会送出一个离散的呼叫位置信号到选择呼叫控制面板,并触发选呼音响警告继电器,使其向机组发出应答提示。

图1 机载选呼系统

1.2 选呼译码器功能及原理

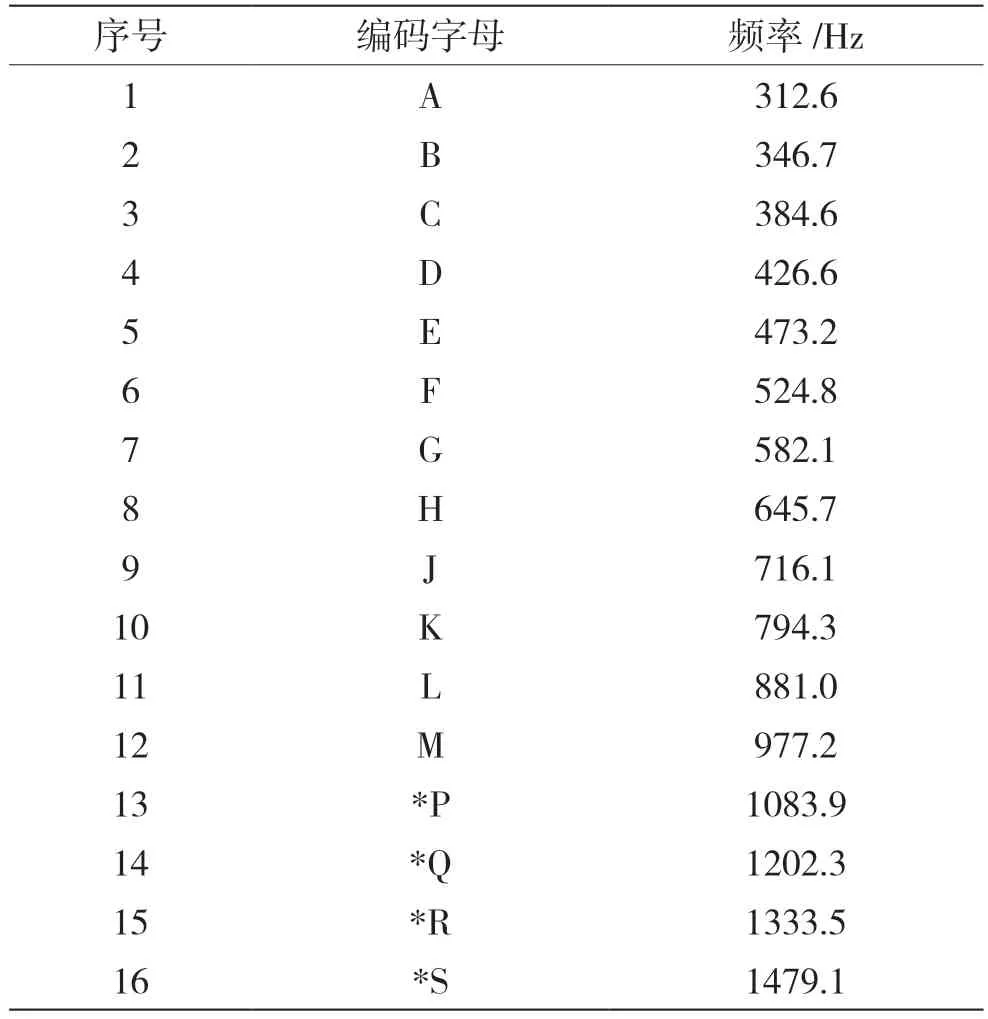

选呼译码器的本质是双音多频(Dual-Tone Multi-Frequency,DTMF)信号解码器。ARINC714-6 详细介绍了选呼编码规则[4]。每架航班的选呼编码都由4 个英文字母组成,每个英文字母对应一个音频频率,如表1 所示。可用与设置选呼编码的字母有16 个,选呼码最大容量为10 920,即10 920 架本地空域飞机同时被呼叫。地面通信站(如塔台)要呼叫空域内某飞机时,将该机编码音频以两组双音多频信号(DTMF)的形式加载到HF 或VHF 上,飞机收到信号后经过译码匹配确认是否呼叫本机。

表1 选呼编码字母及其频率

音频加载时需要遵守一定的规则,可以视为一种音频协议,如图2 所示。每个选呼信号包含两个DTMF 信号,每个DTMF 信号又包含两个字母音频。每个DTMF 信号持续时间为(1±0.25)s,两个DTMF 信号之间的间隔时间为(0.2±0.1)s。每组选呼信号之间的间隔应远大于(0.2±0.1)s,即如图3 中的AC-BD、CA-BD、AC-DB、CA-DB 被视为与AB-CD 为同一编码。

图2 选呼音频协议格式

2 选呼译码算法设计与仿真

2.1 Goertzel 算法

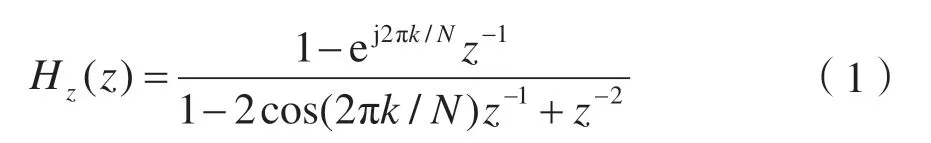

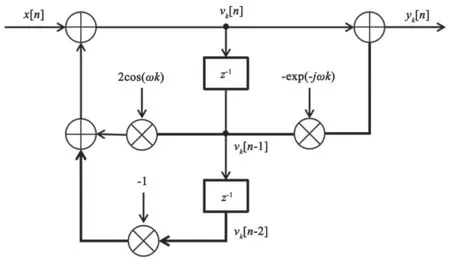

选呼译码器的解算对象是DTMF 信号,包含有特定的频率。Goertzel 算法的主要功能是可迅速准确求得DTMF 信号的DFT值[5]。Goertzel 算法本质上是一个二阶IIR 带通滤波器,传递函数为:

该滤波器对应的传递函数框图如图3 所示。

图3 Goertzel 算法

其中:

根据目标频率f、采样率R与检测区间采样值N和检测区间完整周期数k之间存在的关系:

可将滤波器的递归部分改换为:

其非递归部分则可更新为:

令初值而:

即可解出的目标f的DFT 系数幅度平方为:

可见,基于Goertzel 算法的译码算法逻辑清晰、结构简单,可准确应用于选呼系统的DTMF 信号高能量群目标频率的求解。

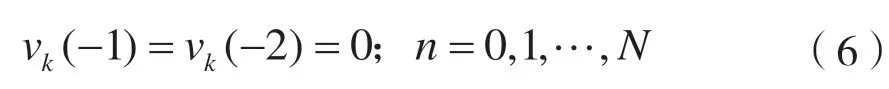

2.2 译码算法流程设计

译码器的本质功能是解算出混合信号中能量最高的频率。为验证Goertzel 算法的译码功能,本设计在MATLAB 中实现了如图4 所示的译码器算法流程仿真测试。

图4 译码器算法流程

在编制算法仿真程序前,先编制独立的Goertzel算法的基本译码模块。该模块不同于MATLAB自带的Goertzel(X,f)函数,分为定点型和浮点型两种,特性各异。定点型侧重于符合FPGA的设计规则,而浮点型更接近真实场景的理想状态。

以前述Goertzel 算法为基础,调用Goertzel 算法的过程可以描述如下。

设译码系数c为一中间变量,满足:

定义N,k;

求解系数c;

迭代求解:

则可解得目标频率的能量值为[6]:

仿真程序运行时,首先进行初始参数的设置和必须的待用参数计算,包括采样率、检测区间的采样值、采样弧度值以及系数等;其次,加入预制的验证音频,并加入一定的干扰噪声;最后,进行16个特定音符的循环解码并输出解算结果。

2.3 MATLAB 算法仿真验证

验证过程开始时,初始化的采样率R设置为8 kHz,采样量N为1 024,则采样周期为128 ms。考虑到信号中断、语音插入等情况,取得实时多路DTMF 信号不便于实验。因此,加入的验证音频为一段特制的57 s 的包含所有字母音符的规范音频。该音频与ARINC 714-6 规定的频率一致,幅度F(电压相对值)随时间变化如图5 所示,具体为AB-CD有4次、EF-GH有4次、JK-LM有4次、PQ-RS有4次。

图5 验证音频

理想的音频解析不能有效评估Goertzel 算法的译码性能,设计中加入了适量噪声成为混合双音多频信号。图6 为含噪声的待译码DTMF 信号。

图6 含噪声的DTMF 信号

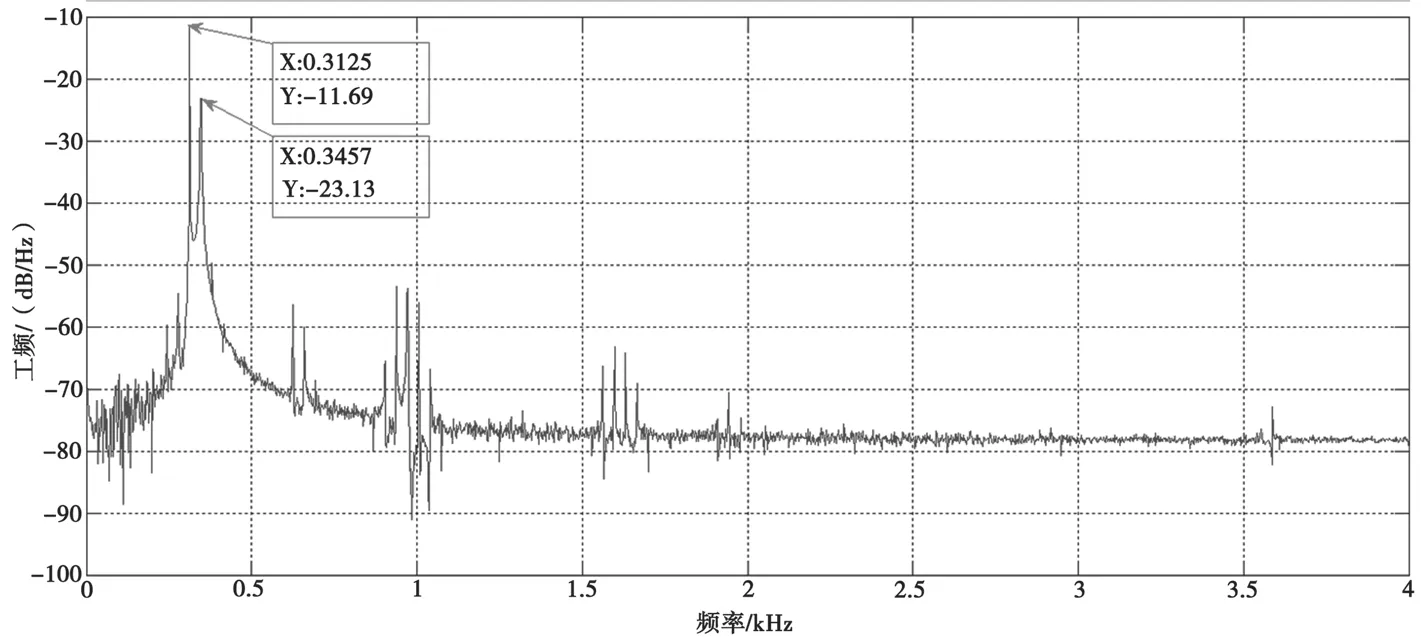

将混合噪声的DTMF 信号输入Goertzel 算法模块时,检测程序循环设定目标频率值,使得译码模块实现“实时”解算信号频率。图7 为解算出第一个双音频信号,即频率为312.5 Hz 的字母“A”(有误差,标准频率为312.6 Hz)与频率为345.7 Hz 的字母“B”(有误差,标准频率为346.7 Hz)。

图7 第一个双音频信号

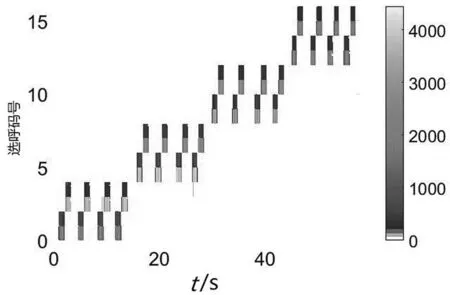

图8 为450 s 内解算出的各频率功率,图9 为与之对应的频率分布。可见,本算法能有效解算出掺杂噪声的DTMF 信号中ARINC 714-6 规定的16个飞机选呼编码基本字母。

图8 功率分布

图9 频率分布

根据上述结果可见,在MATLAB 中的基于Goertzel 算法的译码程序模块可解算出含有噪声的选呼系统DTMF 信号中特定的字母频率。

3 选呼译码FPGA 模块设计与验证

3.1 FPGA 的优点

采用FPGA 是设计先进高集成度、大规模数字电路的主流方案之一,较之于ASIC 设计周期短、成本低,较之于MCU 或DSP 运行效率高、可靠性高。综上所述,应用FPGA 器件设计数字电路系统的主要优点体现为可缩短设计周期、设计更改灵活性高、可降低研发成本、可增大功能密集度以及提高系统可靠性和安全性[7]。

FPGA 设计将硬件研发软件化,以Verilog 硬件描述语言程序代码“模块”为基本单位。设计只需要将选呼译码功能编写为一个Verilog 代码“模块”,即能实现传统机载选呼译码设备的主要功能。将传统的一套设备精简成一段代码或一块芯片,极大地降低了机载设备的空间占用率和功耗,并使得在同一批次设备中不用对物理设备进行重复的逐一验证,也可大幅减轻研制负担。

3.2 基于FPGA 的译码模块设计

研究以面向FPGA 的modelSIM 集成开发环境为仿真测试平台工具开发目标模块。模块中寄存器[0]~[15]分别代表表1 中16 个字母“A”~“S”。通过编制功能模块和测试用例,在modelSIM 中模拟出Goertzel 算法译码DTMF 信号的完整过程。

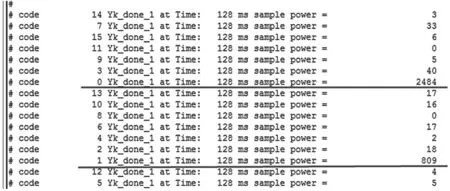

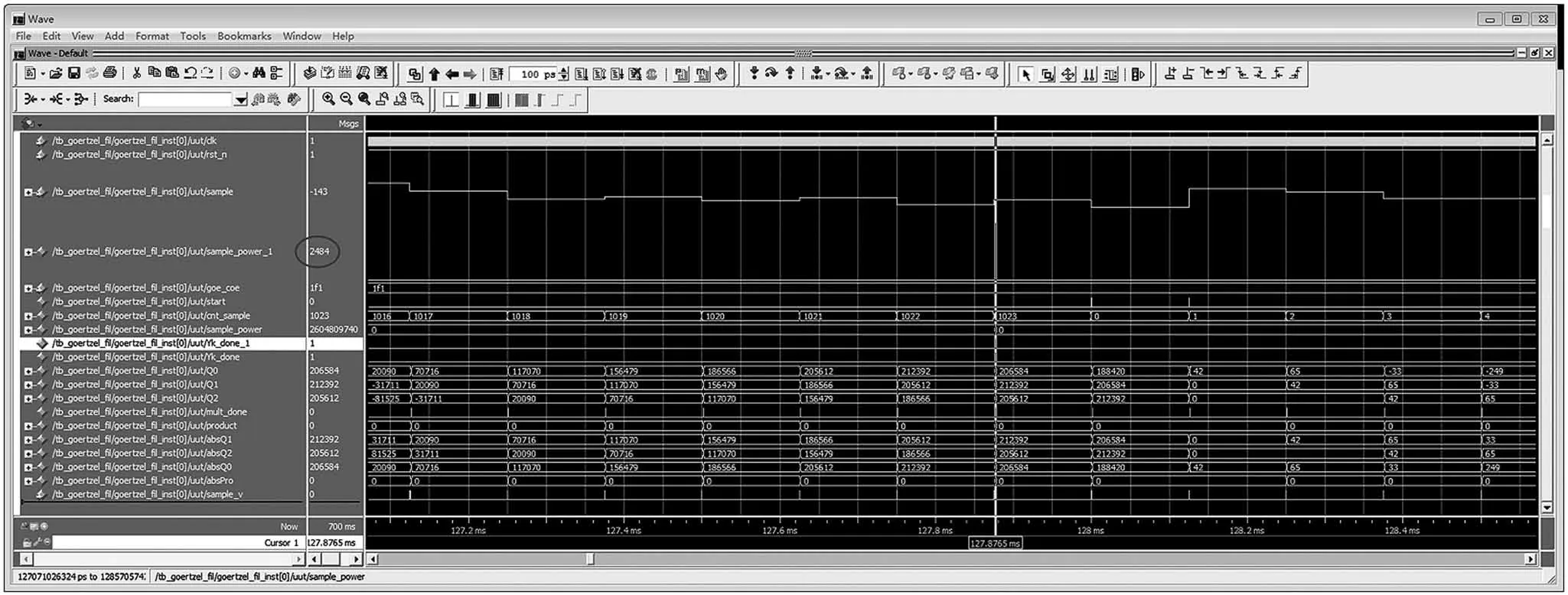

图10 为在700 ms 内仿真器运行译出5 个寄存器“[0]”和寄存器“[1]”,即由字母“A”和“B”组成的双音信号的时序图。明显可见,字母“A”的音频功率高于字母“B”。图11 和图12 的仿真结果为在第128 ms 时刻(第一采样点)的译码情况,其中图11 可见寄存器“[0]”的相对功率(无量纲)为2 484,寄存器“[1]”的相对功率为809,均远高于其他相对功率均小于100 的字母音频,说明本模块可实现DTMF 信号高能量频率的筛选。

图12 中在EDA 左边栏详细显示了字母“A”的译码情况数据,其中字母“A”音频相对功率为2 484,与图11 中列表的功率值相符,说明本FPGA 模块可完整实现选呼译码功能。

4 总结与展望

4.1 总结

本研究以开发基于FPGA 的选呼译码功能模块为目标,通过对Goertzel 算法应用于DTMF(双音多频)信号检测原理的深入研究,设计了针对理想的选呼音频信号(含噪声)的MATLAB 验证程序,并开发了以Goertzel 算法为核心的FPGA 选呼译码器模块,最后通过modelSIM 平台验证了其具备解算选呼信号的功能。

图10 字母“A”的译码时序

图11 第20 ms 时刻的译码情况

图12 字母“A”的译码情况数据

4.2 展 望

本设计实现了基于Verilog 语言的选呼译码功能模块设计,模块可作为一种IP 核直接在集成式选呼系统的设计过程中采用,可提高新型航电设计效率。但是,本模块仅完成了选呼译码功能实现,其性能和精度还需要与硬件设备结合进行深入测试和调整。根据ARINC 714-6 相关的适航要求,选呼译码模块应围绕以下几个方面进行性能和精度调试:

(1)译码模块可解算出两个相等量的3 dB 之内的调制音频,无论该音频是否符合选呼规则;

(2)译码模块可解算出具有标称调制90%(不低于60%)的音频包络;

(3)译码模块可容忍编码音频频率±0.15%的公差,以确保译码工作正常;

(4)译码模块可容忍编码音频频率±15%的失真率,以确保译码工作正常。