28nm 工艺基于T_Coil 结构的带ESD 防护器件的高速IO 设计∗

2019-11-29张博翰陈建军朱小娜

张博翰 陈建军 梁 斌 罗 园 黄 俊 朱小娜

(国防科技大学计算机学院 长沙 410000)

1 引言

根据美国国家半导体公司(National-Semiconductor)统计数据表明,集成电路失效产品中的37%是由静电放电现象/过度电性应力(Electrostatic-Discharge/Electrical-Over-Stress,ESD/EOS)所引起的[1]。ESD 是指两个带有不同电荷量的物体相互接触时,电荷在两个物体之间发生的电荷转移现象。在集成电路领域,当集成电路芯片的管脚与不同物体相互接触并发生电荷转移时,就会产生静电放电电流。这种静电放电电流远远大于集成电路芯片正常工作时所需要的电流,通常会高达几安培到几十安培并产生几伏到几十伏的静电放电应力,从而导致芯片内部核心电路中的相关组件发生软失效或硬失效,并引起芯片性能乃至整个系统性能的瘫痪[2~3]。

现如今,随着集成电路技术的发展,CMOS 器件不断突破“物理极限”,电子器件的速度越来越快,尺寸越来越小,抗ESD能力持续减弱,而同时电子器件的密集程度越来越高,这就使得ESD问题在当今的工业中变得更加重要。为了提供合理的ESD 防护性能,在ESD 防护技术中,ESD 防护电路必须包含抵抗瞬间放电电流的大型器件,比如高阻值的电阻、电容或者二极管等。结果ESD防护电路引入了大量的寄生电容,严重影响了高速IO 电路的速度,限制了带宽。所以在保证ESD防护能力的条件下,同时使高速IO 电路具有高速度,宽带宽,成为集成电路设计领域的关键性难点。

当前集成电路领域已经普遍认识到静电放电现象(ESD)对高速IO电路的设计有非常大的影响,各半导体公司和各高校都投入物力和人力来尝试解决这一问题。与国外相比,国内在ESD防护方面的研究不够深入,技术积累不足,同时国内对于28nm 工艺的集成电路设计技术还不成熟,特别是对带ESD 防护器件的高速IO 设计的研究还比较缺乏。设计一款28nm 工艺下基于T_Coil 结构的带ESD防护器件的高速IO,既可以通过T_Coil结构有效提高设计带宽,又可以进行纳米技术下的集成电路的ESD防护器件的研究。因此研究28nm工艺下基于T_Coil 结构的带ESD 防护器件的高速IO 设计具有较大的研究意义。

2 带ESD防护器件的高速IO电路

与传统电路相比,高速IO 电路具有速度高,密集程度高,对ESD应力敏感的特点。这些特点使得高速IO 设计的ESD 保护电路必须满足几个更加困难的标准,即这些电路应该满足:1)尽管ESD 保护器件本身具有寄生电容,但仍能保证电路具有宽带宽;2)占用面积是合理的小区域,这样可以将数十或数百个这样的器件集成在芯片上,而不会使布局和布线复杂化;3)在输入端和输出端具有良好的阻抗匹配,以避免破坏高速数据;4)表现出可忽略不计的中频带损失[4~7]。

本章回顾两种以最小化ESD 寄生电容为目的的传统高速IO 设计思路,结合高速IO 电路对ESD防护器件的要求,分析其优缺点。然后介绍T_Coil结构与之进行比较。为了简化分析,约定ESD防护器件的等效电容CESD=1.2pF且负载电阻R=50Ω。

2.1 感应峰值技术

感应峰值技术在低噪声领域有非常广泛的应用,它在只占用很小的面积的前提下,可以给电路提供非常可观的带宽增益。这种特性使得感应峰值技术很适合应用在带ESD 防护器件的高速IO 设计。事实上,在带宽应用中,感应峰值可与片上终端电阻一起使用,以扩大整个电路的信号带宽。图1 展示了这种设计方案。虽然这种设计方案在超调可忽略不计的情况下将速度提高了近40%,但是感应峰值技术的阻抗匹配性很差,很容易损坏高速数据[8]。

图1 采用电感峰值技术设计的输入电路

2.2 分布式ESD

分布式ESD,即解决阻抗匹配问题的宽带技术沿着传输线(T 线)分配ESD 保护器件,如图2 所示[9]。

分布式ESD 结构可以很好地满足高速IO 对ESD 保护电路的特殊要求中的两个,即较宽的带宽和良好的阻抗匹配。然而,分布式ESD技术在信号损耗、ESD 总电容与分布式结构的总面积之间存在严重的折衷。例如,对于CESD=1.2pF,传输线引入了大约6dB 的中频带损耗。并且,即使经过多次折叠,传输线的长线结构也会导致其他信号的布局和布线出现问题。此外,ESD 总电容的折衷会导致整个电路的电压耐受力下降,即电路的ESD防护能力被降低。更为严重的是在实际生产中,传输线的串联电阻可能不允许ESD 器件在不同的引脚之间均匀分布。结果,IO 焊盘附近的ESD 器件可能会首先断开,使得电路其他部分承载大电流并使电路损坏。也就是说,分布式ESD结构真正的ESD防护能力比预期要弱很多。

图2 分布式ESD结构[9]

2.3 T_Coil结构

如图3 所示,T_Coil 结构由两个具有相同的耦合系数k 的耦合电感器L1和L2以及桥接电容器CB组成。输入端施加到端口A上,终端电阻RT连接到端口B上,负载电容CL连接到端口X上。

相比感应峰值技术和分布式ESD,T_Coil 结构提供了两个在带ESD 防护器件的高速IO 电路设计中非常有用的特性。首先,电路具有良好的阻抗匹配,如果设计得当,电路会显示纯电阻输入阻抗Zin=RT,而与频率和负载电容CL的取值无关。这可以通过识别在低频率下,耦合电感器L1和L2减少对终端电阻RT 的输入或在高频率下,桥接电容器CB在L1和L2导通时起到相同的作用来分析出来。

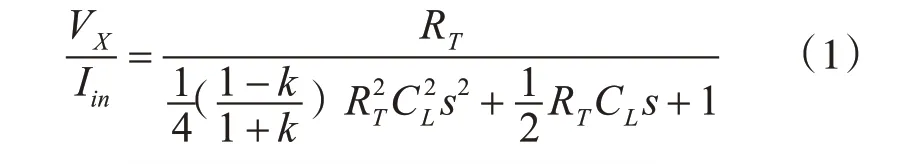

其次,T_Coil 结构比感应峰值技术更大程度地增强了IO 电路的带宽。T_Coil 结构的传递函数由式(1)给出:

图3 T_Coil结构[11]

对于k=1/2的均匀延迟,带宽扩大了2.72倍,比具有相同类型相应的感应峰值技术提高了70%。此外,T_Coil结构提供了非常适合部署ESD 防护器件的环境,其中ESD防护设备可以取代负载电容CL和终端电阻RT用作片上终端电阻器。这不会导致电路的布线和布局复杂化。

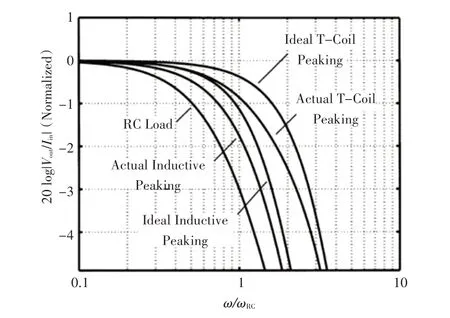

图4 五种模型比较[11]

图4 描述了三种网络结构的传递函数:一阶RC 负载、具有理想或真实电感器模型的感应峰值以及具有理想或真实T_Coil 结构的T_Coil 模型。假设每个网络结构都是由理想的电流源驱动,频率归一化为原始带宽。可以看到T_Coil 结构优于感应峰值,并且即使在理想情况下,T_Coil 也能达到50%的峰值。对于具有真实T_Coil 结构的T_Coil模型,电路也显示出高质量的匹配。

3 电路设计

图5 显示的是基于T_Coil 结构的带ESD 防护器件的高速IO 设计原理图。为了实现8GHz 的预期带宽,设计采用两个T_Coil 结构,使用差分结构输出,用来消除共模噪声,其中L1和L2是耦合系数为k 的两个完全相同的耦合电感器,CB是桥接电容器。输入端施加到端口A上,终端电阻RT连接到端口B 上,负载电容CL连接到端口X 上,终端电阻设定为50Ω。其中ESD 防护器件取代负载电容作为终端电阻器,CESD表示的是ESD 防护器件的等效电容。

图5 电路设计原理

3.1 电路设计

图6 显示的是本文完成的28nm 工艺下基于T_Coil 结构的带ESD 防护设备的高速IO 设计的电路整体设计,使用Cadence Virtuoso 软件设计完成。图6 的左半部分是整个电路的激励信号部分,激励信号部分分为上下两个部分,上半部分电路的整体信号激励,包括输入电流激励、全局电压激励以及两个交流信号输入激励。下半部分是可变电阻阵列的控制信号,包含三个高电平和三个低电平信号。图6 的右半部分是T_Coil 结构模块和ESD防护模块。因为在设计方案中ESD 防护器件与T_Coil 结构中原有的负载电容CL一同构成T_Coil结构的负载部分,所以在设计方案中T_Coil结构模块和ESD 防护模块封装成顶层模块。在前文中提到,T_Coil结构在阴极射线管的高速接口芯片上有了广泛的应用,并且T_Coil结构提供了非常适合部署ESD 防护器件的环境。所以在设计方案中我们采用T_Coil结构来实现高速IO设计,在输出端口X上挂ESD防护器件。

图6 方案整体电路设计

图7 T_Coil结构模块

图7 显示的是T_Coil 结构模块,模块包含两个T_Coil 结构,为实现差分信号,两个T_Coil 结构的器件参数是完全等同的,电感器L5和L6用作T_Coil结构的耦合电感器,输出端连接到耦合电感器的中轴位置。终端电阻设计为可变电阻阵列,阻值为50Ω。电流输入采用电流镜结构,将输入电流放大120 倍。输入信号的信号输入负载为36 个NMOS管并联在一起做放大管。ESD 防护器件是挂在输出端的。如图8 所示,ESD 防护器件采用反向二极管结构,因为二极管具有正向电流导通、反向电流阻断的特点,ESD 产生的瞬间放电电流会击穿二极管,从而保护集成电路芯片不被瞬间放电电流破坏。本文所采用的反向二极管技术可以达到2000V的抗ESD性能。

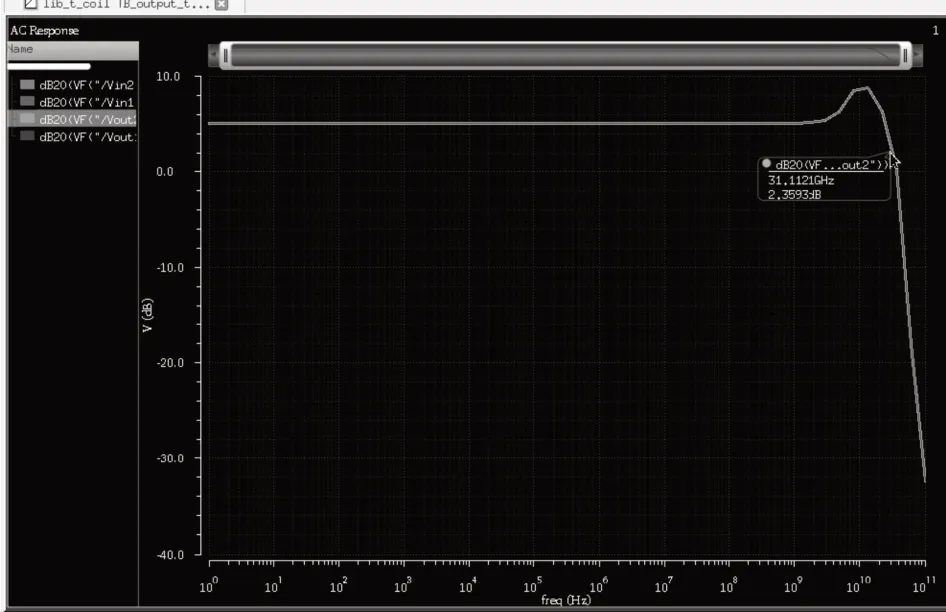

3.2 功能性能仿真

为了验证设计是否达到要求,使用ADE L(Analog Design Environment L,Spectre 的图形界面版仿真工具)进行功能性能仿真。首先检测频域表现,设定仿真温度27℃,仿真模式为ac,扫描范围1G~100G,仿真结果见图9。如图所示,频域表现为一条曲线,平行部分为5dB,表明电路是正增益,在2dB 点看到电路表现出的带宽是31.112GHz,比预期的8GHz 带宽大很多。然后检测时域表现,仿真时间为100ns,选取的仿真模式为moderate。图10显示时域的仿真结果,可以看到输入信号完全对称,输出信号比输入信号的电压值要高,仿真结果达到预期。

图8 ESD防护电路

图9 电路速率和增益仿真图

图10 时域表现图

4 版图设计

图11 电路整体版图设计

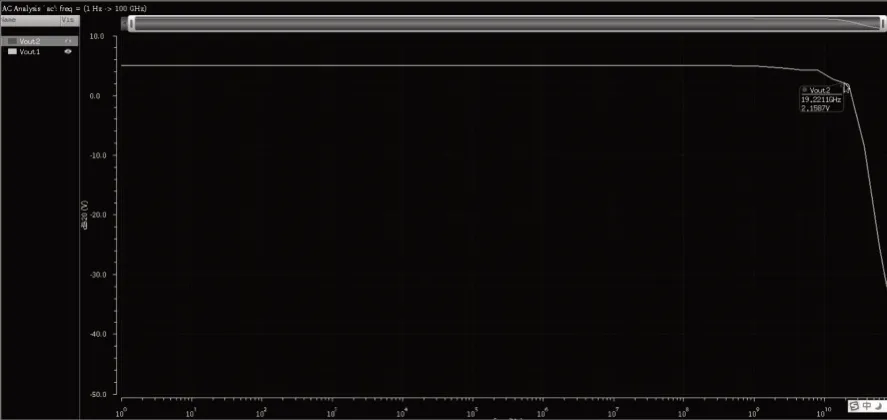

图12 版图的频域仿真图

版图是在掩膜制造产品上实现电路功能且满足电路消耗、性能等的物理实现,从版图上可以减少工艺制造对电路的偏差,提高芯片的准确性。图11 显示的是图6 所对应的版图设计。使用ADE_L仿真工具对版图进行带寄生参数的仿真,将版图的寄生参数提取出来并转成Calibre View 文件,完成准备工作以后将带有版图寄生参数的Calibre View文件映射到电路图中,然后进行仿真。频域表现见图12,电路表现出的带宽是19.221GHz,比电路设计差30%左右。时域表现见图13,仿真结果符合预期。

图13 时域表现图

5 对比

与传统技术相比,T_Coil 结构可以在保证ESD防护能力的前提下很好的提高设计的带宽。图14展示的是采用传统技术完成的高速IO 设计所达到的性能。为了便于比较,两种设计方案的输入激励信号和ESD防护器件完全相同。可以看到,在传统技术下,电路的带宽为26.402GHz,与T_Coil结构相比带宽减少了15%。

图14 时域表现图

6 结语

本文对带ESD 防护器件的高速IO 设计进行了研究,讨论了高速IO 电路的特点和其对ESD 防护器件的特殊要求,回顾了两种以最小化ESD寄生电容为目的的传统技术。针对传统技术存在的问题,本文采用T_Coil 结构设计高速IO,完成28nm 工艺下基于T_Coil 结构的带ESD 防护器件的高速IO 设计。使用Virtuoso 软件完成了高速IO 的电路设计和版图设计,使用ADE_L 仿真工具进行功能性能仿真和带寄生参数的仿真,电路图带宽为31.112GHz,版图带宽为19.221GHz,设计符合8GHz带宽的预期。