基于FPGA的VME总线监视模块的研制

2019-09-12

(1.中国人民解放军第五七二〇工厂,安徽 芜湖 241007; 2.南京航空航天大学 自动化学院,江苏 南京 210016)

VME总线[1]全称为VERSA Module Eurocard Bus,是在VERSA总线的基础上扩展演变而来的。经历几十年的发展,虽然不如PCI、USB等总线应用广泛,但仍凭借其高性能、支持多处理计算机系统等优势在航空航天领域大范围应用。文献[2]介绍了早期VME接口芯片VIC068A/VIC64;文献[3]~文献[5]介绍了应用VME接口芯片的方式。

为满足后续新机VME总线模块电路板深修的需要,迫切需要加强对VME总线数据监视方面的研究。本文在对VME总线通信规范进行深入分析的基础上,基于Altera公司FPGA的Nios II嵌入式处理器[6-8],设计并研制一块VME总线监视模块,测试结果表明其有效性。所研制的VME总线监视模块能够为后续新机型中VME总线模块的测试与修理提供技术支撑。

1 VME总线规范分析

本节介绍VEM总线系统基本架构。VME总线主要由4部分构成:数据传输总线、数据传输总线仲裁总线、优先中断总线和公用总线。图1为VME总线架构。

① 数据传输总线。VME总线的数据传输总线执行异步并行传输。由于为异步传输所以在数据传输总线中存在一些控制信号,表明传输发起、已完成或无法完成等状态。其主要信号线如表1所示。

② 数据传输总线仲裁总线。由于VME总线支持多个处理器,也就存在同一时刻多个处理器需要占用

图1 VME总线架构

信号线名功能A1~A31高31位地址信号线D0~D3132位数据线AM0~AM5地址修改线,用于传递附加信息LWORD长字信号线DS0、DS1数据选通线AS地址选通线,表明地址有效WRITE读写线,表明读或写操作BERR错误线,表明传输未能在规定时间完成DTACK传输应答线,表明传输被应答RETRY表明传输不能在此周期内完成

数据总线的情况。数据传输总线仲裁总线用于在此情况下决定谁先占用数据总线。

④ 公共总线。公用总线为系统提供时钟、初始化及故障检测等功能。

2 硬件电路设计

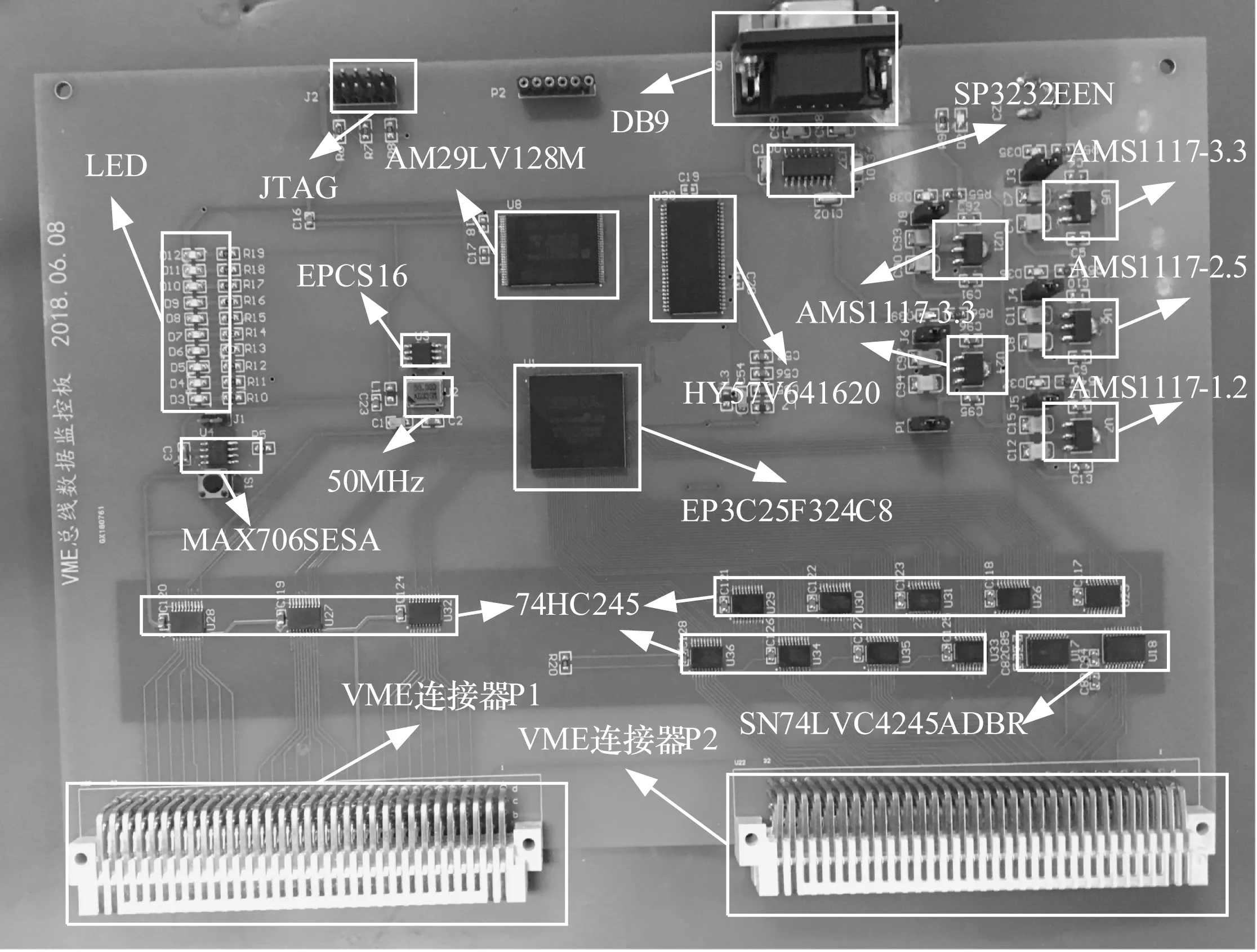

图2为模块硬件结构,整个模块包含5个部分:FPGA最小系统、Flash电路、SDRAM电路、总线缓冲电路、串行接口电路。

① FPGA最小系统设计。本设计所选FPGA为EP3C25F324C8,以其为基础介绍其最小系统电路设计。具体包括时钟电路、复位电路、JTAG电路、配置电路以及其它电路的设计。其中时钟电路由一个50 MHz的有源晶振产生;复位电路由一个低电平复位芯片MAX706SESA产生;配置器件选用EPCS16器件;其他电路具体包括FPGA电压(包括VCCIO、VCCA以及VCCINT电压)供给、指示灯等电路。

图2 监视模块硬件结构框图

③ SDRAM电路设计。本设计采用的HY57V641620ELTP-5是一款容量为8兆字的CMOS同步DRAM。该器件采用时钟上升沿完全同步操作。所有输入和输出都与时钟输入的上升沿同步。

④ 总线缓冲电路设计。VME总线的数据、控制信号通过8位总线传输器74HC245与FPGA相连接。VME总线中数据传输总线仲裁总线、优先中断总线的菊花链信号通过8位总线传输器SN74LVC4245与FPGA相连接。

⑤ 串行接口电路设计。本设计串行接口电平转换选用器件SP3232EEN。SP3232EEN是一款RS-232收发器,适用于便携式应用。

3 模块软件设计

由于模块软件以SOPC为核心搭建,主要包含两个部分:FPGA片内逻辑与SOPC应用软件。

3.1 FPGA片内逻辑

VME监视模块FPGA片内逻辑架构如图3所示,总共有2部分组成:SOPC系统和信号采集模块。SOPC系统中的通用Flash控制器和SDRAM控制器实现与外部存储连接,PIO控制器实现从信号采集模块获得数据,UART控制器则负责将采集到的信号向外传输。信号采集模块负责VME总线地址、数据及控制信号的采集。

图3 VME监视模块FPGA片内逻辑架构

(1) SOPC系统配置。

本设计采用平衡型(NIOS II/s),并配置JTAG调试接口等级为等级1,JTAG调试接口功能设置为JTAG目标模块、下载软件数据和软件断点。由于本设计将软件程序存储于Flash中,程序复位加载位置设置为CFI Flash控制器。意外加载位置设置为SDRAM控制器。

本设计中为SOPC添加的外设接口主要包括:

① SDRAM控制器。根据所选SDRAM型号HY57V641620ELTP-5设置参数SDRAM控制器结构参数:数据位宽为16位;存在1个片选、4个块结构;地址线行宽为12位、列宽为8位。时间参数:列选择(CAS)延时为3个时钟周期;上电后初始化所需要的延时2个周期;刷新时间间隔为15.625 μs;上电到开始初始化之间的延迟时间100 μs;刷新时间为70 ns;预充电时间为20 ns;列有效与行有效延迟为20 ns;数据端口数据保持时间5.5 ns;写恢复时间14 ns。

② CFI Flash控制器。Flash芯片与Avalon接口通过一个Avalon三态桥相连接。本设计采用的片外存储闪存为AM29LV128M,通用闪存接口设置中对此器件已有预设参数,直接设置为AM29LV128M123R_BYTE的预设参数。

③ PIO控制器。PIO控制器是Avalon从接口与I/O端口间的存储器映像连接口。PIO控制器能产生基于输入信号的中断请求。每个PIO控制器可提供32个I/O端口。本设计一共配置了7个PIO控制器,如表2。

④ JTAG UART核。JTAG UART核是PC主机与SOPC Builder系统间通信的一种方式,常用作系统调试。

⑤ UART核。UART核为具有Avalon接口的通用异步接收/发送器。其可实现RS-232协议,设置波特率、奇偶校验位、停止位、传输的数据位以及其他可选的RTS-CTS流控制信号等。

⑥ EPCS设备控制器。Nios II通过EPCS控制器访问Altera的EPCS串行配置芯片。

表2 PIO控制器列表

(2) 信号采集模块。

该模块主要对VME总线上有效的数据、地址信息进行采集,缓存至64位FIFO,并最终通过PIO接口传输至SOPC系统。该模块主要对VME总线上,有效的数据、地址信息进行采集,缓存至64位FIFO,并最终通过PIO接口传输至SOPC系统。

由于VME总线上有效电平宽度均高于40 ns,而FPGA逻辑工作频率为100 MHz。为了防止电平抖动对数据采集造成影响,每一个信号的电平都必须保持3个周期稳定,才被认定为有效电平。

图4 信号采集模块解析VME总线信号流程

图5 VME主模块写入信号采集模块监视仿真

图6 VME主模块读取信号采集模块监视仿真

3.2 SOPC应用软件

当pio_control_i输入信号出现上升沿触发中断,SOPC软件进入接收信号采集模块数据流程。SOPC系统首先将PIO控制器pio_control_b、pio_control_f所控制I/O端口输出高电平,代表SOPC正在接收数据,且处于忙状态。之后将pio_data、pio_addr、pio_dir输入的数据按顺序依次存入32位缓存数组,且缓存数组中每存入一个输入计数+1。每次输入计数+1后需要判断计数是否超出范围,若超出则计数清0。当将数据、地址、方向全部存入缓存数组后,此次接收周期完成,SOPC系统将PIO控制器pio_control_b、pio_control_f所控制I/O端口输出低电平,表示SOPC系统不忙,传输完成,可进行下一次传输。

在无中断发生情况下,SOPC软件循环检查输入计数是否等于输出计数,若不相等,表示缓存中有串口未发出的数据。串口发出缓存数组中第输出计数个数据,在检查UART核status寄存器状态是否完成发送。发送完成后,输出计数+1。每次输出计数+1后需要判断计数是否超出范围,若超出则计数清0。图7为SOPC应用软件运行流程。

4 模块功能验证

图8为VME总线监视模块功能验证总体架构。运用MVME3100作为VME总线主控模块,发起对自身VME总线从空间的数据传输。当监测模块到传输时,将传输数据通过SDRAM保存,并通过串口将传输数据发送至上位机。图9为VME总线监视模块实物。

MVME3100在初始化中将PCI地址空间0x80000000~0x800fffff映射至VME总线空间0x08000000~0x080fffff。本实验通过对VME总线空间0x08000000~0x080fffff进行数据读写。通过自定义函数实现对VME总线空间的连续数据写入,且写入数据依次递增。

自定义函数参数定义如下:

STATUS testPCItoVME32(

INT32 address, //数据写入的初始VME空间地址,从该地址起依次向高地址写入数据

INT32 data, //写入VME空间的第一个数据,此后每次写入的数据,在data值基础上累加

int n //写入数据个数

)

图7 SOPC应用软件运行流程

图8 模块功能验证架构

图9 VME总线监视模块实物

图10为VME监视模块整体功能验证举例。该例实现了对由VME空间地址0x8000000开始的连续100次传输的监视。传输地址、数据依次递增。

图10 VME监视模块整体功能验证举例

5 设计过程中应注意的方面

在VME总线监视模块的研制过程中,应注意以下几个问题:

② 在基于NIOS II的SOPC架构搭建过程中,由于FPGA内部逻辑的延时影响,所以NIOS II输入时钟与输入SDRAM应存在-75°相角差。

6 结束语

本文在系统掌握VME总线通信过程与协议的基础上,针对目前国内外VME总线的研制现状,研制出一种基于FPGA设计了VME总线监视模块,对该模块的功能进行试验验证,结果表明其有效性。