机载PLD大规模组合逻辑反求装置的研制

2019-09-12张子明许劭晟2周勇军李珊珊李金猛张小辉

张子明, 许劭晟2, 周勇军, 李珊珊, 李金猛, 张小辉

(1.中国人民解放军第5720工厂 航空设备测控与逆向工程实验室,安徽 芜湖 241007; 2.安徽师范大学,安徽 芜湖 241002)

随着电子技术的飞速发展,大量的可编程逻辑器件(如GAL、CPLD、FPGA等)取代逻辑门芯片应用于机载电路板,受限于技术资料封锁等因素,空军修理企业无法获得这些器件各输出引脚与各输入引脚的组合逻辑关系,既难以分析电路板的工作原理,也不能对其内部软件进行备份,给航空机载设备电路板的维修保障工作带来一定的难度。

传统意义上在制造业领域的反求工程,具体是指在设计理论和技术等支持下,相关人员通过一定的手段对设计出的新产品进行透彻的分析和改进,这既是对原始设计的一种提升,也可以成为再设计[1]。结合快速发展的激光技术和数控技术,反求工程正在成为汽车、航空航天、模具、玩具、船舶等工业领域产品设计制造的重要手段[2]。另外在维修领域,反求工程已应用于飞机导管[3]、水轮机转轮[4]的维修以及1553B总线信号接口定义反求[5-6]中。但是在制造和维修领域,反求工程主要应用在机械产品,电子产品尤其是芯片级的应用相对较少。

数据的精简、筛选与优化是反求工程的关键技术[7-9],笔者提供了一种基于输入遍历得到大数据的反求工程方法。组合逻辑反求模块通过一套硬件装置,遍历目标逻辑芯片的各种输入情况,采集对应的输出后传输到上位机,研究设计反求算法,再通过上位机将反求算法用高级语言编写为可执行程序解析采集到的海量数据,从而求出芯片内的大规模组合逻辑关系。

1 总体方案结构

1.1 装置功能分析

所研制的组合逻辑反求装置包括上位机软件和下位机两个部分,其功能如下。

(1) 上位机软件。

① 基于C语言编写的组合逻辑反求算法软件,用于根据输入遍历获取的输出数据来求解并输出内部组合逻辑关系。

② 基于VC++编写的串口软件,用于发送指令和获取输入遍历,而对应的输出数据并保存为文本文件形式。

(2) 下位机。

① 被测板即各种PLD的测试夹具,被测板测试各种主流可编程逻辑器件,包括GAL、CPLD、FPGA等,为了方便逻辑注入,被测板还搭建好了逻辑器件的最小系统。

② 测试板由FPGA为控制器产生各种输入情况,在提供被测板输入后采集相应的输出,再由FPGA和RS232协议芯片搭建的串口模块将采集到的数据上传到上位机以供进一步处理。

1.2 装置结构框图

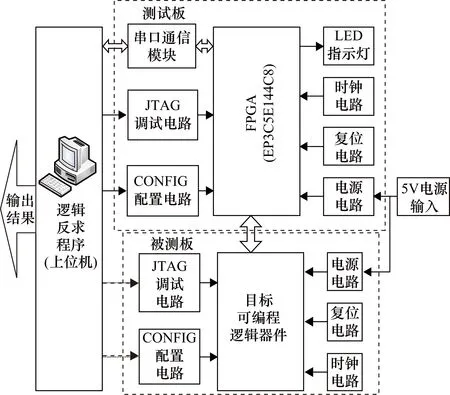

本反求装置包括上位机和下位机两个部分,其中下位机包括测试板和被测板以及连接器,遍历所有的输入情况并将输出结果传输给上位机以提供进一步处理;上位机为逻辑反求程序,具体包括反求算法程序和串口通信程序,装置结构框图如图1所示。

2 模块硬件设计

2.1 测试板设计

测试板采用FPGA作为控制器,型号为Altera公司的EP3C5E144。产生对目标逻辑芯片的输入信号,并且接收目标逻辑芯片的输出信号,同时提供可以上传输出结果的串口通信模块,具体来说分为以下几个部分。

图1 装置结构框图

(1) 电源电路。

在本装置中,EP3C5E144工作需要3.3 V、2.5 V、1.2 V三种电压,所以电源方案为外接输入5V直流电,在此基础上设计电源转换电路。分别为使用LMS1117-3.3、LMS1117-2.5、LMS1117-1.2芯片搭建3.3 V、2.5 V、1.2 V电路。

(2) 复位电路。

复位电路提供EP3C5E144的工作开始触发,采用MAX706SESA芯片外接复位按钮,按下按钮时即产生下降沿复位信号。

(3) 时钟电路。

时钟电路提供EP3C5E144芯片的工作频率基准,采用50 MHz有源晶振。

(4) JTAG电路和CONFIG电路。

其中,JTAG电路实现在线调试功能,CONFIG电路实现下载固化功能。

(5) LED指示灯电路。

因为本装置处理大规模数据,其遍历和传送需要一定时间,因此设置了LED指示灯电路用于显示其工作状态。

(6) 串口通信模块。

串口通信模块用于将遍历输入而得到的输出序列传送到上位机以进行下一步处理。采用RS232串口协议完成与上位机的交互,硬件设计为使用SP3232EEN芯片进行通信信号电平的转换,波特率设置为115200 bit/s。

2.2 被测板设计

被测板包括各种可编程逻辑器件的安装插座(插针),方便其装卸;同时含有相应的电源、时钟、复位、配置芯片、JTAG调试口等电路和资源,使目标器件在上电之后可以正常进入工作状态,同时也可以在被测板上给目标器件编程注入程序。

3 下位机软件设计

3.1 下位机主程序流程

本装置下位机以Verilog 硬件描述语言编写FPGA运行的代码,实现的功能包括遍历所有输入并获取其相应的输出、接收上位机指令以及向上位机传送输出数据等。

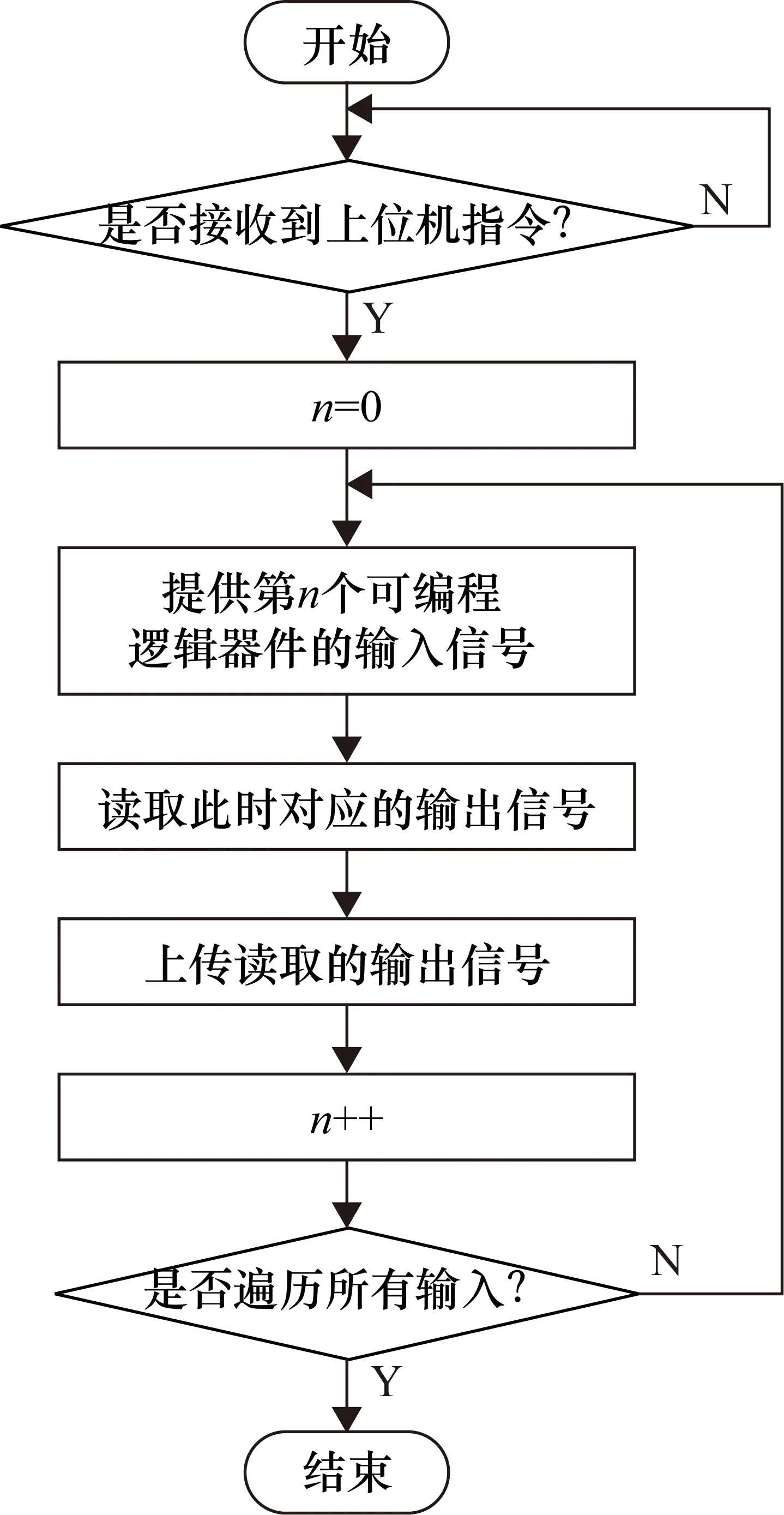

下位机的主流程框图如图2所示。

图2 下位机主软件流程框图

3.2 串口通信模块

下位机编写了串口通信模块用于上下位机的数据交互,具体方法为:用FPGA自带的PLL构建了波特率发生器,在接收时以6倍波特率频率采集RXD信号,一旦检测其有下降沿,则等待3个时钟,以便于在每个波特率中部采集信号,然后每隔6个时钟采集一次RXD信号,采集8次后组成为接收到的一个字节数据;发送时则直接采用波特率频率作为时钟,首先将TXD置为高电平,在接收到发送指令时将TXD置为低电平,然后每到一个时钟发送一位数据,直到将一个字节的8位数据全部发出后,再将TXD拉回高电平。接收和发送一个字节数据的软件流程如图3所示。

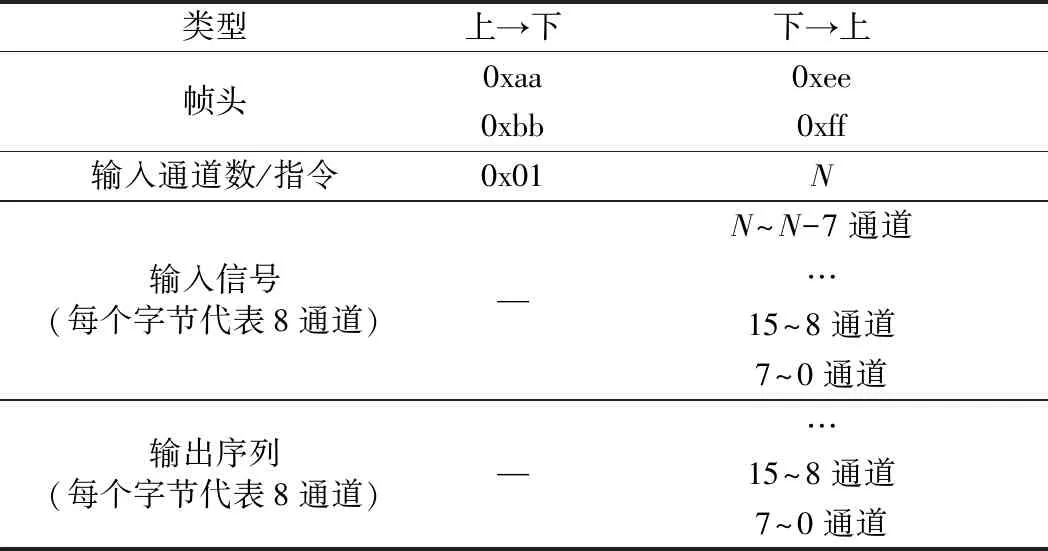

为防止数据误传、提高传输可靠性,设计了数据帧,其格式如表1所示。

4 上位机软件设计

4.1 反求算法

反求算法是本文的核心内容,是本装置的关键部分。算法的主要思想是运用广义上的动态规划方法,将先前得到的输出总序列按照自顶向下的顺序确定顶层逻辑和分离逻辑左右支,然后递归继续求解左右支序列的逻辑关系。具体过程如下:

图3 RS232串口接收和发送软件流程

类型上→下下→上帧头0xaa0xee0xbb0xff输入通道数/指令0x01N输入信号(每个字节代表8通道)—N~N-7通道…15~8通道7~0通道输出序列(每个字节代表8通道)—…15~8通道7~0通道

① 将输入信号和输出信号编号,然后类似于存储器模式将输入信号看作地址总线,将输出信号看作数据总线,按照地址递增顺序读取输出数据。

② 选择待分离输入(组),置于地址大端,通过置换调整输出数据,得到相对应的输出信号序列。

③ 检测输出信号是否满足逻辑对称性,若不满足,则重新执行步骤②;若满足则分离顶层逻辑(∪或∩),并且得出逻辑左右支的输入(组)以及对应的输出信号序列,并将输出信号序列代入步骤②,进行递归操作。

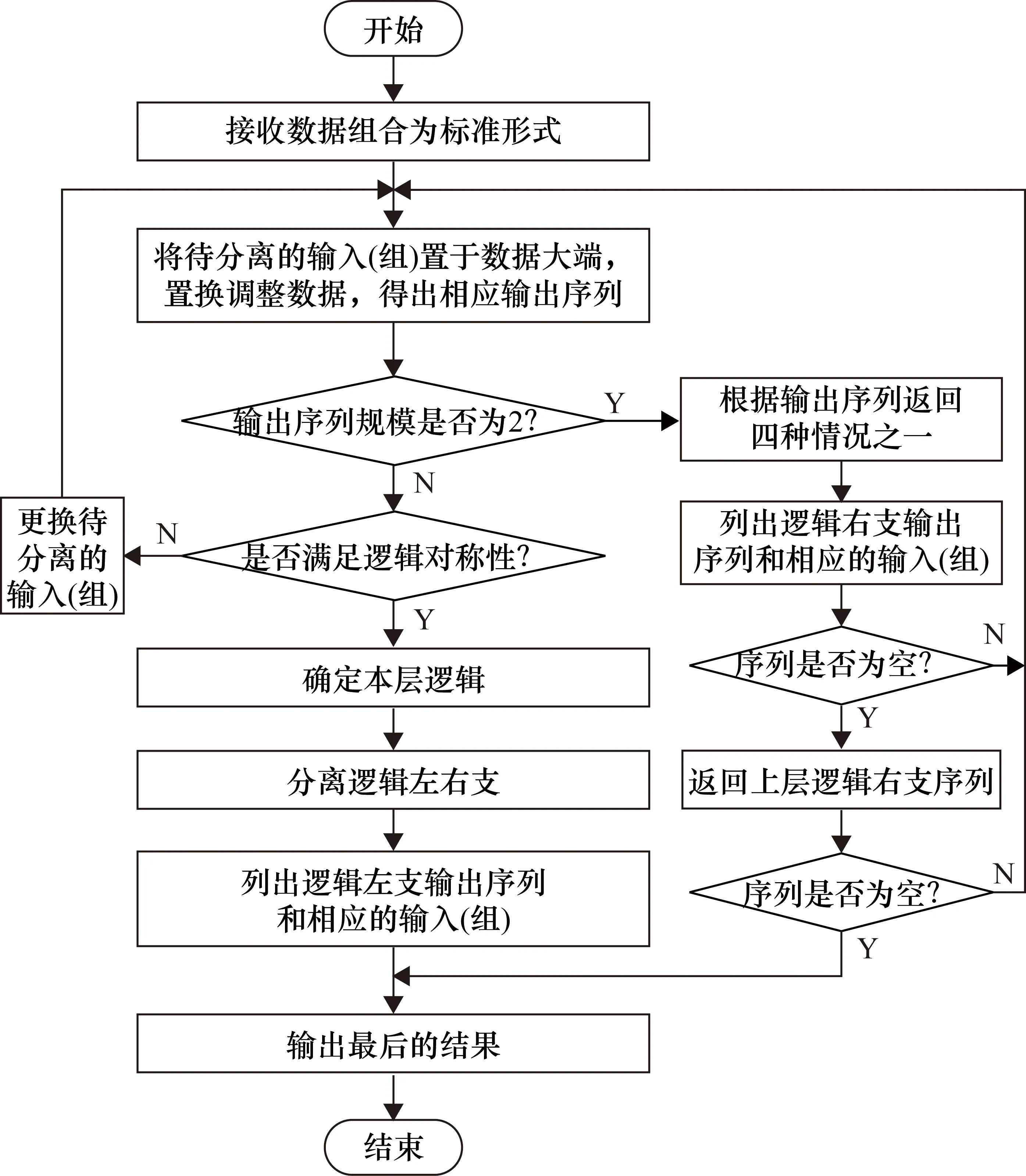

反求算法流程如图4所示。

图4 反求算法流程

以逻辑式:OUT=(A∩B)∪(C∩D)为例对以上算法进行补充说明:

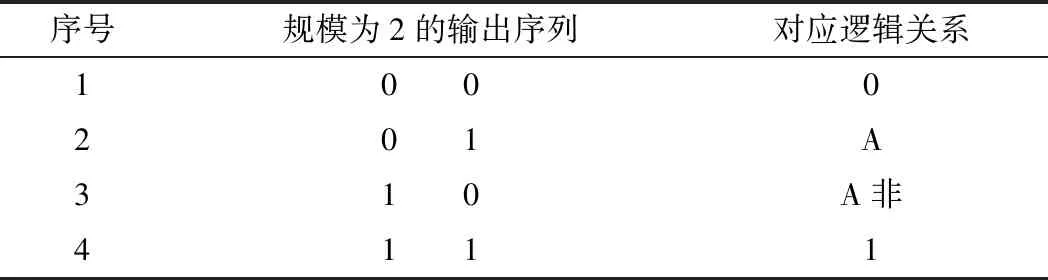

① 在步骤②中,若发现输出序列的规模缩小为2,则根据输出序列的情况返回4种逻辑关系,见表2。

表2 输出序列规模为2时的对应逻辑情况

② 逻辑对称性的说明:对于M路总输入,待分离的N路输入(组)时,将输出序列划分为规模为2N的2M-N个输出组,如果这些输出组只有两种序列,其中有一组为全1或全0,则称为该输出具备逻辑对称性。如表3所示,待分离的输入为A和B两路,总输入为4路,因此输出序列划分为规模为4的4个输出组,这些输出组只有0001和1111两种序列,因此具备逻辑对称性。

③ 顶层逻辑和左右支序列的确定:如果出现全1项的逻辑对称性,则顶层逻辑为“并”;如果出现全0项,则顶层逻辑为“交”。左支序列规模为2N,规则为如果对应的序列有全1项,则全1项对应的输出为1,其他对应的输出为0;如果对应的序列有全0项,则全0项对应的输出为0,其他对应的输出为1。右支序列的确定更为简单,直接选取除全0或全1项之外的那一组输出序列即可。如表3所示,最下方的输出块为全1,则顶层逻辑为“并”(第5列交叉线单元格);另外前三块输出为相同的非全1项,左支序列对应为000(第5列左斜线单元格),加上最后的全1输出,左支序列对应为1,因此左支序列为0001(第6列所示);右支序列直接选择非全1项,即第5列左斜线框中的序列,为0001。

④ 在分离顶层逻辑时,也可以排除无效输入,加快求解速度。

表3 OUT=(A∩B)∪(C∩D)真值表相关

4.2 串口工具

使用开发环境编写串口工具,具备RS232协议通信功能的同时,还可将接收到的数据保存为TXT文件,用来提供给4.1节的算法作为数据源进行逻辑反求。

5 装置操作步骤

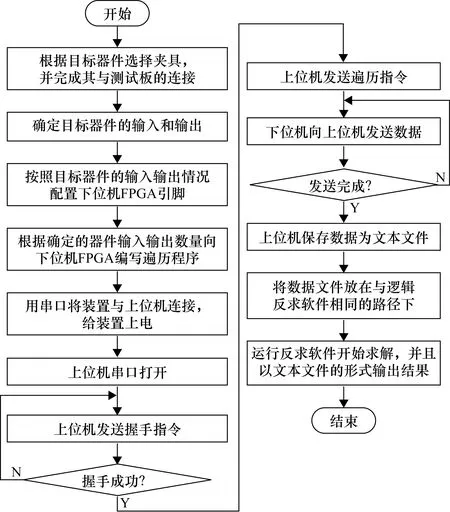

使用所设计的装置对PLD进行逻辑反求主要分为以下步骤,如图5所示。

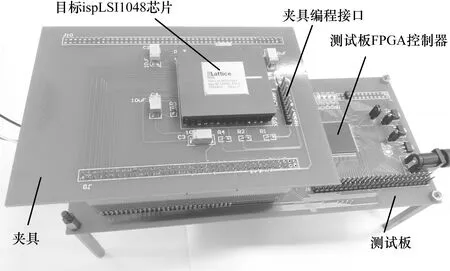

① 根据需要操作的PLD芯片选择相应的夹具,将器件安装在夹具上,并且完成测试板与夹具的安装使其连接起来。图6为测试ispLSI1048(CPLD)时夹具与测试板连接的情况。

② 根据目标器件在电路板中的使用情况,分析确定出该芯片哪些引脚是输入引脚,哪些引脚是输出引脚,另外本文只针对组合逻辑的反求,所以要排除时序逻辑的情况。

③ 根据目标器件的输入输出数量确定数据规模,并编写下位机FPGA的遍历程序,另外根据目标器件的输入输出情况确定下位机FPGA的引脚方向配置。

图5 装置操作步骤流程框图

图6 测试ispLSI1048及其夹具

④ 将装置与上位机的串口相连,装置上电,打开相应的上位机RS232端口。

⑤ 上位机发送握手指令,若收到回复则握手成功,可以进行下一步操作,否则反复握手直至收到回复。

⑥ 上位机发送遍历开始指令,装置开始逐一给出所有的输入组合,并且将得到的输出结果发送到上位机。

⑦ 数据接收完毕后,将数据保存为文本文件的形式,然后将该文件与逻辑反求软件存放在相同路径下。

⑧ 运行反求软件,开始逻辑关系求解,并且以文本文件的形式输出最终结果供用户分析。

6 试验验证和应用

6.1 GAL测试

GAL器件的特点是小巧灵活,引脚数较少,一般实现较简单的组合逻辑功能,可以用人工手段反求其逻辑关系,但是耗时较长。

现针对一款4输入4输出的GAL器件进行逻辑反求,使用所设计的反求装置进行自动求解,仅用时2 s即可完成全部解算工作。将输入代入逻辑式验证结果正确,反求成功。但是在引脚配置、器件安装等环节需要耗去一定时间。因此在小规模的逻辑反求中优势尚不明显。

6.2 CPLD测试

CPLD器件引脚数较多,实现的组合逻辑关系比较复杂,例如本次测试选择的CPLD拥有18输入和16输出,其数据规模达到218×16=4194304个,因此是无法使用人工方法求解其逻辑关系的。

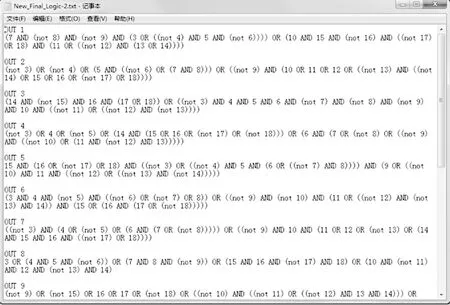

将该器件按照以上方法进行逻辑反求,求解时间大约为180 s,最后得出了其内部的逻辑关系。图7列出了各输出对应的逻辑关系。

图7 求解出的逻辑关系

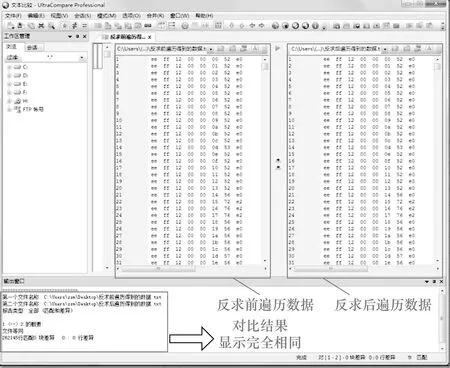

将求解出的逻辑关系使用Verilog语言编写后烧入另一片CPLD中,再将该CPLD遍历得到相应的输出数据,将该数据文件与原器件得到的数据文件进行比较,如图8所示,一共262145行数据无任何差异,完全相同,验证了反求正确率达到100%。

本次测试可以看出,其反求用时较短,结果准确,可靠性和可用性高,相比人工方法具有不可比拟的优势。

6.3 产品维修实例

在进行了两款PLD器件的反求测试后,将本装置应用于实际板件的维修中:某机型飞控产品某部件出现故障,经过故障定位该产品电路板的D1芯片(GAL)存在问题。但是由于普通商用编程器无法读取芯片内的代码,该芯片无法替换,严重影响该产品的修复进程。

该芯片设计为9输入、8输出的组合逻辑功能。使用本反求装置,对无故障产品的正常D1芯片进行遍历反求,在15 s内即求解出该芯片的内部逻辑关系

图8 数据对比验证

式。得出逻辑关系式后通过正向编程的方法对空白的D1芯片烧写操作,再将此芯片替换掉故障芯片,重新对产品上电测试,产品工作正常,故障排除。

7 结束语

针对目前无法使用计算机自动反求机载PLD内部组合逻辑关系这一现状,基于输入遍历运用大数据技术研制了一款机载PLD内部组合逻辑关系反求装置。实验结果表明,该装置操作简单便捷,性能稳定可靠,可以快速反求出机载PLD的内部逻辑关系,从而应用于含PLD的航空电子产品原理分析及产品维修中。