基于时钟树机制的超高速数字锁相放大系统

2019-09-06茆亚洲朱亦鸣

邱 亮 茆亚洲 彭 滟 朱亦鸣

(上海理工大学光电信息与计算机工程学院,上海,200093)

引 言

锁相放大技术是一种基于相干解调原理的微弱信号检测技术[1-4]。通过给待测信号施加一个载波参考信号作调制,使载波参考信号携带待测信号的幅频特征,然后在检测端利用本征参考信号与待测载波信号的强相关性,将携带有待测信号幅频特征的参考载波信号进行相干解调,从而将待测信号从强背景噪声中提取出来。1972年美国斯坦福公司研制出第一台商用级模拟锁相放大器,信号输入带宽可达101 kHz,动态范围120 dB。国内对于锁相放大技术的研究起步比较晚,中大科仪有限公司采用FPGA与ARM平台架构开发的OE2041型数字锁相放大器,信号最高输入带宽30 MHz,动态范围100 dB。近日,瑞士苏黎世公司利用超高速模数转换器(Analog-to-digital converter,ADC)芯片研发的HLMI型锁相放大器将检测带宽提高到600 MHz,动态范围100 dB,成为世界上迄今为止最快的商用数字锁相放大器。在此设计中,最大的优势是采用的单颗ADC芯片可以在保持高分辨率的前提下大幅度提高采样率,从而将锁相放大器信号处理带宽提高到600 MHz。相对传统模拟锁相放大技术,数字锁相放大器性能取决于ADC系统的分辨率、采样率及本征噪声特性[5-7],这就需要基于数字量化保持等特征的数字锁相放大器具有更高的采样率和分辨率。

本文设计了一种基于时钟树机制、并联ADC交替采样结构的超高速数字锁相放大系统。创新性地利用时钟树结构生成多路协调ADC交替采样的时钟信号,时钟树结构包含抖动衰减功能、内部压控振荡源和多个同步管理功能,可以对多路ADC的采样时钟分别进行稳频和严格锁相,减小采样时钟抖动引起的转换误差及畸变,最大限度保留原单片ADC的高精度指标[8]。同时系统利用正交相干解调技术对待测信号和噪声源进行精确测量,提高了系统的噪声抑制能力,从而解决了传统数字系统以牺牲采样精度换取采样速率的弊端,实现了最高采样率400 MHz、动态范围大于100 dB,并且具有从十万倍噪声中提取信号的能力。例如在75 kHz方波调制频率下,可以从5 mV的噪声中提取3 nV的待测信号。

1 多通道并行ADC采样时钟设计

1.1 时钟抖动对采样的影响

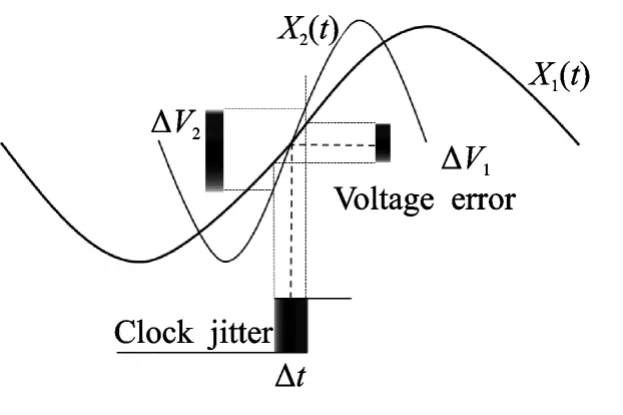

采样时钟信号的质量在时域上采用时钟抖动来描述,在频域上使用相位噪声来表征,两者是对同一事物的不同表述[9]。如图1所示,模拟信号X1(t)和X2(t)的频率不同、幅度相等,在同样的采样时钟抖动Δt作用下,幅度误差ΔV1和ΔV2不相等。由此得出,对于幅度变化率越快频率越高的信号而言,时钟抖动引起的ADC采集误差也越大。

图1 采样时钟抖动导致幅度量化偏差Fig.1 Amplitude quantization deviation by sampling clock jitter

下面定量的分析采样时钟抖动对有效位数的影响。根据文献[10]的理论,信噪比可表示为

式中:fanalog为输入信号的频率,tjitterrms为采样时钟的抖动有效值。

由式(1)可知,系统的信噪比与被测信号的频率和采样时钟抖动的有效值有关。根据文献[11],ADC的信噪比与有效位数关系可用分贝表示为

信噪失真比为

式中:Psignal代表信号功率,Pnoise代表噪声功率,Pdistortion代表谐波失真功率。

ADC的有效位数可定义为

在理想情况下,信噪失真比等于信噪比[11],则有效位数与信噪比的关系为

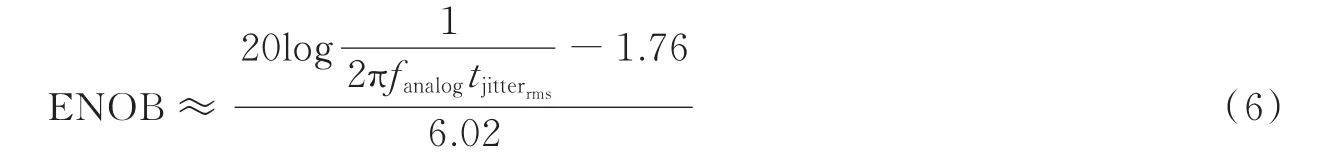

将式(1)代入式(5),可得到有效位数与时钟抖动的关系为

从式(6)可以看出,采样时钟抖动越大,采样系统越难以获得高的有效位数。因此,分析时钟抖动对采样的影响,并以此设计低抖动时钟电路是非常重要的。

1.2 时钟树设计

如上所述,在时间交替并行ADC采样结构中,设计多通道低抖动采样时钟非常必要。通常协调多路ADC工作的时钟信号由时钟分配芯片产生,这种方式在硬件上实现比较容易,但在实际设计电路板过程中,PCB板的布线和电子元器件自身的误差,都会造成输出的时钟信号存在一定的抖动,增加了时钟信号的不确定性。同时这些器件容易受外界因素的影响,比如电压、温度以及特定器件工艺的变化也增加了不确定性。这些不确定性会叠加,从而导致ADC时序出现偏差,这对需要精准时钟信号的时间交替并行ADC结构是难以接受的[12-13]。

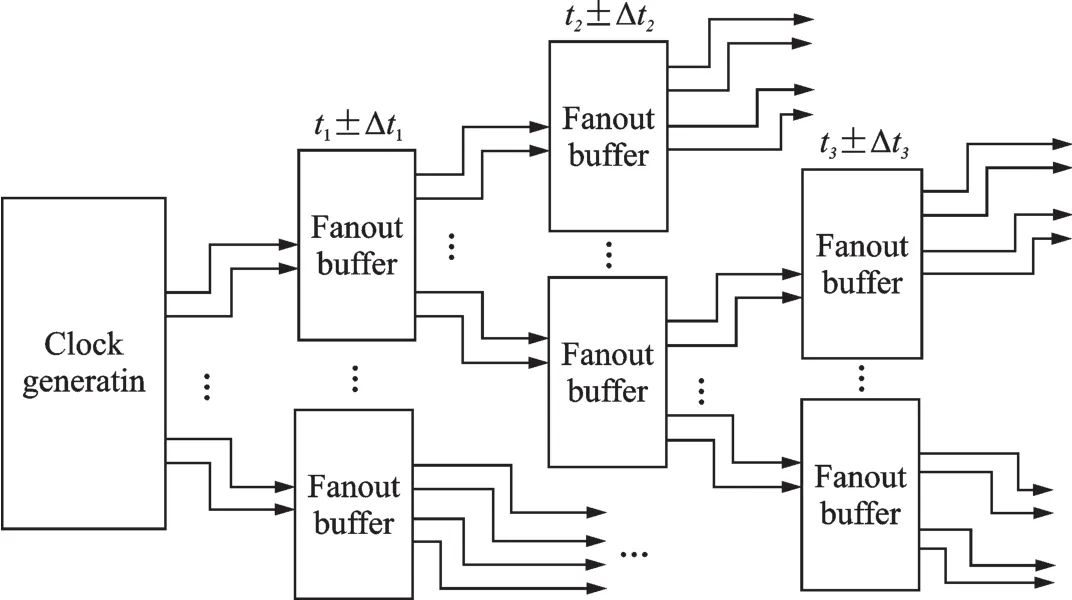

为此本文设计了时钟树结构生成多路时钟信号。时钟树拓扑框图如图2所示,包含一个时钟树树根和多级缓冲器,结构巧妙,可灵活设置时钟信号输出通道个数。图中t1,t2,t3为各级确定性时间误差,该误差可在后期数据处理中进行校正。Δt1,Δt2和Δt3为各级不确定性时间误差,这种不确定性时间误差在上述的时钟分配芯片方案中无法解决。而在本文的时钟树结构中,采用Analog Devices公司的一款高性能双环路整数N分频抖动衰减器HMC7044作为时钟树的根。该芯片的最大优势是可以通过上位机软件发送串行外设接口(Serial peripheral interface,SPI)命令或更精确的同步请求脉冲(SYNC)对输出的时钟信号进行相位对齐,同时发送的指令将使芯片内置的通用参考信号定时器复位,从而控制所有的时钟输出分频器同步对齐。此外,HMC7044还可以通过上位机软件设置生成确定数量的输出脉冲,用作系统内部的参考信号脉冲,最大程度保证多个输出通道高精度同步。因此,在本文时钟树结构中各级输出之间的任何偏斜误差或在后期制板中各输出端线路长度不相等造成的误差都可以在源头进行补偿,从而最大限度降低时钟信号的不确定性误差[14]。

图2 时钟树拓扑框图Fig.2 Topology block diagram of clock tree

2 实验结果

2.1 时钟树结构仿真及实验测试

利用EDA软件ADIsimCLK对HMC7044进行仿真,具体参数设置如下:芯片输入的外参考信号为128.88 MHz,32倍时钟分频,单通道输出的时钟信号频率为100 MHz。仿真结果如图3所示,在并联ADC采样结构中,通常关注10 kHz~20 MHz频带范围内的时钟抖动情况[15],仿真选取10 kHz和100 kHz这两个频率点计算相位噪声,分别为-106.21 dBc/Hz和-111.01 dBc/Hz。

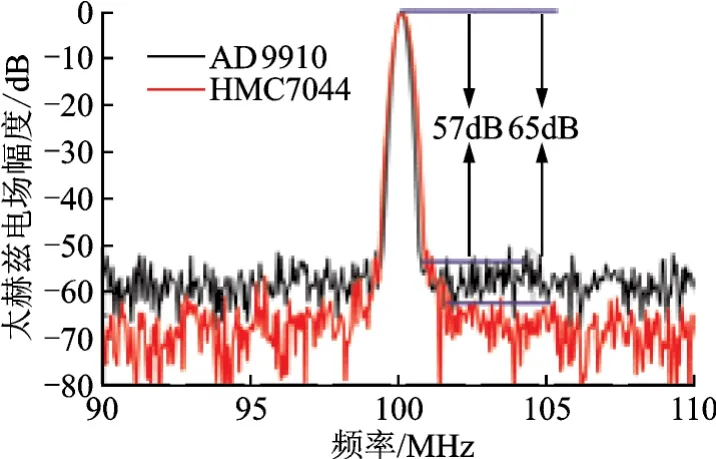

实验中,本文在ADI公司官网申请了HMC7044评估板。采用KEYSIGHT公司的频谱分析仪N9322C对输出的单通道100 MHz时钟信号进行了相位噪声测试,结果如图4所示。根据文献[15]中相位噪声的计算公式,在10 kHz和100 kHz处的相位噪声分别为-97 dBc/Hz和-107 dBc/Hz。由于实际设计中PCB板的布线、焊接及测量误差等因素的影响,HMC7044相位噪声的实际测试数据比图3的仿真结果稍差一点,但基本符合预期结果。接着又与锁相环时钟芯片AD9910进行了对比,对比结果如图4所示。相比于利用锁相环时钟芯片产生信号的方案而言,时钟树结构具有更低的相位噪声,时钟抖动更小。将其应用在时间交替并行ADC采样结构中,能有效保证数据采集系统的有效位数和动态范围[11]。

图3 100 MHz信号相位噪声仿真结果Fig.3 Simulation result of 100 MHz signal phase noise

图4 相位噪声Fig.4 Phase noise

2.2 锁相放大系统设计

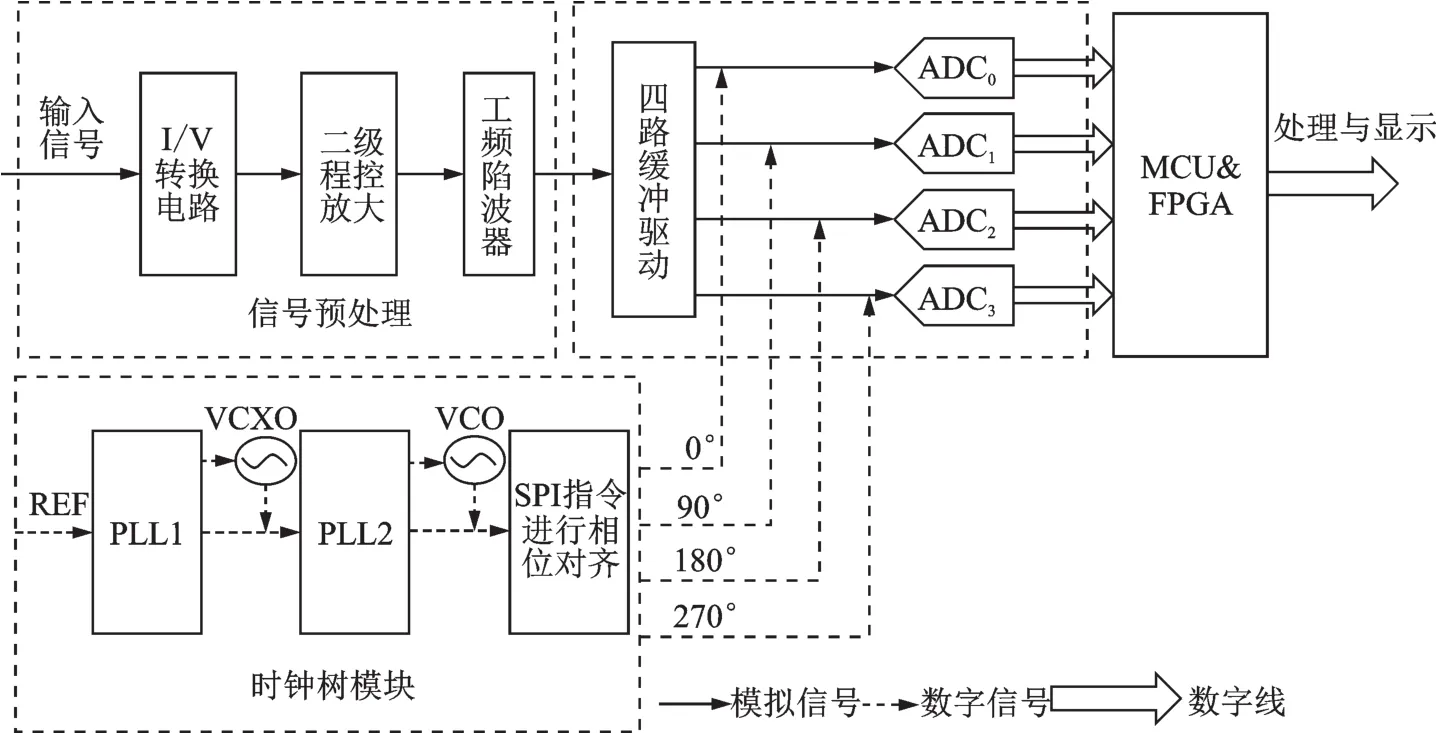

基于上述的测试结果,设计了基于时钟树机制、并联ADC交替采样结构的超高速数字锁相放大系统USST9265。结构框架如图5所示,其硬件部分主要包括高速低噪声I/V转换运算放大器、二级程控放大器、陷波器、四路高速高精度ADC模块、时钟树模块(PLL1作为抖动衰减器,通过极窄的环路带宽,将干净的本地压控晶体振荡器(Voltage controlled xtal oscillator,VCXO)锁定至相对嘈杂的参考环境中,PLL2将低噪声VCXO倍频至压控振荡器(Voltage controlled oscillator,VCO)频率,信号输出通过SPI命令进行相位对齐,最终产生四路严格同步且低抖动的频率为100 MHz的时钟信号分别给四路模数转换器)、高性能FPGA、MCU处理器和USB接口等。

2.3 锁相放大系统性能测试

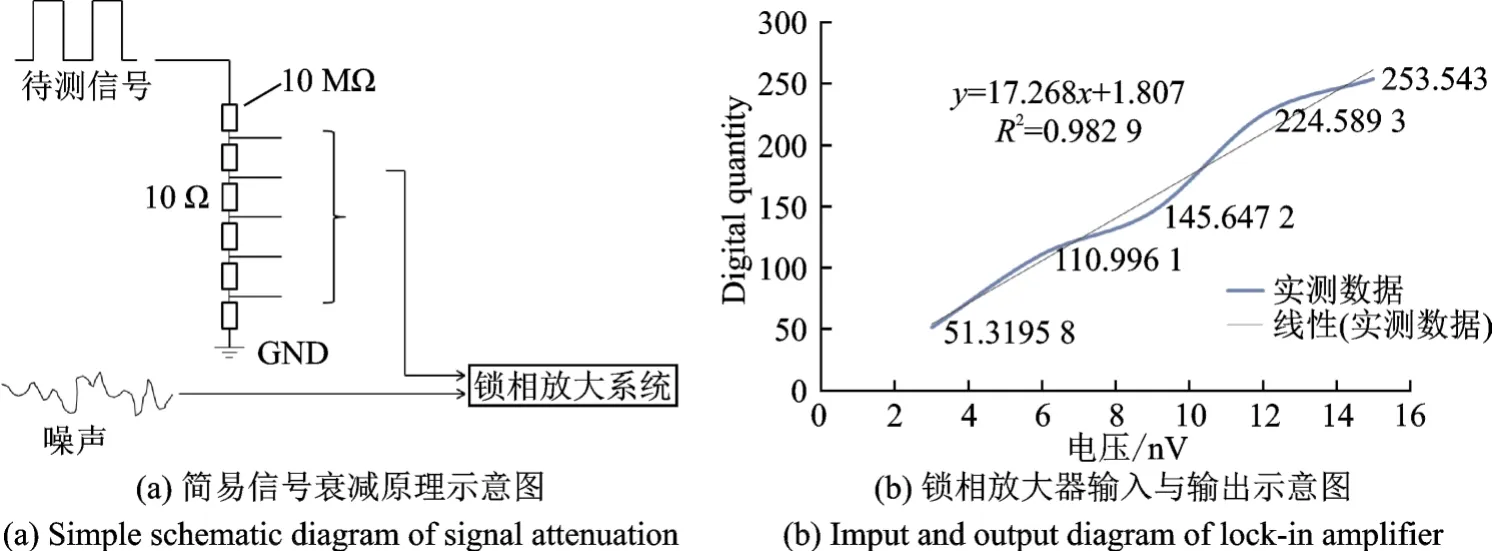

性能测试需要一个信号衰减电路,如图6(a)所示,本文设计了1个10 MΩ大电阻串联5个10 Ω小电阻作为信号衰减。本系统内置的信号发生器输出1个幅度3 mV、频率75 kHz的方波信号,经过电阻衰减后,与5 mV左右的噪声信号进行叠加,再进入锁相放大系统,在±10 mV量程下,测试锁相放大系统能否反映出待测信号的线性变换,即输入放大一倍,输出是否相应放大一倍,测试结果如图6(b)所示。从测试数据可以看出,系统线性度拟合R2为0.982 9,能够准确反应系统对待测信号的线性变换,表明该系统具有从十万倍噪声中提取信号的能力,且动态范围大于100 dB。

图5 锁相放大器Fig.5 Lock-in amplifier

图6 性能测试Fig.6 Performance testing

3 实验结果与分析

3.1 国内外主流锁相放大器实验对比

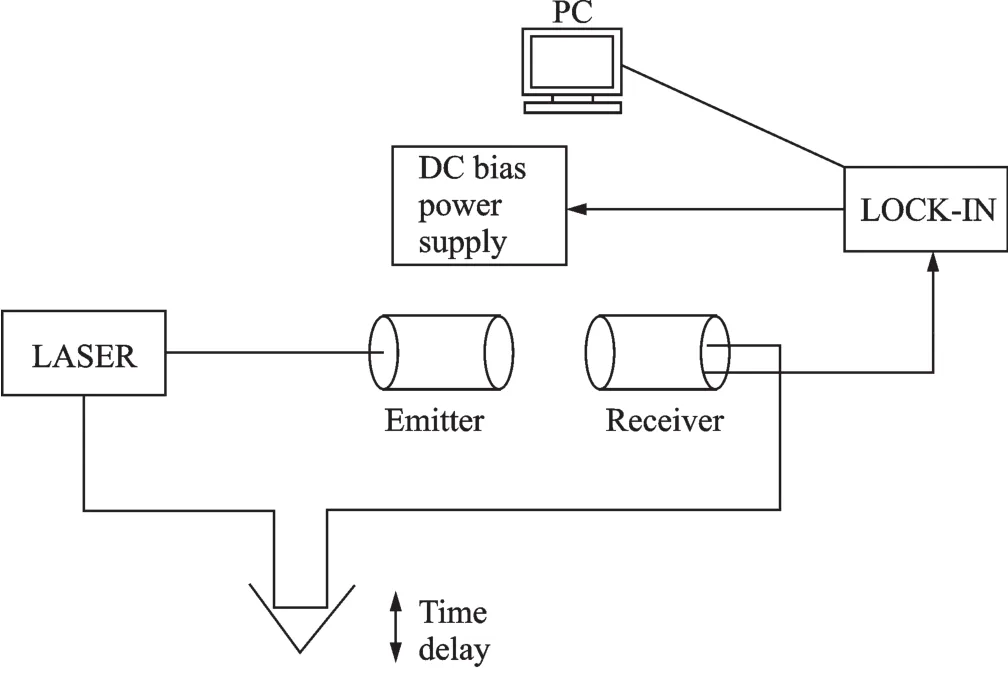

在同等测试条件下,将本文设计的数字锁相放大系统USST9265与美国斯坦福公司锁相放大器SR830分别测试全光纤式太赫兹时域波谱系统。波谱系统拓扑框图如图7所示,其工作过程如下:飞秒激光器输出两束相同的激光脉冲,一束为泵浦光,另一束为探测光,其中泵浦光激励光电导发射天线(Emitter),天线表面受激产生电子-空穴对,在天线两端加载的100 V、75 kHz调制偏置电压作用下,电子-空穴发生定向移动产生瞬间光电流,向空间辐射太赫兹电磁波。另一束与泵浦光同步到达的探测光脉冲照射在光电导接收天线(Receiver)上,天线表面受激产生的光生载流子在太赫兹波偏置电场的作用下发生定向加速移动,在接收天线上产生光生电流,再通过扫描光学延迟线的位置,就可以控制太赫兹脉冲和探测光脉冲之间的时间延迟,从而得到完整的太赫兹时域脉冲。

图7 全光纤式太赫兹时域波谱系统框图Fig.7 Block diagram of all-fiber terahertz time-domain spectroscopy system

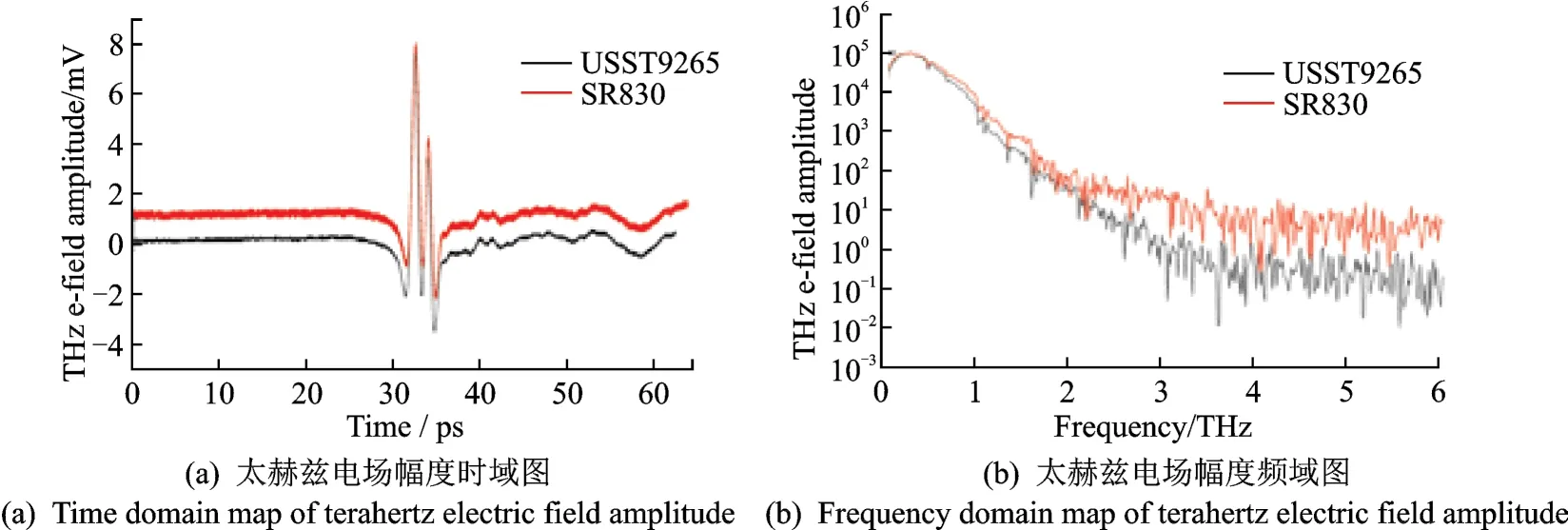

如图7所示,由全光纤太赫兹系统发射器(Emitter)发出的微弱太赫兹时域脉冲信号,经自由空间传输后,被接收器(Receiver)接收,再经锁相放大器检测,最后显示在上位机屏幕上。在测试中,先后更换了USST9265和SR830两台锁相放大器用来对比性能,故对两款锁相放大器设置了相同的参数,即积分时间为1 ms、滤波器阶数为3阶、前置放大106倍等。测试结果如图8所示,其中图8(a)为USST9265和SR830对太赫兹时域脉冲信号的测试结果,为了更直观地对比,将SR830加载直流偏置处理,图8(b)为时域图作傅里叶变换后的结果。

图8 USST9265与SR830实测数据Fig.8 Measured data of USST9265 and SR830

3.2 数据分析

如图8(a)所示,两台锁相放大器都能检测出太赫兹时域脉冲信号的基本波形,即单周期脉冲较强、脉冲前沿平、脉冲后沿有缓慢抖动。但在细节方面,尤其是脉冲前后沿的基底噪声方面,锁相放大器USST9265的检测结果明显比SR830小。从对应的频域图[16]上看,如图8(b)所示,USST9265的频谱宽度为3 THz,优于SR830的2 THz频谱宽度。根据文献[17]中信噪比的估算公式

式中:S(ω)为频谱峰值,σ(ω)为噪声基线水平。可得出,USST9265和SR830的信噪比分别为105和1 778.28。再由公式

可算出USST9265和SR830的信噪比分别为50 dB和32.5 dB。实验结果表明,基于时钟树交替采样并联ADC技术设计的锁相放大系统USST9265具有更好的频谱宽度和更高的信噪比,性能优异,实现了对高速宽带信号的高精度测量。

4 结束语

本文分析了采样时钟的相位噪声对交替式ADC采样结构有效位数的影响,并给出了显性的数学表达式。提出了基于时钟树结构生成分布采样时钟的方法,相比于利用锁相环时钟芯片产生信号的方案,时钟树结构具有更小的时钟抖动。在此基础上,自主设计了一款超高速数字锁相放大系统USST9265,该系统在极大提高采样速度的前提下,最大限度的保证了高分辨率,改进了传统数字系统以牺牲采样精度换取采样速率的弊端。最后将其与国外主流厂商的商用锁相放大器进行了对比,信噪比提高了约17.5 dB。结果表明,基于时钟树机制、并联ADC交替采样结构的超高速数字锁相放大系统,有效解决了模数转换机制中分辨率与采样率不能同时兼顾的矛盾,实现了最高采样率400 MHz、动态范围大于100 dB,并且具有从十万倍噪声中提取信号的能力。这对于设计更高速,更大动态范围的锁相放大器具有非常重要的实际工程意义。