高性能软相关同步技术在数据链抗干扰上的应用*

2019-06-13陈长兴凌云飞王晓东文志军

杨 牧,陈长兴,凌云飞,王晓东,林 兴,文志军

(空军工程大学理学院,西安 710051)

0 引言

在未来高科技条件下的战争中,信息的准确传递是决定战争胜负的关键,无论是弹用数据链还是其他各类空地、星地数据传输链路,都需要在复杂电磁环境下进行数据传输,数据链抗干扰技术能够有效提高电子对抗环境下的信息传输能力,目前受到了各国的高度重视。

数据链抗干扰技术通常采用MIMO系统,以扩频和跳频技术进行[1-3],通过避开干扰频段和时间来提高抗干扰能力,但这种方法缺乏对功率衰减问题的处理,物理层抗干扰能力并未提升;文献[4-6]采用抗干扰天线来提高物理层抗干扰问题,但这种方式需要载体能够布置足够的天线阵元,弹载天线尺寸不一定能够满足要求;文献[7]分析了通过扩频、卷积码等调制与编译码方式提高抗干扰性能,但不论何种方式提高性能,基本的同步性能是决定调制与编译码能够发挥作用的关键指标。本文主要针对物理层同步技术的抗干扰进行研究,主要创新点包括:优化文献[8-9]中采用的软相关方式,由于其采用的软相关方式需要进行信噪比估计,复杂度较高,因此,本文采用了近似简化算法;同时,考虑到数据链在远距离传输下信号能量衰减的不同,增加了基于SNR估计的环路动态调整,从基带层面提升了数据链在长距离传输下的抗干扰能力与动态适应能力;最后,在FPGA平台上实现了以上算法,并测试了同步算法的错误概率。

1 算法理论分析

1.1 优化的软相关算法

软相关算法基本思想是根据接收的比特能量寻找最符合期望比特序列的起点,也可以理解为基于极大似然估计判断的边界。在实际通信中,接收到的比特能量可以用式(1)表达:

其中,rk是接收端的比特信号能量,Ack是发送端的比特信号,nk为噪声能量,对于此信号,根据文献[10-12]中给出的方案,需要对连续信号作软相关来找出最大值,其中软相关计算公式为:

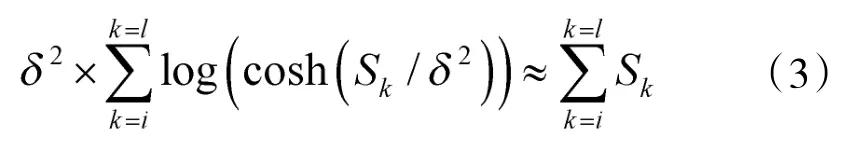

其中,Pi为某点软相关的幅度值,l为同步码的长度,Sk为与起始位置不大于同步码长度的比特位置上的信号能量,Signk是该点的期望符号,而δ2为噪声能量,这种软相关方案下需要对噪声能量有较为准确的判断,然而在实际应用中,估计得到的信道噪声不会非常准确。式(2)中等式右边第2项是为了剔除噪声在本次软相关过程中的影响,由于传输信号中,比特通常采用交织与卷积的方式,因此,可以认为比特能量的期望均值为0,因此,可将其简化为下式:

将其带入软相关计算公式,简化得到如下的计算公式:

更新过的计算公式不需要得到信号能量,因此,更适合工程实现,修改的算法利用信号能量来估算噪声带来的影响,直接对软相关范围内的数据求幅度和,在降低计算复杂度的同时并不会带来大的性能损失。

软相关计算会得到一串不同幅度值的相关结果,要得到正确的同步起点,还需要对软相关结果进行判决,本文采用置信度判决方式,置信度判决公式如下:

其中,R为各比特符号幅度值,Rmax是最大点的幅度值,Rall是同步范围内所有点的同步结果,也含最大点。为适应不同衰落下的信号能量,将成功判决条件分为两种情况,成功判决条件如下:

1)当P大于50%时,直接判决该点为信号同步起点;

2)当P处于30%~50%时,采用Tong判决方式,与首个最大点位置相同判决成功次数加一,反之减一,当判决成功次数大于等于3时判定为起点,小于-3时认为判决点错误,重启判决;

3)当P小于30%时,此次判决认为无效。

这种判决方式能够有效在低信噪比下准确选取合适的同步起点,同时能够适应高信噪比下快速同步的需求。

1.2 SNR判决下的动态调整

对于高信噪比高动态与低信噪比与低动态的场景,采用SNR判决调整环路参数、同时计算同步成功置信度。

图1 动态调整流程图

动态调整算法基于信噪比计算,当跟踪上一定时间的信号后,计算得到粗略信噪比,当信噪比大于门限时,采用高动态环路,同时将计算同步成功置信度;反之采用高灵敏度环路,也同样计算置信度,当置信度满足要求时,接收基带跟踪同步完成。

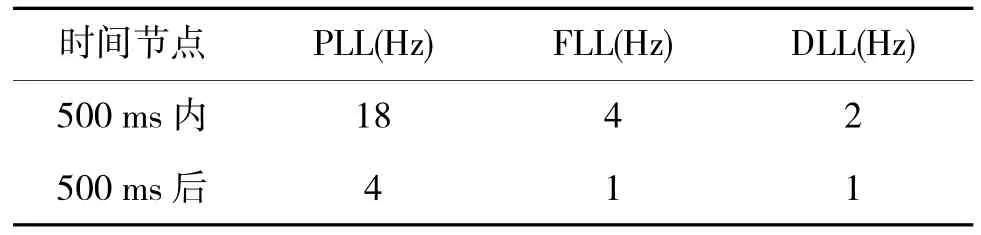

本文采用二阶锁频环辅助三阶锁相环的环路方案。为满足不同场景下的环路需求,环路带宽也应选取合适值,根据实际测试与仿真结果,设定两种环路配置如下:

表1 高动态环路配置

高动态环路适用于高信噪比条件,能够在捕获完成后500 ms内快速实现粗跟,后续降低环路带宽实现精细跟踪。

表2 高灵敏度环路配置

高灵敏度环路配置降低了整体环路带宽,确保在环路中滤出更多的噪声,以提升跟踪性能。

2 仿真分析

仿真主要分析优化后的软相关算法的误同步率性能与动态切换效果。

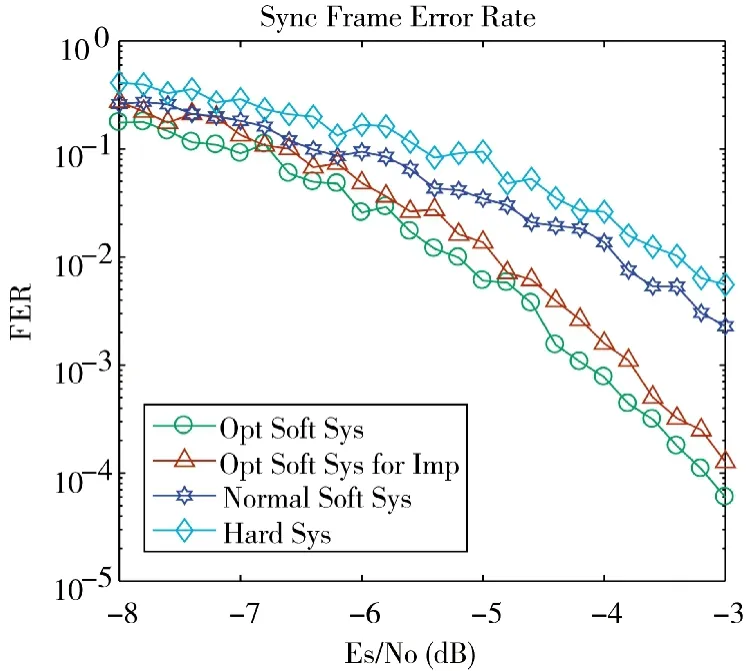

2.1 软相关性能仿真

性能仿真中采用了常用的硬相关方式(即直接找同步头的方式)、普通软相关、文献中优化的软相关方案及本文采用的简化了复杂度的软相关方式。考虑到工程应用中跟踪环路必然存在相位与码环误差,本文仿真中均采用跟踪环路输出值作为同步判决数据输入,避免了其他文献中采用无误差码环导致的与实际效果不符。

图2 软相关算法性能仿真

图2中,Hard Sys与Normal Soft Sys分别为硬判决同步与普通软判决同步,而Opt Soft Sys为文献中给出的优化软判决方式,Opt Soft Sys For Imp是简化了计算复杂度后可用于实际工程应用的软相关同步判决性能,可以看出,尽管简化复杂度后的软相关同步判决算法性能比文献中的优化算法性能略有下降,但损失不到0.5 dB,仍然比普通软相关算法的性能有1 dB的提升。同时,本文算法仅比普通软相关算法的计算复杂度增加了N个加法器(N为同步头比特数),而文献中的优化软相关方式由于需要噪声能量,因此,在实际使用中是无法实现的。

本文算法的应用场景不仅需考虑低信噪比下正确同步的性能需求,也需要在高信噪比场景中能够实现快速同步,根据上文所述,同步判决采用置信度实现。

图3 不同信噪比下软相关同步结果

图3中可以看出,高信噪比每次相关的结果置信度都很高,根据上文中置信度计算方式,图3中高信噪比软同步在第37个点,首次出现大的相关峰值时成功同步;低信噪比在第94点上成功同步,算法实现了不同场景对同步的要求。

2.2 同步策略动态调整

环路同步策略主要针对高信噪比下的动态性能,因此,仿真主要针对高动态下的跟踪能力,仿真测试高动态下的环路锁定情况,其中环路锁定判决计算方式如下:

I/Q分别为同向分量信号能量与正交分量信号能量,由于采用调制方式为BPSK,因此,Q路信号能量在稳定跟踪时接近于0。P值越接近1,跟踪稳定度越好。

表3 高动态测试结果

表3显示,在最高30 g的情况下,依然能够稳定跟踪,同步策略在高动态场景下能够正常工作。

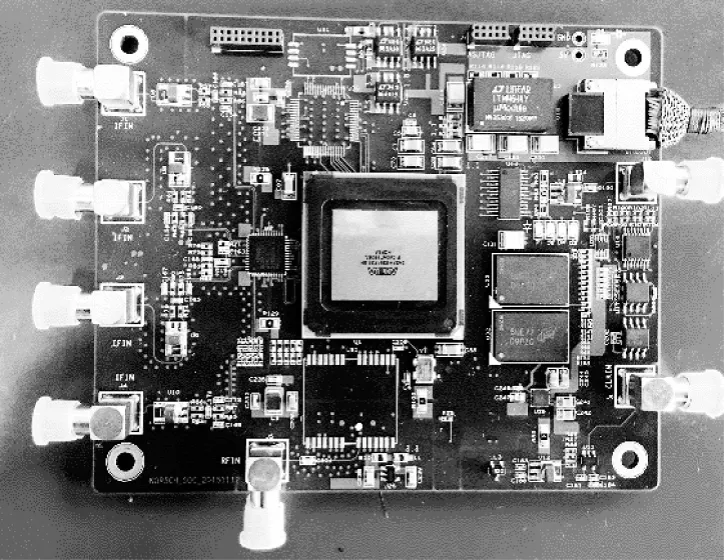

3 硬件实现

高性能软相关技术是数据链基带处理的一部分,本文采用altera arriaV SOC芯片进行硬件实现,其中软相关采用SOC芯片中ARM部分进行处理,将连续数据比特通过HPS传至ARM端进行浮点数据处理,这种方式能够充分发挥SOC芯片优势。

图4 数据链接收机样机

软相关主要在ARM端进行处理,处理流程如下:

1)接收FPGA端传输的1比特积分值,并将传输的首个积分值设为计数起点;

2)以N个计数值为周期,即同步码为周期,进行软相关;

3)统计各点相关值,计算置信度;

4)根据判决条件实现快速同步/高灵敏度同步。

以上便是数据链软相关下的优化同步方案,值得注意的是,在数据由FPGA端传到ARM端时,必须严格确保数据传输不出现丢失的情况,否则会导致ARM端比特错位,进而导致整个传输失败。

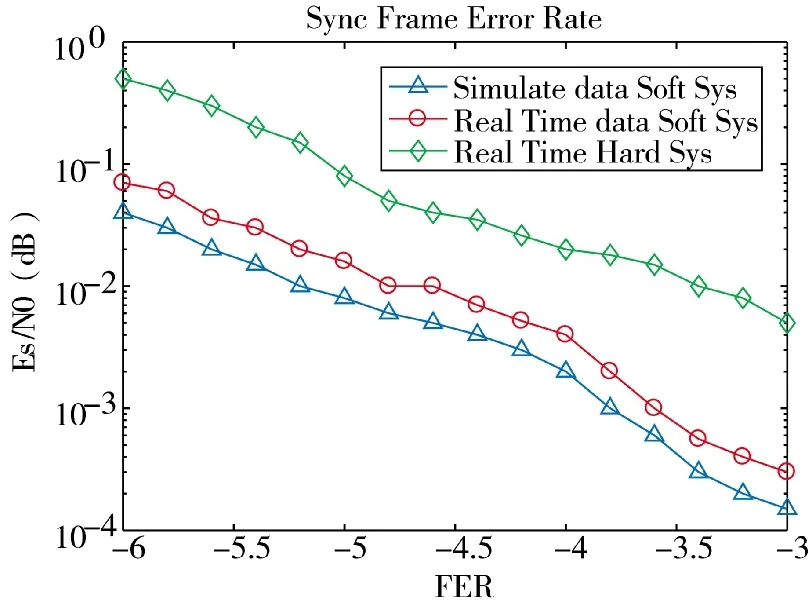

实际测试结果与仿真结果对比如图5所示。

图5 实测相关结果与仿真结果对比

图5中,Simulate data为仿真数据,Real Time data为实际在FPGA板上传输测试数据,可以看出,两者误差不到0.5 dB,误差主要是数据量化带来的误差,仿真结果表明,优化后的软相关结果比之前采用的硬判决方案能有2 dB左右的性能提升。

4 结论

本文从数据链传输物理层考虑提高抗干扰能力,在软相关同步上实现了一种更为实用的算法,在降低计算复杂度的同时仅损失了0.5 dB的同步性能,同时利用优化的同步判决在信道变化的情况下实现了通用化的同步方案。

在完成软件仿真后,采用SOC芯片实现了本文算法,在实际通信过程中本算法工作正常,性能较之前采用的硬判决方案有约2 dB的提升。