电阻负载型NMOS反相器输出低电平优化

2019-05-08刘春艳

刘春艳,李 媛

(渤海大学新能源学院,锦州121013)

1 引言

反相器是电子线路中的常用器件。随着微电子技术和工艺的不断发展和创新,电子产品的应用越来越广泛,但也面临着更加复杂的电磁环境。反相器是几乎所有数字集成电路设计的核心[1-3],现今反相器应用主要以CMOS反相器为主,但部分电路也会有其他反相器的应用,例如分立元件电路中就常用电阻负载型NMOS反相器,对于反相器在这些方面的应用,人们也做了大量研究[4-6]。但是对于电阻负载型NMOS反相器的参数对NMOS反相器的性能的影响,相关的研究还很少见,基于此,对影响反相器输出低电平的各个因素进行分析,针对电阻负载型NMOS反相器的衬底掺杂浓度、P+区掺杂浓度、栅氧化层的厚度、导电沟道的宽长比等影响反相器输出低电平的各个因素展开研究。

2 NMOS反相器器件结构选择

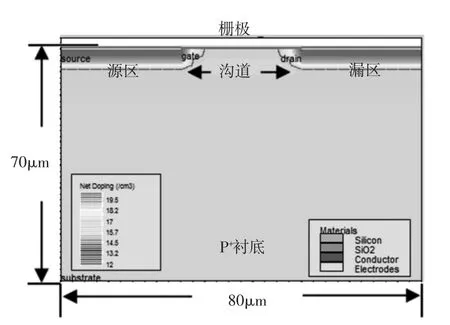

利用Silvaco TCAD[7]建立一种电阻型负载反相器MOSFET结构,如图1。此NMOS器件采用常规平面型水平沟道MOS结构,基本参数设定为:P型单晶硅片衬底,电阻率ρ为 4Ω·cm;为降低表面少子复合损耗,少子寿命设为10μs;硅衬底掺杂浓度为1×1016cm-3;衬底厚度为 70μm;NMOS器件宽度为80μm;栅极宽度、源极宽度、漏极宽度皆为1μm;用于调整NMOS阈值电压的表面P+区掺杂浓度为1×1017cm-3;为了降低源、漏极接触电阻,提供足够多的多子电子,NMOS器件源、漏区掺杂浓度应较高,设为1×1020cm-3;为了增大NMOS器件跨导和截止频率,在满足工艺加工水平要求的前提下,NMOS器件导电沟道长度应尽量取短,选择为0.6μm;为了增大NMOS器件的电流能力,须增大NMOS器件的沟道宽长比,故设沟道宽度较大,为15μm。此外,对于半导体器件,其载流子复合损耗和迁移率大小是影响器件载流子输运和电学性能的两个重要参数,对于NMOS器件,其导电依靠的是迁移率较高的多子电子,为了降低多子电子在水平沟道中的复合概率,应降低沟道表面态密度,适当降低沟道区掺杂浓度,以降低多子电子在沟道输运过程中的复合损耗,改善NMOS器件的跨导和频率响应。

图1NMOSFET器件结构仿真图

半导体器件内部载流子复合概率受半导体掺杂区域掺杂浓度、外界环境温度、结温、界面态密度、界面电荷、材料内部缺陷、复合中心密度等因素的影响,故此在仿真过程中,载流子复合损耗模型选择与硅材料内部掺杂浓度、晶格温度、复合中心密度、陷阱密度相关的复合模型:SONSRH、SRH、AUGER。

半导体器件内部载流子多子电子迁移率受到半导体器件内部掺杂浓度、晶格振动、载流子散射、水平电场、纵向电场等因素的影响,在仿真过程中,NMOS器件内载流子迁移率模型选择与晶格温度、硅材料内掺杂浓度、横向及纵向电场相关的迁移率模型:CVT。

在仿真过程中,源漏区重掺杂也会对NMOS器件的电学性能产生一定影响,因此也考虑了硅材料重掺效应所引起的禁带变窄和能带简并效应。

3 器件仿真及结果分析

电阻型负载反相器电路结构如图2。线性电阻为负载的NMOS反相器,输入信号Vi从栅极输入,即 Vi=VG;输出电压 VO从漏极取出,即 VO=VG。

图2 电阻负载型NMOS反相器电路图

将输入管Ti等效为可变电阻RMOS,由此,VO可由RL和RMOS的分压比表示[8],即:

当 Vi=VDD且 VDD>≫>Vi,有:Ti导通,RMOS<≪<RL,VO=0V;当 Vi=0V,则有 Ti截止,RMOS>≫>RL,VO=VDD。由此可知输入和输出呈反相关系。

电压传输特性用输出电平VO与输入电平Vi之间的关系来表示,反映了输出电平随输入电平的变化规律。从NMOS反相器的电压传输特性曲线可以评价该器件的电学性能优劣。从电压传输特性曲线上可直接读出输出高低电平、逻辑阈值转换电平、输出开门/关门电平等。通过对比不同反相器电压传输特性,也可对由反相器制造工艺缺陷(如不同工艺导致的NMOS反相器阈值电压变化、不同衬底质量或不同的掺杂浓度导致的反相器导电因子变化等)和由反相器结构设计缺陷(如NMOS反相器沟道宽长比、栅极面积等的设计缺陷)所导致的NMOS反相器电性能异常进行排查、分析和改善。电阻负载NMOS反相器的静态特性可直接由节点电流方程和伏安特性推导得出;在NMOS器件(作为输入管)的特性及电源电压均为已知的情况下,NMOS电阻负载反相器两端负载电压与负载电阻、流经的负载电流之间有如下关系[8]:

负载线方程[8]则为:

由式(2)、(3)可见,对于NMOS电阻负载反相器的电压传输特性,反相器输出电压VO与负载电阻大小(负载电阻通常为集成的薄膜多晶硅电阻或集成的由扩散制备得到的区域电阻)有关,负载电阻越大,NMOS反相器输出低电平越低,反相器逻辑摆幅越大。NMOS反相器过渡区也受到负载电阻的影响,负载电阻越大,反相器过渡区越窄,反相器直流通态损耗越低,反相器电性能越好。

电阻型负载NMOS反相器的输出低电平可表示为[8]:

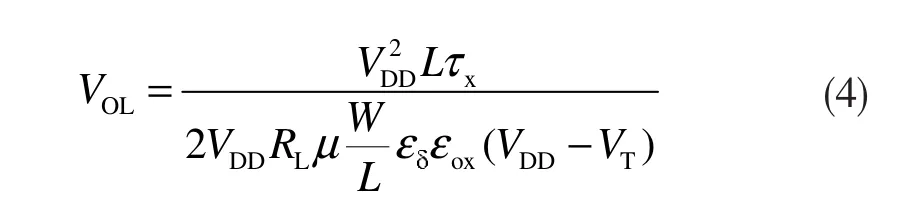

为衬底掺杂浓度对反相器输出低电平特性的影响如图3所示。由图中曲线可见,对于具有不同衬底掺杂浓度的电阻型负载NMOS反相器,输出低电平差异明显。增加衬底的掺杂浓度,反相器输出低电平随之增大。产生该现象的原因可由公式(4)解释,当电阻型负载反相器的衬底掺杂浓度增加,μ随衬底掺杂浓度增加而减小,电阻RL的阻值不变,电阻型负载反相器的输出高电平不变,导电沟道宽长比不变,输出低电平增大。当衬底掺杂浓度调整为3×1017cm-3,P+区掺杂浓度保持 1×1017cm-3不变时,所得的阈值电压最符合电阻负载型NMOS反相器的电平转换需求。

图3 不同掺杂浓度下输出电平曲线

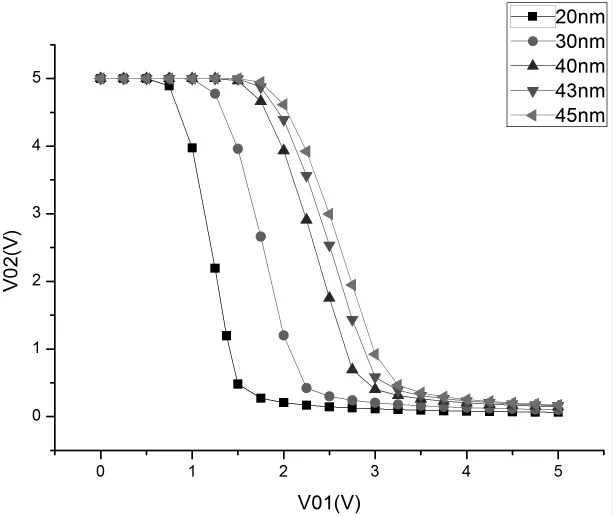

不同栅氧化层厚度对反相器输出低电平特性的影响如图4所示。由图中曲线可见,对于具有不同栅氧化层的厚度的电阻型负载反相器,输出低电平差异明显。增大栅氧化层的厚度,反相器的输出低电平随之增大。产生该现象的原因同样可由公式(4)来解释:当电阻型负载反相器的栅氧化层厚度增加,ττxx增大,电阻RL的阻值不变,电阻型负载反相器的输出高电平不变,导电沟道宽长比不变,输出低电平增大。当栅氧化层的厚度为43nm时,阈值电压得到理想的取值,所得的VO2随VO1变化输出曲线效果最佳,即达到了优化电阻型NMOS反相器输出低电平的目的。

图4 不同栅氧化层厚度下输出电平曲线

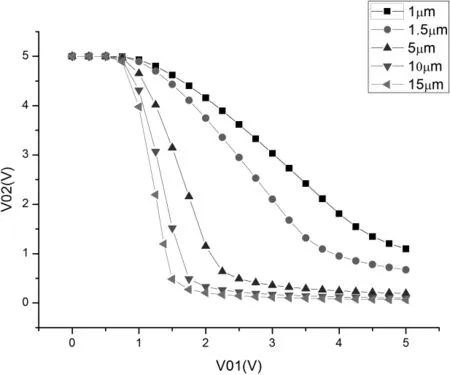

不同导电沟道宽度对反相器输出低电平的影响如图5所示。由图中曲线可见,对于具有不同晶体管导电沟道的宽长比的电阻型负载反相器,输出低电平也明显不同。当导电沟道宽度为1.5μm时,VO1继续增大,直到5V时,输出电平VO2始终没有趋近于0V,产生该现象的原因仍可由公式(4)解释:当电阻型负载反相器的晶体管导电沟道的宽长比增大,电阻RL的阻值不变,电阻型负载反相器的输出高电平不变,输出低电平减小。由于减小导电沟道的宽度,即降低导电沟道的宽长比,会使导通电流变小,相当于增大了NMOS晶体管的导通电阻和所分得的电压,所以改变导电沟道宽长比的方法不利于实现对电阻负载型NMOS反相器的输出低电平的优化。

图5 不同导电沟道宽度下输出电平曲线

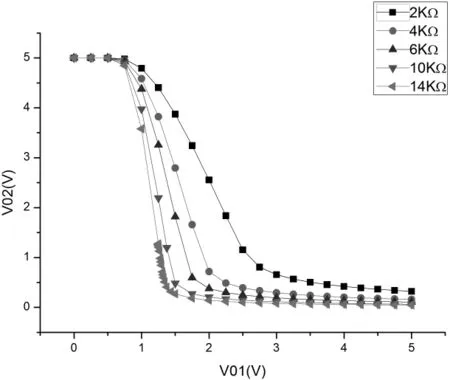

最后,图6为不同电阻值RL对反相器输出低电平特性的影响。由图6可见,对于具有不同电阻RL的阻值的电阻型负载反相器,输出低电平不同。当电阻RL的值减小时,不利于电阻负载型NMOS反相器输出低电平的优化,产生该现象的原因可由公式(4)解释:当电阻型负载反相器的电阻RL的阻值增大,电阻型负载反相器的输出高电平、μ、导电沟道宽长比皆不变,而输出低电平减小。电阻RL阻值越大对输出低电平的优化越有利。

图6 不同电阻值RL下输出电平曲线

4 结束语

利用Silvaco TCAD对电阻负载型CMOS反相器进行仿真研究,依据仿真得到的不同P+区掺杂浓度、不同栅氧化层厚度、不同导电沟道宽度及不同电阻值RL下的输出特性曲线,全面系统分析了性能参数对电阻负载型CMOS反相器的影响。结果表明:增加衬底和P+区掺杂浓度可以改变阀值电压,从而实现对电路的输出电平的优化;增大栅氧化层的厚度也是优化电阻型NMOS反相器输出电平的可行方法。