晶圆厂转移过程中CMOS工艺可靠性研究

2019-05-08刘旸

刘 旸

(中国电子科技集团公司第四十七研究所,沈阳110032)

1 引言

CMOS工艺是在PMOS工艺和NMOS工艺的基础上发展起来的,是目前集成电路产品设计最常选用的工艺。CMOS电路在加工上是将NMOS器件和CMOS器件同时制作在同一衬底上,具有功耗低、速度快、抗干扰能力强、集成度高等优点[1]。由于降低制造成本、产能增加和供应商多样性要求等因素,在CMOS的生产过程中,晶圆厂转移是半导体行业的常见现象[2]。不同晶圆厂的工艺参数存在差异,在进行晶圆厂转移时,需先评估晶圆厂间的工艺流程、工艺参数、原材料等的差异,才能做到在不影响用户使用的前提下进行晶圆厂转移[3]。

2 工艺线差异对比

某型待转移产品原采用4英寸3μm双层金属P阱硅栅CMOS工艺进行加工,工艺流程如下:

备片→一氧→形成N阱→形成P阱→阱推进→预氧化→Si3N4淀积→形成有源区→场区注入→场氧化→去除Si3N4→一栅氧化→沟道调整注入→栅氧化→Poly淀积→Poly掺磷→形成多晶硅栅→PSD注入→NSD注入→ILD→形成孔→金属淀积→金属布线→钝化淀积→形成PAD窗口→合金

晶圆厂转移后,拟采用5英寸2μm双层金属P阱硅栅CMOS工艺生产线进行产品加工。综合对比两条生产线的加工工艺,涉及工艺变更的内容主要包括以下几个方面:

1)衬底片电阻率由 4~6Ω·cm改为2.5~3.5 Ω·cm;

2)P管场区阈值调整方式由注入后阱推进改为场区形成后进行表层注入;

3)P管沟道调整注入由栅氧化前调整为栅氧化后;

4)NSD注入调整至PSD注入之前;

5)栅氧厚度由50nm改为40nm;

6)ILD由TEOS 900nm改为TEOS 200nm+BP TEOS 600nm;

7)金属布线层厚度由1.2μm改为1.1μm。

3 差异评估

3.1 衬底电阻率

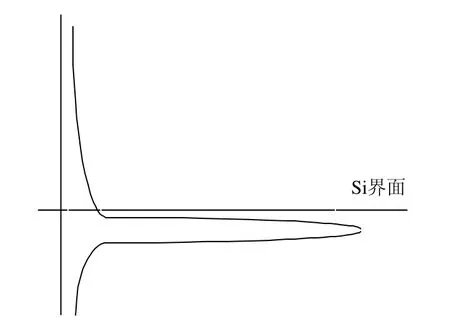

待转移产品设计电路中包括NMOS晶体管和PMOS晶体管,纵向结构如图1所示。

图1 N、P管纵剖结构图

其中,NMOS晶体管在衬底上通过注入、退火形成P阱,实际晶体管结构在P阱内加工。P阱电阻形成过程中,已改变原沟道区电阻率,通过监控P阱电阻,可确定工艺变更是否对器件造成影响。

原工艺中,第26工步为PMOS晶体管沟道调整注入,通过注入来调整P管沟道区电阻率。阈值电压与栅氧厚度、栅氧质量和沟道掺杂浓度有如下关系式:

其中,εs为半导体介电常数,e为电子电荷,Vt为热电压,ni为本征载流子浓度,均为固定值;εox为氧化层介电常数,QQ'SS′SS为单位面积氧化层等价陷阱电荷,随栅氧化层的厚度和质量变化;Φφmmss为金属半导体功函数,随沟道掺杂浓度变化。

由式(1)可知,栅氧厚度、栅氧质量和沟道掺杂浓度为影响阈值电压的主要工艺参数。亦可利用阈值电压来监控相关电参数。

经PCM测试,工艺变更后P阱电阻值、PMOS晶体管阈值电压及NMOS晶体管阈值电压均在原PCM设计值允许范围内,衬底片电阻率变更对产品电参数影响不大。

3.2 P管场区阈值调整

“场区”为两个独立晶体管间的区域,作用是防止不等电位晶体管间因漏电导致电路失效。其工作原理与常规MOS晶体管相同,仅表层向下1μm以内区域参与工作。即“场区”表层向下1μm以内区域的掺杂浓度满足工艺设计要求,满足电路工作需要。

PMOS管的场区注入用于提高寄生场管的开启电压,使其不会在电路正常工作时误开启。移线产品的工作电压为5V,根据该产品的工作特点,寄生场管开启电压在7.5V以上,满足产品需求,不会对产品造成影响。可通过监控场区阈值电压确认工艺更改是否对产品造成影响。经样管测试,产品场区开启电压为13V,满足产品设计要求,对产品无影响。

3.3 P管沟道调整注入

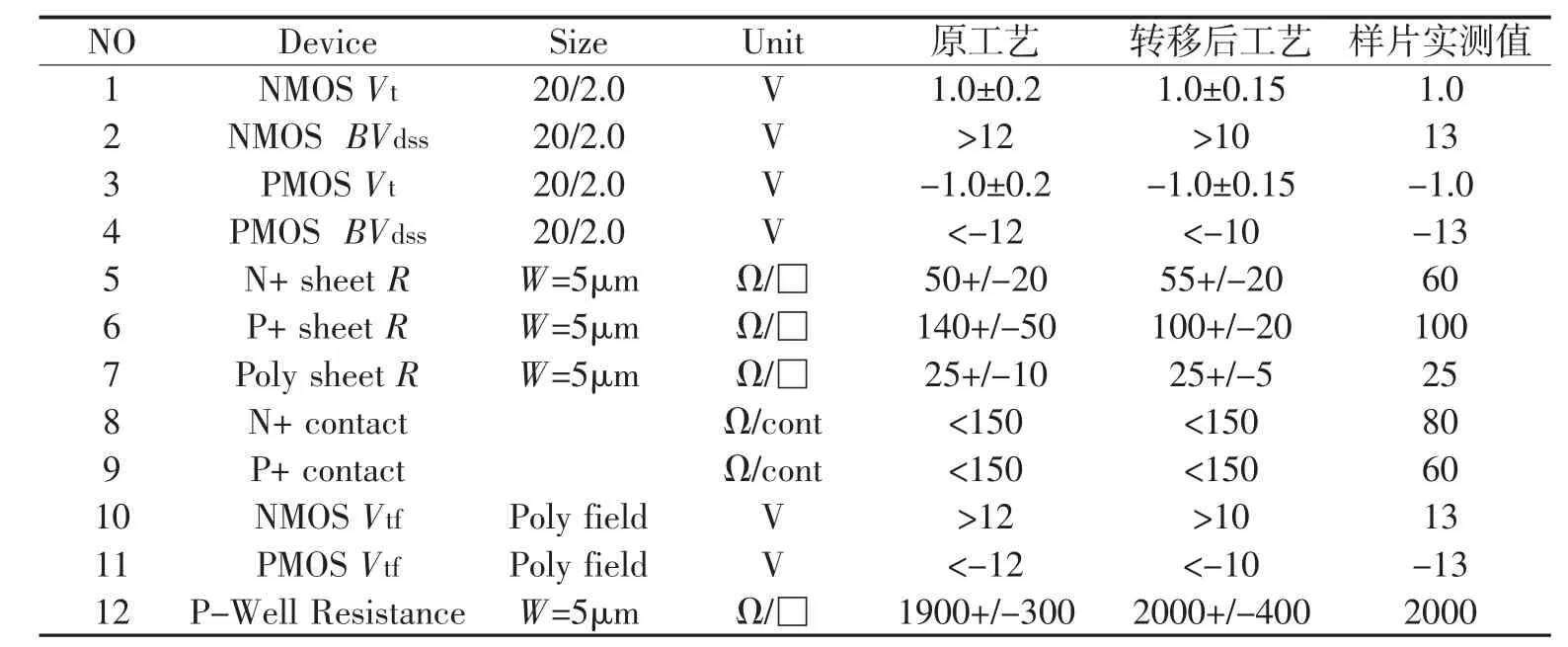

原工艺中P管沟道调整注入是在一栅氧化后进行。沟道注入是隔着50nm的一栅氧化层进行的。在移线后的工艺中,此步注入调整至栅氧化后,注入是隔着40nm栅氧化层进行的。注入工艺有两个工艺参数,即能量和剂量。原工艺离子注入能量为35keV,决定离子注入的深度;离子注入剂量为1.8×1012cm-2,决定掺杂区域的离子数量。根据注入原理,离子注入深度遵循如图2所示的高斯分布示意图。

图2 高斯分布示意图

P沟调整注入的离子浓度峰值应接近Si-SiO2表面,该峰值位置可通过调整注入能量来改变。即工艺变更后,可通过调整注入能量使离子浓度峰值达到工艺设计要求。P沟调整注入可通过P管阈值进行监控,经对样管的测试,产品P管阈值电压为1.0V,满足产品设计要求,对产品影响较小。

3.4 NSD注入

NSD和PSD注入工步分别通过光刻打开N+区域或P+区域的窗口,进行离子注入。未打开窗口的区域由光刻胶覆盖保护,离子无法透过光刻胶注入到硅片中,该工艺调整对产品性能无影响。

3.5 栅氧厚度

由式(1)可知,栅氧厚度、栅氧质量和沟道掺杂浓度为影响阈值电压的主要工艺参数[4]。此三项工艺参数相辅相成,共同决定产品阈值电压。CMOS集成电路中,对栅氧质量的要求为栅源击穿电压达到1nm/V以上[5]。经实际测试对比,移线后加工的样片NMOS及PMOS晶体管的栅源击穿电压均在1nm/V以上,与原工艺参数差异不大,满足工艺要求。

3μm P阱硅栅CMOS工艺采用50nm热氧化SiO2作为栅氧化层,2μm P阱硅栅CMOS工艺采用40nm热氧化SiO2作为栅氧化层,栅氧化层厚度有所改变。在栅氧质量相近的情况下,可调整沟道掺杂浓度使产品阈值电压达到产品设计要求值。通过对样片的测试,产品阈值电压为1.0V,在产品PCM参数范围内,栅氧层厚度改变对产品质量影响较小。

3.6 ILD工艺

ILD为金属布线与电路间的隔离保护层,金属布线平铺在ILD层之上。ILD层下方还有多晶硅栅和场氧两层介质层,形成高低不平的台阶。金属布线采用溅射方式淀积在ILD层上,用于各晶体管之间的连接。溅射过程中,金属原子为垂直下落,台阶处覆盖的金属层厚度较薄,在电路工作过程中易由于热集中而熔断[6]。图1中圆圈标识处即台阶处。

BP TEOS工艺为TEOS工艺的下一代工艺,具有回流特性,可通过加温增密的方式实现回流,减缓台阶处的陡直度,减少台阶对金属布线的影响,降低金属布线热集中情况,有助于产品质量提升。

3.7 金属布线厚度

根据GJB597A规定,顶层金属化层厚度至少为800nm,有钝化层保护的情况下最大电流密度为5×105A/cm2。两条工艺线采用的掺杂铝的成份和掺杂比例均相同,均匀性、致密性和附着性差异不大[7]。金属化层厚度降低后,各项条件均满足GJB要求。样管加工完成后,经测试,延迟时间无明显差异,两种工艺对比延迟时间差异不大。

4 实测评估与对比

1)PCM测试评估

两种工艺所采用的原材料接近、工艺类似,样管加工完成后测试考核差异不大。由表1中的对比参数可以看出,两个工艺平台的PCM设计值相似度极高。样品加工完成后,PCM测试结果均满足产品PCM设计要求。

表1PCM设计值对比

2)成品率评估

对所有晶圆片进行原片级测试,中测成品率达到85%,原工艺线加工产品的中测成品率平均为72%,晶圆厂转移后成品率明显提升。

3)电参数测试评估

取晶圆厂转移前后的两批电路,对电参数进行对比验证,各个电参数特性无明显差异,且都满足详细规范要求。

各参数对比验证结果见表2。

由表2数据可得出以下结论:

输出高电平(VOH)对比:

端口的输出电压越高,说明端口的高电平驱动能力越强。通过以上参数对比,更改后的输出高电平与更改前相差很小。

输出低电平(VOL)对比:

端口的输出电压越低,说明端口的低电平驱动能力越强。通过以上参数对比,更改后的输出低电平与更改前相差很小。

表2 晶圆厂转移前后电参数对比

输入漏电流(IIL)对比:

输入漏电流是端口在输入状态下的漏电流。输入漏电流越小,说明端口的输入状态越好。通过以上参数对比,更改后的输入漏电流与更改前基本没有变化。

输出三态漏电流(IOZ)对比:

输出三态漏电流是端口在输出三态状态下的漏电流。输出三态漏电流越小,说明端口的输出三态状态越好。通过以上参数对比,更改后的输出三态漏电流与更改前没有变化。

静态电源电流(IDDSB)对比:

静态电源电流是电路在静态条件下,电源端口的电流值[8]。静态电源电流越小,说明电路的静态功耗越小。通过以上参数对比,更改后的静态电源电流与更改前变化很小。

工作电源电流(IDD)对比:

工作电源电流是电路在动态条件下,电源端口的电流值。工作电源电流越小,说明电路的动态态功耗越小。通过以上参数对比,更改后的工作电源电流与更改前变化很小。

数据最小建立时间(TS)对比:

数据最小建立时间是触发器时钟信号上升沿到来以前,数据稳定不变的时间。通过以上参数对比,数据最小建立时间更改前后都通过了功能验证。

BYTE最大延迟时间(TD)对比:

BYTE最大延迟时间是A/D的高低选择,通过以上参数对比,更改后的BYTE最大延迟时间与更改前变化很小。

综合以上评估对比结论,晶圆厂转移前后产品测试数据对比无明显差异,各项指标均满足规范要求。晶圆厂转移不影响产品技术指标,并满足详细规范中的各项试验要求,对产品使用、质量无影响。

5 结束语

通过逐一对比4英寸3μm双层金属P阱硅栅CMOS工艺与 5英寸 2μm双层金属 P阱硅栅CMOS工艺,确定7处工艺差异。经由理论分析和实际测试验证,确认两种工艺的工艺参数差异不大,晶圆厂转移后,产品各项指标均满足规范要求,且不影响原有用户使用,此结论可为类似产品的转移提供参考。