功率VDMOS器件高温直流应力下退化及失效机理研究

2019-04-11陈旭华

石 磊,陈旭华

(1.上海第二工业大学 工程训练中心,上海201209;2.安阳市环境监测中心站,安阳455000)

0 引言

垂直双扩散金属氧化物半导体(VDMOS)是一种重要的功率半导体器件,具有独特的垂直导电双扩散结构。对比传统的双极型晶体管,其具有低驱动功率、高输入阻抗、高开关速度、高线性跨导等优点,并且没有双极型晶体管的二次击穿现象[1-5]。VDMOS问世以来即在各种大功率应用场合发挥重要作用,特别是在汽车、高铁、航空、航天等重要领域有着不可或缺的作用。VDMOS的失效和退化是关乎设备和人员安全的重要问题,特别是其常处于大功率、高环境温度等严酷工作环境下,这对其可靠性提出了更高的要求。

国内外主要研究VDMOS功率器件在温度应力、电应力、机械应力下的退化失效过程和机理。单尼娜等[6]研究了直流和脉冲状态下功率VDMOS器件的可靠性,得出了两种状态下失效敏感参数为跨导。Davidovic等[7]研究了器件在持续辐照和负偏压温度应力下的变化,表明辐照和负偏压应力施加顺序的不同带来的不同影响。Wang等[8]研究了器件芯片漏极被外加薄膜施加应力情况下的变化,得出随着应力提高其开态电阻随之下降的结论。谭稀等[9]研究了器件漏电流、热阻(RTH)与软焊料空洞率关系,结果表明漏电流、RTH随空洞率增长而变大。本文研究了器件在高温应力、直流应力共同作用下的退化过程,对多项电学参数进行了较为全面的测量,并进行了RTH测量和微区分析,综合多种手段分析其退化和失效机理。

1 实验方案

待测功率VDMOS样品器件3支,采用国内自主封装的HRM7433D,分别为1、2、3号管。为得到器件在加速条件下的敏感参数退化规律,将器件置于高温环境对其施加功率,进行性能加速退化实验,电应力条件设置漏源电压(UDS)为5 V,漏源电流(IDS)为2 A,温度应力条件为230℃。

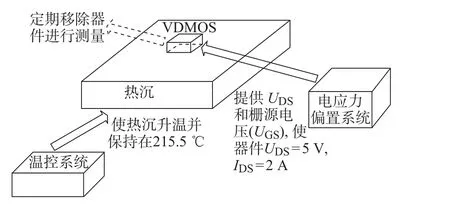

实验系统主要由温度控制系统和电应力偏置系统两大部分组成,图1为实验装置整体结构示意图。将其固定于热沉平台上,对器件施加压力。利用电热板、温控器、周波数调功模块、PT100传感器等设备搭建了温控系统,使热沉温度保持215.5℃,根据预先测出的器件RTH值,可计算出器件结温和热沉平台温差约为14.5℃,因此器件结温保持在230℃左右。

图1 实验装置整体结构示意图Fig.1 Schematic diagram of the experimental equipments

电应力偏置系统由栅压电路、漏源电压电流监测模块、电源组成。调节电源电压,使得UDS=5 V,栅压电路提供可调节栅源电压(UGS),调节UGS大小使IDS保持2 A。

实验中对多项参数进行测试,施加应力一段时间后,将其从实验平台取下置于通风处自然冷却1 h以上,使其和室温20℃保持一致,而后进行测量。测量后再将器件重新置于实验平台,对其恢复施加电学和温度应力。最初96 h应力阶段,每施加24 h应力进行一次测量。之后将测量间隔延长,改为每96 h应力进行一次测量。在第1 152 h测试点后,3号管在实验中突然失效,因此测量数据截止到1 152 h。

2 测量结果与讨论

2.1 电学参数退化

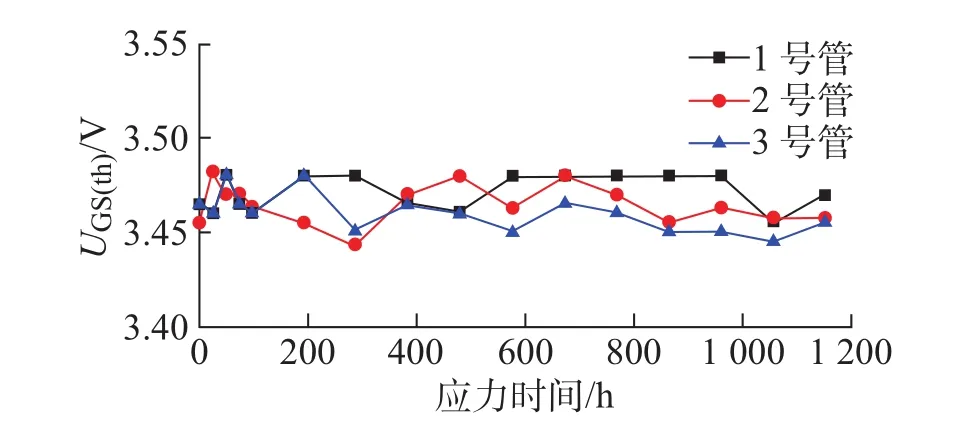

图2所示为测量得到的栅极阈值电压[UGS(th)]和应力时间的关系,保持UDS=UGS,UGS(th)为IDS=250µA时的UGS值。由图可知,随着应力时间增长,1、2、3号管的UGS(th)基本没有变化。通常金属-氧化物-半导体(MOS)场效应晶体管的栅极是薄弱环节,持续应力作用下容易失效和退化,影响器件的栅极控制能力[10],导致UGS(th)产生漂移。图2中UGS(th)的稳定表明其栅控能力没有变化。

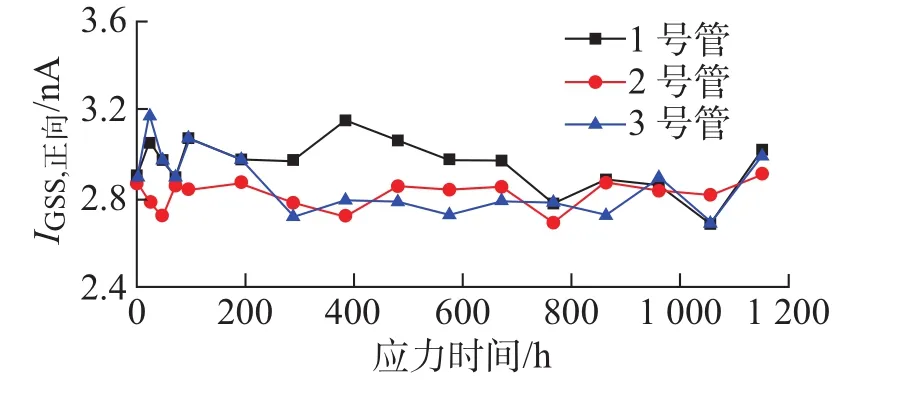

图3所示为施加正向偏压下的栅极-源极漏电流(IGSS)和应力时间关系图,偏压条件为UGS=20 V。当栅极退化时,其典型特征之一为栅源漏电流的增大,相比UGS(th)反映器件三端特性而言,IGSS为器件两端特性,不受器件漏端影响[11],更准确直接地反应栅极的变化。图3中IGSS保持稳定,和图2相吻合,说明器件栅极保持稳定。

图2 UGS(th)和应力时间关系(UDS=UGS,IDS=250µA)Fig.2 Relationship between UGS(th)and stress time(UDS=UGS,IDS=250µA)

图3 正向IGSS和应力时间关系(UGS=20 V)Fig.3 Relation between forward IGSSand stress time(UGS=20 V)

为更充分地研究器件栅极的变化情况,对器件在反向偏压下的IGSS也进行了测量,偏压条件为VGS=-20 V,图4表明其反向偏压下的漏电流同样基本保持不变。鉴于栅氧化层和漏电流的高度相关性[12],图3、4可以进一步精确表明器件栅氧化层保持稳定。

图4 反向IGSS和应力时间关系(UGS=-20 V)Fig.4 Relation between reverse IGSSand stress time(UGS=-20 V)

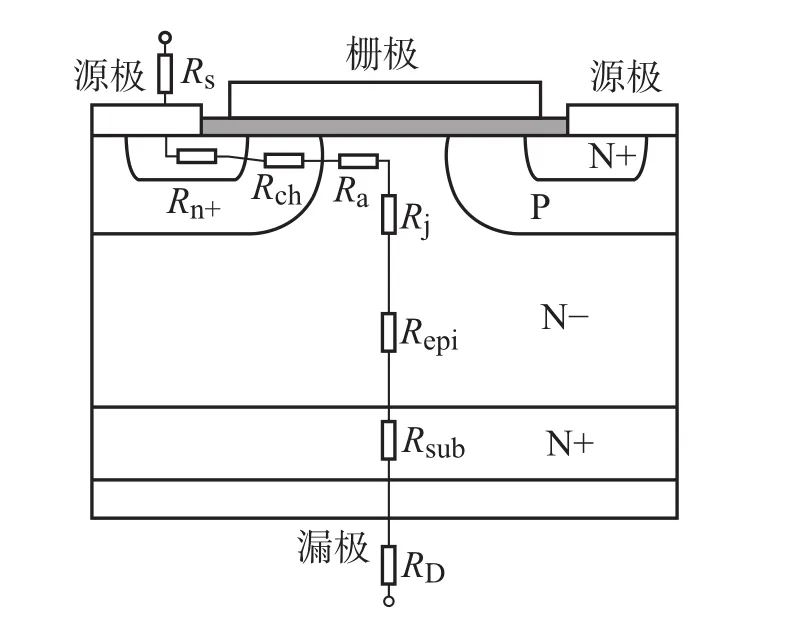

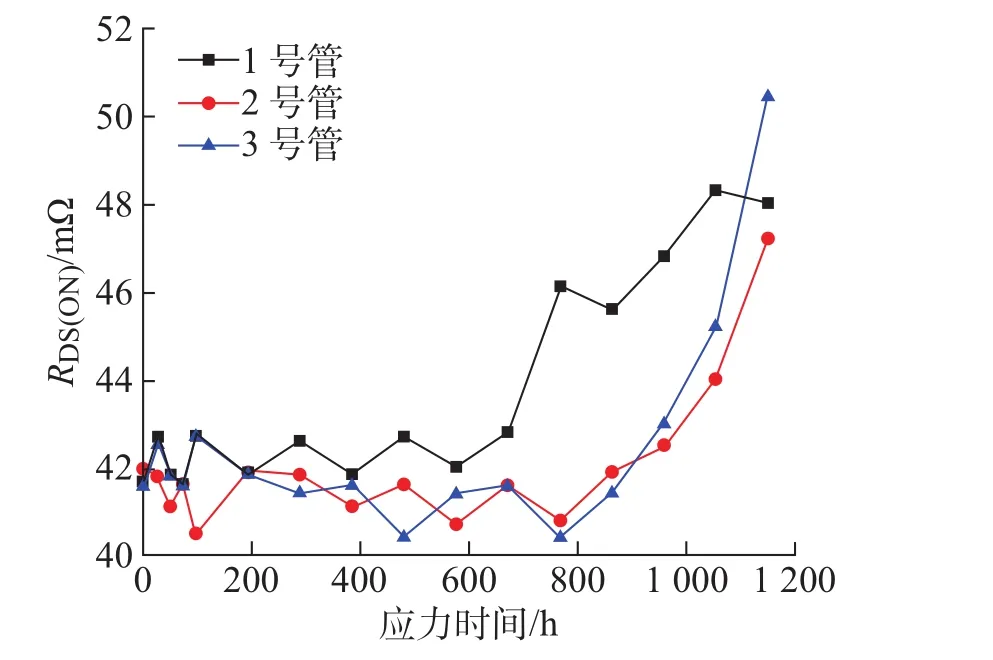

根据功率VDMOS器件的结构原理,其静态漏极-源极通态电阻RDS(on)包括:源极接触及封装电阻RS、源区电阻Rn+、沟道电阻Rch、积累层电阻Ra、JFET区电阻Rj、N-层电阻Repi、衬底电阻Rsub、漏极接触及封装电阻RD,各部分电阻分布如图5所示[13-14]。其中源极电阻RS为器件半导体结构之外的源极相关部分引入的电阻,由含引线在内的源极封装电阻Rcas(S)和源极欧姆接触电阻Rcont(S)两部分组成,即RS=Rcas(S)+Rcont(S)。类似地,漏极电阻RD由含引线在内的漏极封装电阻Rcas(D)和漏极欧姆接触电阻Rcont(D)两部分组成。图6所示为器件的RDS(on)随应力时间变化关系,测量设置UGS=10 V,IDS=28 A。在起初672 h内RDS(on)均保持稳定,而在672~864 h内,各个器件RDS(on)陆续开始出现上升趋势并保持至测量结束,值得注意的是3号管上升较快。但RDS(on)的增长源于器件电阻分布中哪一部分的变化仍需深入分析。

图5 RDS(on)分布示意图Fig.5 Diagram of the distribution of RDS(on)

图6 RDS(on)和应力时间关系(UGS=10 V,IDS=28 A)Fig.6 Relation between RDS(on)and stress time(VGS=10 V,IDS=28 A)

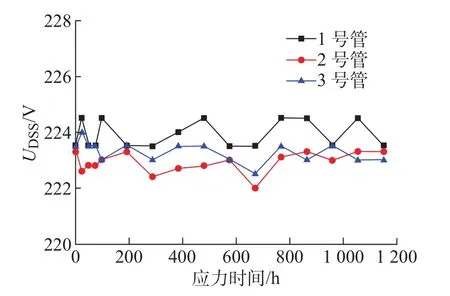

图7所示为漏极-源极击穿电压(UDSS)的退化情况,UDSS即UGS=0 V,IDS=1 mA时的UDS值,其值整体趋势保持不变。UDSS主要取决于外延层厚度、掺杂浓度等因素,特别是取决于外延层中漂移区的情况。但作为一个整体而言,UDSS也受器件其他部分影响,虽然其不是主要因素。从漏电流传输路径来看,从漏极开始,自下而上依次经过衬底N+区、外延层N-区、P区、源区N+区,最终从源极引线流出。随着应力时间延长,UDSS总体不变,测量结果表明,该电流路径上器件各部分状态没有变化。结合之前图2~4对于栅极的分析结果,可判断器件内部各部分在应力作用下均没有发生变化。

图7 UDSS和应力时间关系(UGS=0 V,IDS=1 mA)Fig.7 Relation between UDSSand stress time(UGS=0 V,IDS=1 mA)

图7得到的结果意味着图6中RDS(on)的变化与器件内部无关。因此RDS(on)的变化应来自于器件半导体结构以外的欧姆接触以及包含引线在内的封装结构的变化,即源于RS或RD的增大。正常情况下Rch、Ra、JFET区电阻Rj、N-层电阻Repi占据RDS(on)绝大部分。RD很小,近似可忽略;RS稍大,但相对于RDS(on)而言所占比例仍较小[13-14]。如果是RS或RD导致RDS(on)的显著增大必然是有异常情况发生。

2.2 微区分析

3号管失效后,对其进行了局部微区分析,得到封装开帽后器件表面扫描电镜图片,如图8所示。

图8 器件损坏局部区域扫描电镜图片Fig.8 The SEM image of damaged area of the device

可以看到源极引线已断裂,即图中箭头所指位置,且源极所在的表层呈现明显热损坏迹象。引线断裂处没有锋锐的断面,断面无规则但各处较圆润,且断裂后相接近的两端大体形状为圆头,图像表明应是高温下引线熔断导致,和器件表层图像的起泡鼓起相吻合。源极位置的高温是由于源极封装或源极欧姆接触的退化导致RS升高,而RS升高导致源极部位温度升高,温度升高又促进RS升高。在应力期间,该热电反馈作用发生,导致器件损坏。这一分析和图6中漏源通态电阻的变化情况相符合,各器件RDS(on)普遍都有增大,而损坏的3号管尤为明显。其源极相关部位退化情况最为严重,当RS升高,RDS(on)大于某一临界值时,灾难性的热电反馈最终导致器件烧毁。

2.3 热阻测试

在每个测量点,除电学特性测量之外,本研究对器件的RTH进行了测量。

根据JEDEC标准No.51-1,半导体器件RTH定义为:

式中:TJ为器件温度达到稳态后的结温;TR为参考点温度;PH为器件的电功率即热功率;TJ-TR为参考点与结的温度之差,也就是工作时的结温升ΔT。ΔT/PH就可以得到参考点和结之间的RTH,RTH定义为结对参考点。

本研究采用了电学法测量RTH。其测量原理是,半导体器件的结温和电学参数之间具有对应关系,如PN结、肖特基结的温度和固定电流下的结电压降呈线性关系,此类电学参数称为温敏参数。使用电学仪器测得温敏参数的变化,即可得到器件的温度变化[15]。

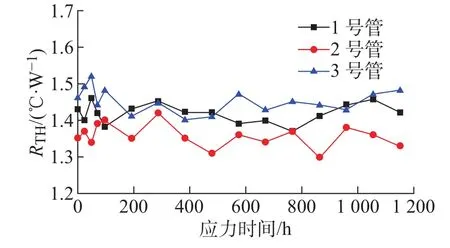

测量RTH时,首先测量被测VDMOS器件寄生二极管PN结电压和温度的线性关系,得到温度系数曲线。而后将其放置于保持恒温的热沉(参考点)上,利用特制夹具将器件固定并给以恒定向下压力。对器件施加功率使其升温,进入稳态后断开功率,采集小测试电流下PN结电压变化情况,结合温度系数曲线得到其温度,进而计算出其结到热沉之间RTH。施加功率仍采用UDS=5 V,IDS=2 A。图9为不同应力时间后结到热沉的RTH测量结果,可以看到除少许测量值自然偏差引起的抖动外,RTH值基本保持不变。

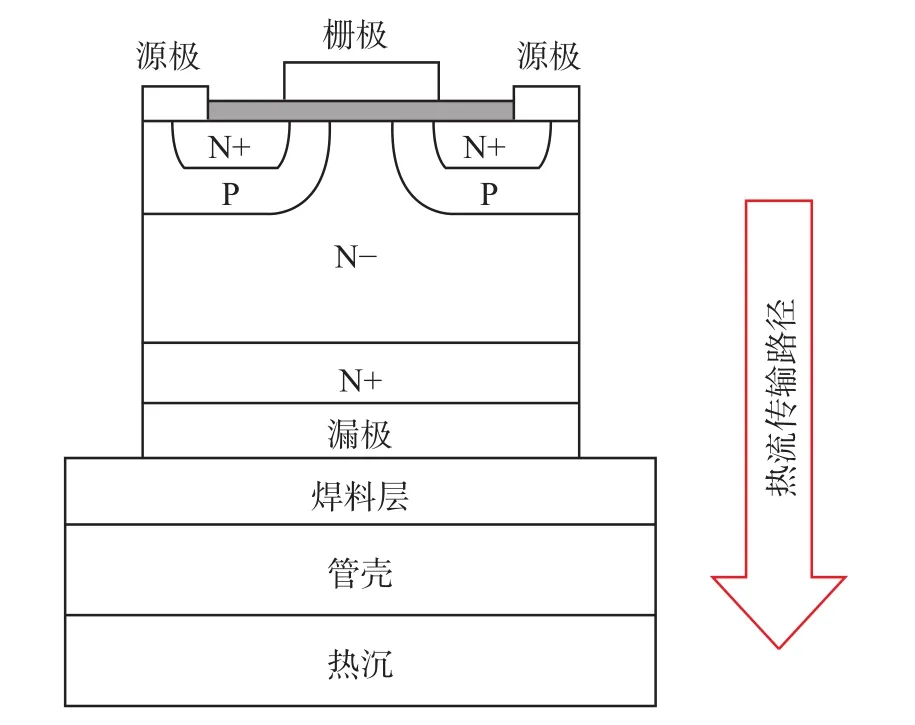

考虑到器件采用TO-254AA国产军工级封装,源极区域向上为绝热性能良好的惰性气体,因此施加功率后主要热流传输路径如图10所示,器件内部升温后,热量由上往下传递至漏极,经焊料层、管壳,传递至最下端的热沉,所测得RTH为该传输路径上的RTH。在传输路径上,器件内部、漏极和焊料层结合处、焊料层、焊料层和管壳结合处、管壳到热沉这些环节的任一变化都将导致RTH值的改变。如果器件内部产生诸如孔洞裂纹或者漏极到焊料层之间结合情况变化,RTH会相应发生变化。图9所示测量结果证明了器件内部没有结构变化,并且漏极到焊料层结合情况保持稳定。此外,焊料层空洞是功率VDMOS器件常见的问题之一,对器件性能特别是RTH构成直接影响[9],RTH测量结果表明了焊料层保持稳定,其空洞情况没有恶化,并且焊料层和管壳结合情况没有变化。管壳到热沉的压力在测试期间保持恒定。

图9 结到热沉的RTH和应力时间关系Fig.9 Relation between the junction-to-sink RTHand stress time

图10 热流传输路径示意图Fig.10 Diagram of heat transfer path

由于RTH保持稳定,在传输路径上的漏极承受的是相对稳定的温度应力,而源极区域在器件表层,向上没有有效传热途径,一旦RS发生变化容易因热量堆积造成温度过高,2.2节中微区分析结果和此相吻合。

3 结 语

本文研究了功率VDMOS器件施加高温直流应力后的退化和失效情况,持续测量了其多项电学参数变化,并进行了RTH测量。研究表明,其UGS(th)、IGSS、UDSS、器件 RTH均保持稳定,表现出较高的可靠性,说明高温直流应力对器件的栅极、漏极、器件内部结构、焊料层、管壳影响均很小。与此同时,RDS(on)随应力作用时间增大而增大。对损坏器件进行微区分析,结合器件RTH变化情况,表明RDS(on)的增大是由于源极封装或欧姆接触部分退化导致RS增大所致,其直接诱发的源极区域高温是器件损坏的原因。在此基础上,今后工作可进一步分析源极封装和欧姆接触各自的退化情况。从提高器件工作可靠性的角度而言,在工艺中设法增加欧姆接触电导率、增加源极引线直径都可以有效降低RS,更好地避免热电反馈的产生。此外,如果能增加器件源极向上方的传热能力,也有助于避免源极部分的损坏。