FPGA的多路串口数据快速采集与传输系统设计*

2019-01-17,

,

(北京工业大学 应用数理学院,北京 100124)

引 言

目前多路串口数据采集与传输对于工业控制现场多个设备串口的工作状态进行现场监控有很大帮助[1],其硬件实现简单,各路串口不存在互相干扰,出现问题易于排查,硬件成本低。然而一般微控制器芯片串口资源有限,很难满足现实需求,如果为了扩展更多的串口资源采用多路串口芯片,但每个芯片容纳的通道数不超过4个[2],这样在工业控制中会大大提高成本。

但是FPGA解决了上述所有问题。由于FPGA引脚多,容易实现单片机串口I/O有限的问题,同时可以方便连接多个外设[3-4]。而且FPGA内部程序是并行运行的,可以同时处理不同任务,这就导致FPGA工作更有效率[5]。因此本文利用FPGA这些特点,设计了适用于多串口装置在低速、小数据量通信条件,以FPGA为核心电路来控制各通道数据采集,同时采用RS232总线实现在高波特率下,将各路串口数据完整地上传到上位机,完成上位机与FPGA控制模块之间的数据传输。

1 总体设计方案

基于FPGA多通道串口数据采集与传输系统的设计,在硬件层面上,本系统利用单输入通道数字式智能仪表与压力传感器连接,将物体压力模拟量转换为数字量发送给FPGA。同时,通过对整体实现8路压力传感器数据采集与传输所占用的存储资源以及逻辑资源进行了初步评估之后,选择采用Cyclone IV系列 EP4CE6E22C8型号FPGA,因为该型号具有30个M9K存储模块,足够用来缓存8路并行数据传输,不会使数据因存储空间不够而出现数据堆叠的现象。

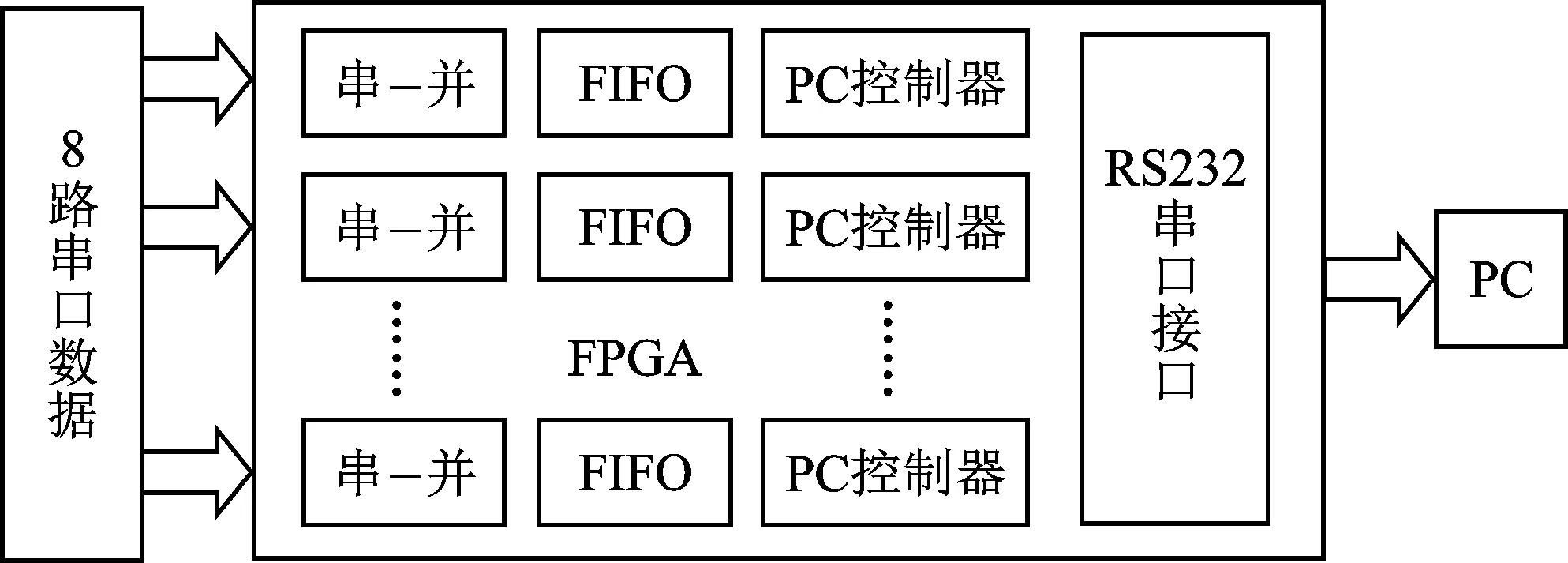

在软件层面上,本系统包括多通道数据采集模块(串转并模块、FIFO数据缓存模块、PC控制器模块)以及RS232串口接口输出模块两大部分,其系统整体构架图如图1所示。8路并行的RS232数据为输入数据,通过8个串转并模块将串行数据转为并行数据保存到8个独立FIFO中。利用FPGA中的同步有限状态机,在RS232串口接口模块建模与设计,将8路数据以查询方式上传到PC机上,对数据进行分析。

图1 多路串口快速数据采集与传输系统框架图

2 FPGA功能设计模块

2.1 多通道数据采集模块

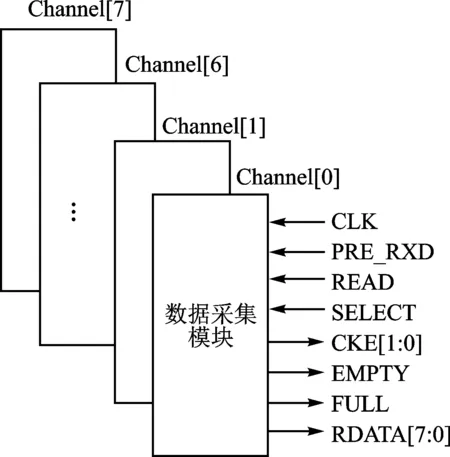

由于FPGA属于并行逻辑结构,各个串口通信模块可以同时进行数据收发而不会互相影响[6],因此系统设计了8路压力传感器数据同时接收,并将其数据保存到各自的FIFO中。系统设计了一路串口模块实现数据的采集与保存,通过在FPGA内部复用功能模块方式[7],利用硬件描述语言Verilog中generate for进行复制,设计出8路串口数据采集模块,如图2所示。其中CLK为系统同步时钟,PRE_RXD是经接口电平转换后FPGA能够采样的串口接收信号,将此数据打包为字节保存到FIFO中,当一帧数据写完或者读完之后,会有FULL或者EMPTY状态来表示各路串口FIFO状态,同时RS232串口接口模块会通过对FIFO的状态进行查询,当FULL[7:0]信号不为0时,给出一个SELECT信号,代表读取哪一路数据上传到PC机上。

图2 8路数据采集模块

利用Modelsim仿真软件测试此系统多通道数据采集模块,其仿真结果如图3所示。其中通过在测试文件中模拟8路压力传感器通道数据,同时输入一串十六进制数据为fa e0 5f 00 01 32 0a,通过观察各通道写入到FIFO中的数据wdata与输入数据一致,说明此系统能够实现多通道数据同时采集,验证了此模块设计的正确性。

图3 8路FIFO写数据

2.2 RS232串口接口模块

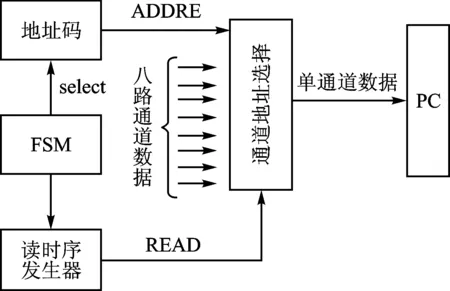

RS232串口接口模块是此系统最主要的部分,该部分利用数字逻辑中的有限状态机(FSM)将8路串口数据通过查询方式不断输出给PC机[8],其FSM与数据采集模块结构框图如图4所示。

图4 FSM与数据采集模块结构框图

状态机在状态转移过程中不断查询各路FIFO状态,选择总线地址码用来表示读取第几路FIFO数据,同时产生读数据控制时序,读取此路FIFO数据,通过RS232串口通信将该路FIFO中数据发送给PC机,并且每路数据在发送之前,都会把此帧数据的地址放到帧头前,代表第几路数据发送给上位机。

此模块利用状态机对8个通道数据进行循环查询来发送每个通道数据,状态机状态位说明如表1所列。

表1 状态机状态位说明

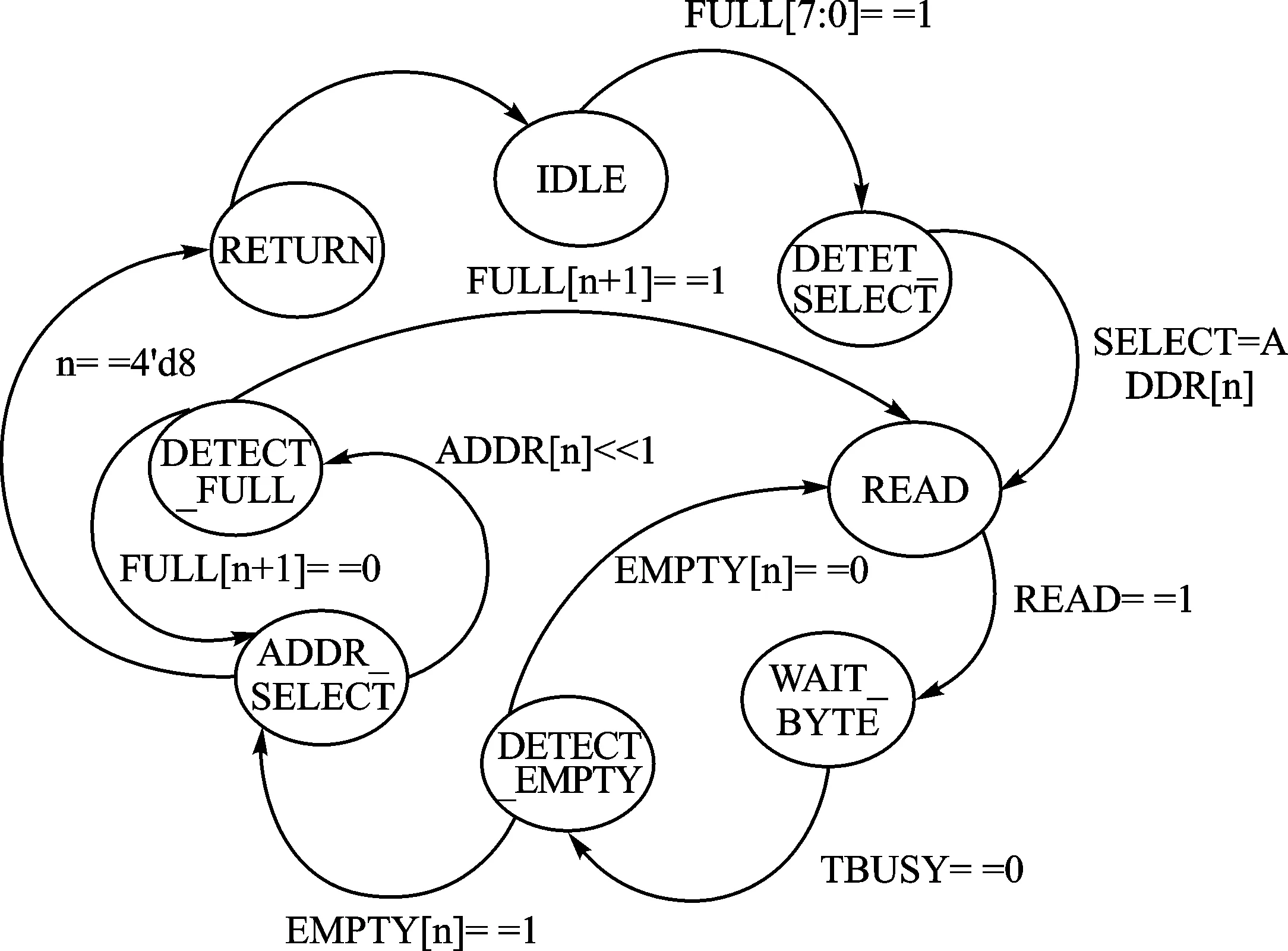

图5为状态机转移图,状态机的具体逻辑为:先检查各通道数据储存FIFO是否为满,如果有满状态,进入状态1,然后从第一通道开始判断哪路数据为满状态,将此通道数据地址输出给SELECT,选择第n路数据输出,进入状态2,将读信号标志READ置为1,开始读取第n通道FIFO,进入状态3,将READ信号置为0,等待一个字节发送完成给上位机,当PC发送数据时,TBUSY信号为1,字节发送完成之后,TBUSY信号为0,此时进入状态4,检查第n路中一帧数据是否读完,如果EMPTY[n]信号为1,代表此路数据读完,进入到状态5,否则返回到状态3。如果进入到状态5,则将通道地址左移一位,如果地址n=8,则进入到状态7,结束一次循环,否则进入状态6,检查第(n+1)路FIFO满状态FULL[n+1],如果为1,进入状态2,否则进入状态7,返回到初始状态。通过上述状态转移,最终8路数据传输完成。

图5 RS232串口接口FSM状态转移图

3 资源配置与优化

在软件设计时,为了节省FPGA芯片内部资源消耗,便于将此系统移植到更多需要此功能的工业生产设计中,同时减少工业成本输出,可以选择一些低成本FPGA芯片,在软件设计时进行了资源优化设计。

首先,FIFO缓冲模块主要实现对通信数据的缓存,提高各路串口传输速率,从而简单有效地完成各路串口数据缓存功能。但通常设计串口通信时,在每个串口模块前端,为发送和接收端分别配置一个FIFO模块[9-10],用于串口数据的缓存。然而本设计为了减少使用芯片存储资源,在设计FPGA功能时,采用了自己编写的FIFO缓冲器,在实际操作过程中使用更加灵活。由于压力传感器最长的一帧数据是300个字节长度,所以为每路设计一个FIFO缓冲模块,储存空间为600个字节。在串口发送末端没有设计FIFO缓冲器,直接从缓存的FIFO中读取数据,为系统节省了300×8字节空间。

其次,在设计各个通道串口波特率时,因为每个通道的串口接收传输速率是相同的,所以此系统在顶层模块中设计了一个各通道共用的波特率模块,以减少占用存储单元。

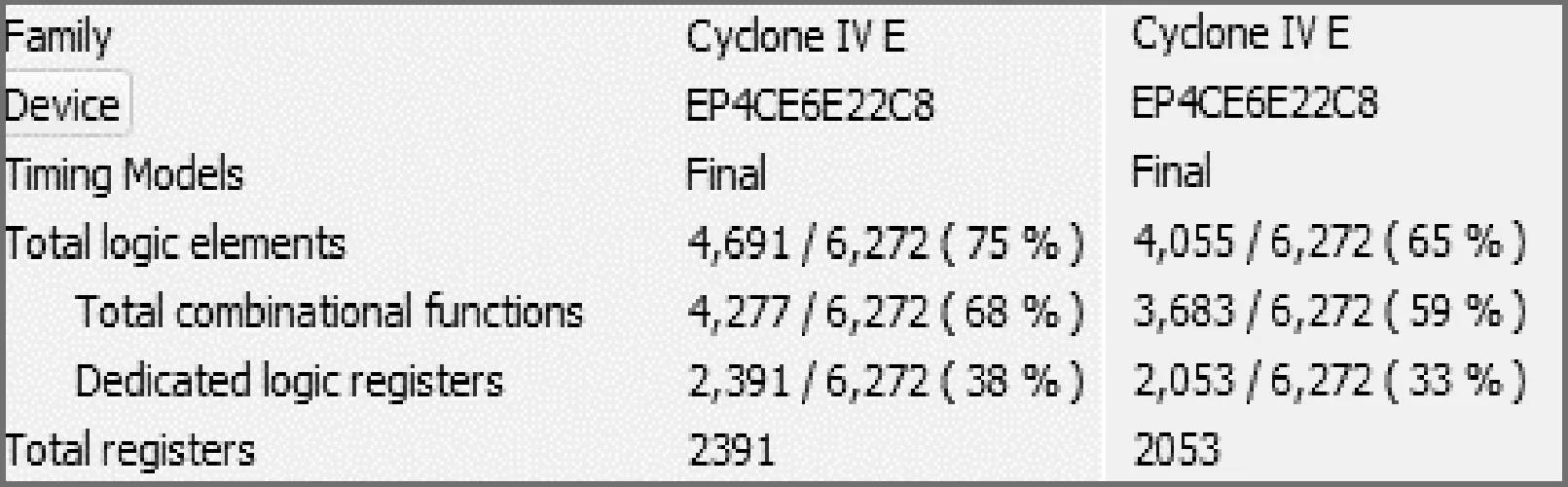

系统通过资源优化后,对优化前后FPGA代码进行编译后,优化前后编译报告资源对比如图6所示。通过对比发现,优化设计后,寄存器资源利用率比优化前减少了10%,说明资源配置实现了一定的优化效果。

图6 资源优化前和优化后的资源对比

4 验证与分析

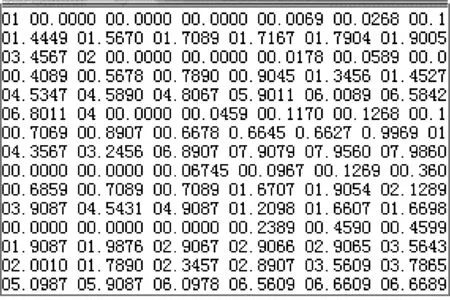

为了验证此系统的正确性,将8路压力传感器+FPGA+RS232串口通信的多路串口系统硬件平台搭建起来进行测验。此平台中,每路压力传感仪表数据传输速率为9 600 bps,当各路数据接收完成后,通过查询方式以256 000 bps发送速率发送每一帧数据,发送速率为每10 ms发送150字节,每帧数据帧头都是通道地址,代表此帧数据为哪路数据。此系统中通过数字仪表显示的数据与PC机上串口助手显示的数据进行对比,观察各路数据的正确性。经多次测试,此系统设计可以实现要求,并且数据完整不丢帧。图7所示为部分测试结果。

图7 各通道部分帧数据

结 语